一种阶梯栅沟槽肖特基势垒二极管器件的制备方法及器件与流程

本发明涉及半导体功率器件领域,尤其涉及一种阶梯栅沟槽肖特基势垒二极管器件的制备方法及器件。

背景技术:

1、肖特基势垒二极管(schottky barrier diode,sbd)是一种快恢复二极管,它属一种低功耗、大电流、超高速半导体器件。肖特基势垒二极管并非是利用p型半导体与n型半导体接触形成pn结,而是利用金属与半导体接触形成的金属-半导体结,其显著的特点为反向恢复时间极短(可以小到几纳秒),正向导通压降仅0.4v左右。肖特基势垒二极管多用作高频、低压、大电流整流二极管、续流二极管、保护二极管,也有用在微波通信等电路中作整流二极管、小信号检波二极管使用,常用在彩电的二次电源整流、高频电源整流中。

2、由于肖特基势垒二极管中不存在pn结二极管的pn结耗尽,其无法有效抑制反向耐压时的漏电流。现有的肖特基一般漏电范围在20~30ua,导致其反偏功耗较大,耐压和漏电流是肖特基二极管上升到一定电压程度面临的主要难题之一。

技术实现思路

1、为了解决以上技术问题,本发明提供了一种阶梯栅沟槽肖特基势垒二极管器件的制备方法及器件。

2、本发明所解决的技术问题可以采用以下技术方案实现:

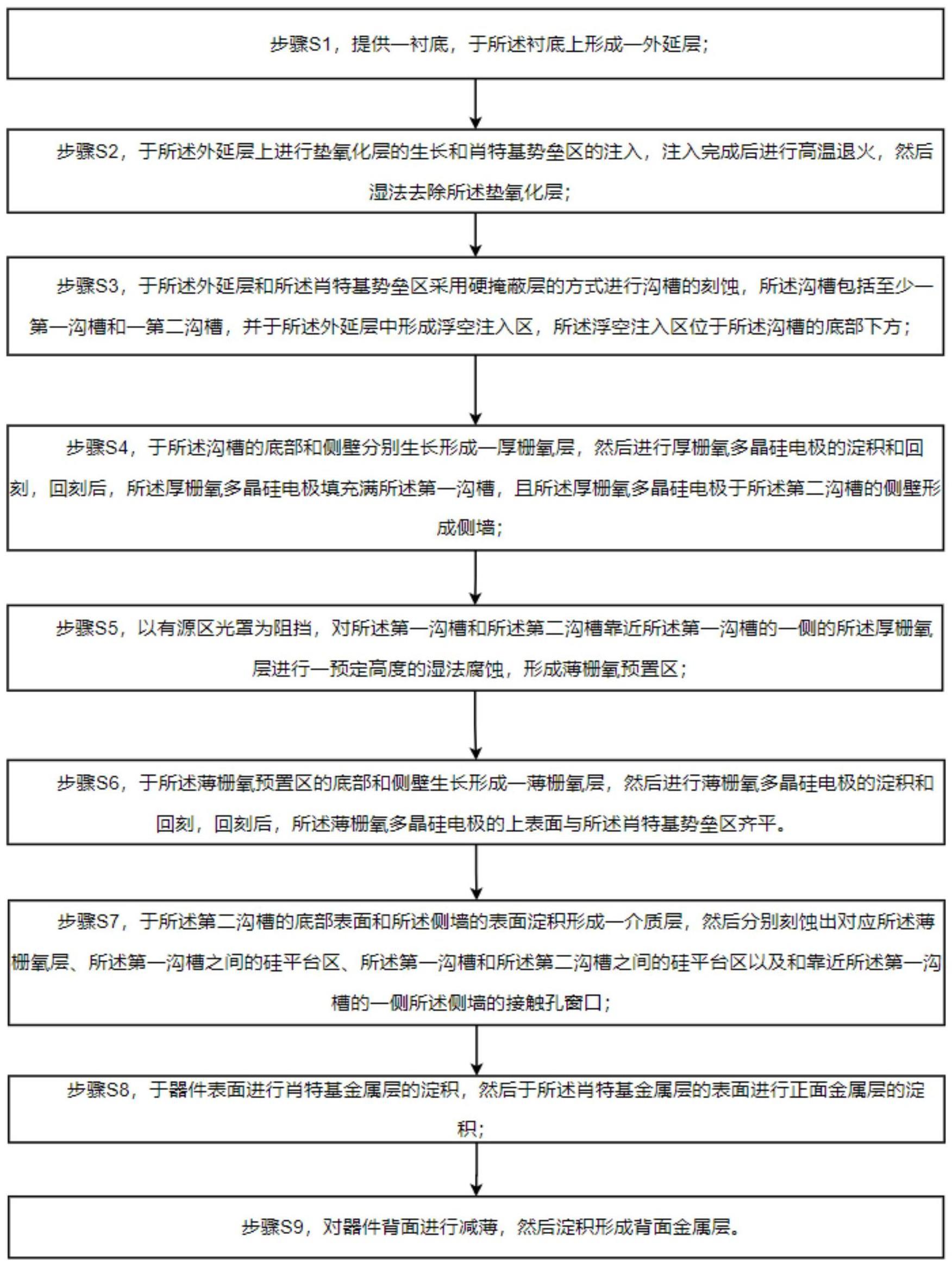

3、一种阶梯栅沟槽肖特基势垒二极管器件的制备方法,包括:

4、步骤s1,提供一衬底,于所述衬底上形成一外延层;

5、步骤s2,于所述外延层上进行垫氧化层的生长和肖特基势垒区的注入,注入完成后进行高温退火,然后湿法去除所述垫氧化层;

6、步骤s3,于所述外延层和所述肖特基势垒区采用硬掩蔽层的方式进行沟槽的刻蚀,所述沟槽包括至少一第一沟槽和一第二沟槽,并于所述外延层中形成浮空注入区,所述浮空注入区位于所述沟槽的底部下方;

7、步骤s4,于所述沟槽的底部和侧壁分别生长形成一厚栅氧层,然后进行厚栅氧多晶硅电极的淀积和回刻,回刻后,所述厚栅氧多晶硅电极填充满所述第一沟槽,且所述厚栅氧多晶硅电极于所述第二沟槽的侧壁形成侧墙;

8、步骤s5,以有源区光罩为阻挡,对所述第一沟槽和所述第二沟槽靠近所述第一沟槽的一侧的所述厚栅氧层进行一预定高度的湿法腐蚀,形成薄栅氧预置区;

9、步骤s6,于所述薄栅氧预置区的底部和侧壁生长形成一薄栅氧层,然后进行薄栅氧多晶硅电极的淀积和回刻,回刻后,所述薄栅氧多晶硅电极的上表面与所述肖特基势垒区齐平。

10、优选地,所述步骤s6之后,还包括:

11、步骤s7,于所述第二沟槽的底部表面和所述侧墙的表面淀积形成一介质层,然后分别刻蚀出对应所述薄栅氧层、所述第一沟槽之间的硅平台区、所述第一沟槽和所述第二沟槽之间的硅平台区以及靠近所述第一沟槽的一侧所述侧墙的接触孔窗口;

12、步骤s8,于器件表面进行肖特基金属层的淀积,然后于所述肖特基金属层的表面进行正面金属层的淀积;

13、步骤s9,对器件背面进行减薄,然后淀积形成背面金属层。

14、优选地,所述步骤s8中,所述肖特基金属层和所述正面金属层覆盖自所述第二沟槽的部分底部区域至器件靠近所述第一沟槽的一侧边缘。

15、优选地,所述步骤s2中,所述肖特基势垒区的注入杂质为b,注入能量为100kev~200kev。

16、优选地,所述步骤s3具体包括:

17、步骤s31,于所述肖特基势垒区上淀积形成硬掩蔽层;

18、步骤s32,对所述硬掩蔽层进行光刻、刻蚀,将沟槽图形转移到所述硬掩蔽层上;

19、步骤s33,以所述硬掩蔽层为阻挡,干法刻蚀形成所述至少一第一沟槽和所述第二沟槽;

20、步骤s34,以所述硬掩蔽层为阻挡,于所述沟槽的底部注入形成浮空注入区;

21、步骤s35,湿法腐蚀去除所述硬掩蔽层。

22、优选地,所述浮空注入区的注入杂质为b,注入能量为100kev~300kev,注入剂量为1e12~1e13每平方厘米。

23、优选地,所述第二沟槽的宽度大于第一沟槽的宽度。

24、优选地,所述步骤s6中,所述薄栅氧层的生长厚度为300~1000a,生长温度为900~100c。

25、优选地,所述肖特基金属层的材质为钛钴锰。

26、本发明还提供一种阶梯栅沟槽肖特基势垒二极管器件,应用如上述的阶梯栅沟槽肖特基势垒二极管器件的制备方法制备得到,包括:

27、外延层,形成于一衬底上表面;

28、肖特基势垒区,形成于所述外延层上;

29、沟槽,包括至少一第一沟槽和一第二沟槽,形成于所述外延层和所述肖特基势垒区中;

30、浮空注入区,位于所述沟槽的底部下方;

31、厚栅氧层,生长于所述沟槽的底部和侧壁;

32、厚栅氧多晶硅电极,填充满所述第一沟槽,且所述厚栅氧多晶硅电极于所述第二沟槽的侧壁形成侧墙;

33、薄栅氧层,生长于薄栅氧预置区的底部和侧壁,所述薄栅氧预置区由所述第一沟槽和所述第二沟槽靠近所述第一沟槽的一侧的所述厚栅氧层进行一预定高度的湿法腐蚀后形成;

34、薄栅氧多晶硅电极,填充于所述薄栅氧预置区,所述薄栅氧多晶硅电极的上表面与所述肖特基势垒区齐平。

35、本发明技术方案的优点或有益效果在于:

36、本发明通过设置肖特基势垒区,实现肖特基势垒和表面电场的调节,从而抑制反向漏电;通过设置沟槽的上部区域的薄栅氧层,以增强肖特基势垒二极管上部分区域的横向电场,进一步抑制肖特基反向漏电,并保障其耐压性能;通过在沟槽底部下方区域设置浮空注入区,以延伸沟槽底部的电场分布范围,形成另一个截止反向漏电的保护锁,同时提高器件耐压能力。

技术特征:

1.一种阶梯栅沟槽肖特基势垒二极管器件的制备方法,其特征在于,包括:

2.根据权利要求1所述的阶梯栅沟槽肖特基势垒二极管器件的制备方法,其特征在于,所述步骤s6之后,还包括:

3.根据权利要求2所述的阶梯栅沟槽肖特基势垒二极管器件的制备方法,其特征在于,所述步骤s8中,所述肖特基金属层和所述正面金属层覆盖自所述第二沟槽的部分底部区域至器件靠近所述第一沟槽的一侧边缘。

4.根据权利要求1所述的阶梯栅沟槽肖特基势垒二极管器件的制备方法,其特征在于,所述步骤s2中,所述肖特基势垒区的注入杂质为b,注入能量为100kev~200kev。

5.根据权利要求1所述的阶梯栅沟槽肖特基势垒二极管器件的制备方法,其特征在于,所述步骤s3具体包括:

6.根据权利要求1所述的阶梯栅沟槽肖特基势垒二极管器件的制备方法,其特征在于,所述浮空注入区的注入杂质为b,注入能量为100kev~300kev,注入剂量为1e12~1e13每平方厘米。

7.根据权利要求1所述的阶梯栅沟槽肖特基势垒二极管器件的制备方法,其特征在于,所述第二沟槽的宽度大于第一沟槽的宽度。

8.根据权利要求1所述的阶梯栅沟槽肖特基势垒二极管器件的制备方法,其特征在于,所述步骤s6中,所述薄栅氧层的生长厚度为生长温度为900℃~1000℃。

9.根据权利要求2所述的阶梯栅沟槽肖特基势垒二极管器件的制备方法,其特征在于,所述肖特基金属层的材质为钛钴锰。

10.一种阶梯栅沟槽肖特基势垒二极管器件,其特征在于,应用如权利要求1-9任意一项所述的阶梯栅沟槽肖特基势垒二极管器件的制备方法制备得到,包括:

技术总结

本发明提供一种阶梯栅沟槽肖特基势垒二极管器件的制备方法及器件,包括:于衬底上形成外延层;进行垫氧化层的生长和肖特基势垒区的注入,去除垫氧化层;刻蚀沟槽,沟槽包括至少一第一沟槽和第二沟槽,并于外延层中形成浮空注入区;生长厚栅氧层,淀积、回刻厚栅氧多晶硅电极;以有源区光罩为阻挡,对厚栅氧层进行预定高度的湿法腐蚀,形成薄栅氧预置区;于薄栅氧预置区的底部和侧壁生长薄栅氧层,淀积、回刻薄栅氧多晶硅电极。有益效果:通过设置肖特基势垒区,调节肖特基势垒和表面电场,通过薄栅氧层的设置增强横向电场,抑制反向漏电;浮空注入区能够延伸电场分布范围,形成另一个截止反向漏电保护锁,提高器件耐压能力。

技术研发人员:刘厚超,黄宇萍,马一洁,张雨,苏亚兵,苏海伟

受保护的技术使用者:上海维安半导体有限公司

技术研发日:

技术公布日:2024/1/12

- 还没有人留言评论。精彩留言会获得点赞!