半导体装置及其制造方法与流程

本发明涉及半导体装置及其制造方法,例如涉及具有半导体芯片的半导体装置及其制造方法。

背景技术:

1、已知将半导体芯片面朝上(face up)安装于具有金属基底和设于该金属基底上的绝缘性框体的封装件中的金属基底上,使用接合线将绝缘性框体上的图案与半导体芯片电连接的半导体装置(例如专利文献1)。

2、现有技术文献

3、专利文献

4、专利文献1:日本特开2019-176149

5、在专利文献1的安装方法中,来自半导体芯片的热经由金属基底而散热,因此散热性高。然而,由于要将半导体芯片搭载于各个封装件,成本变高。

技术实现思路

1、本公开是鉴于上述问题而完成的,其目的在于提供能实现低成本化的半导体装置及其制造方法。

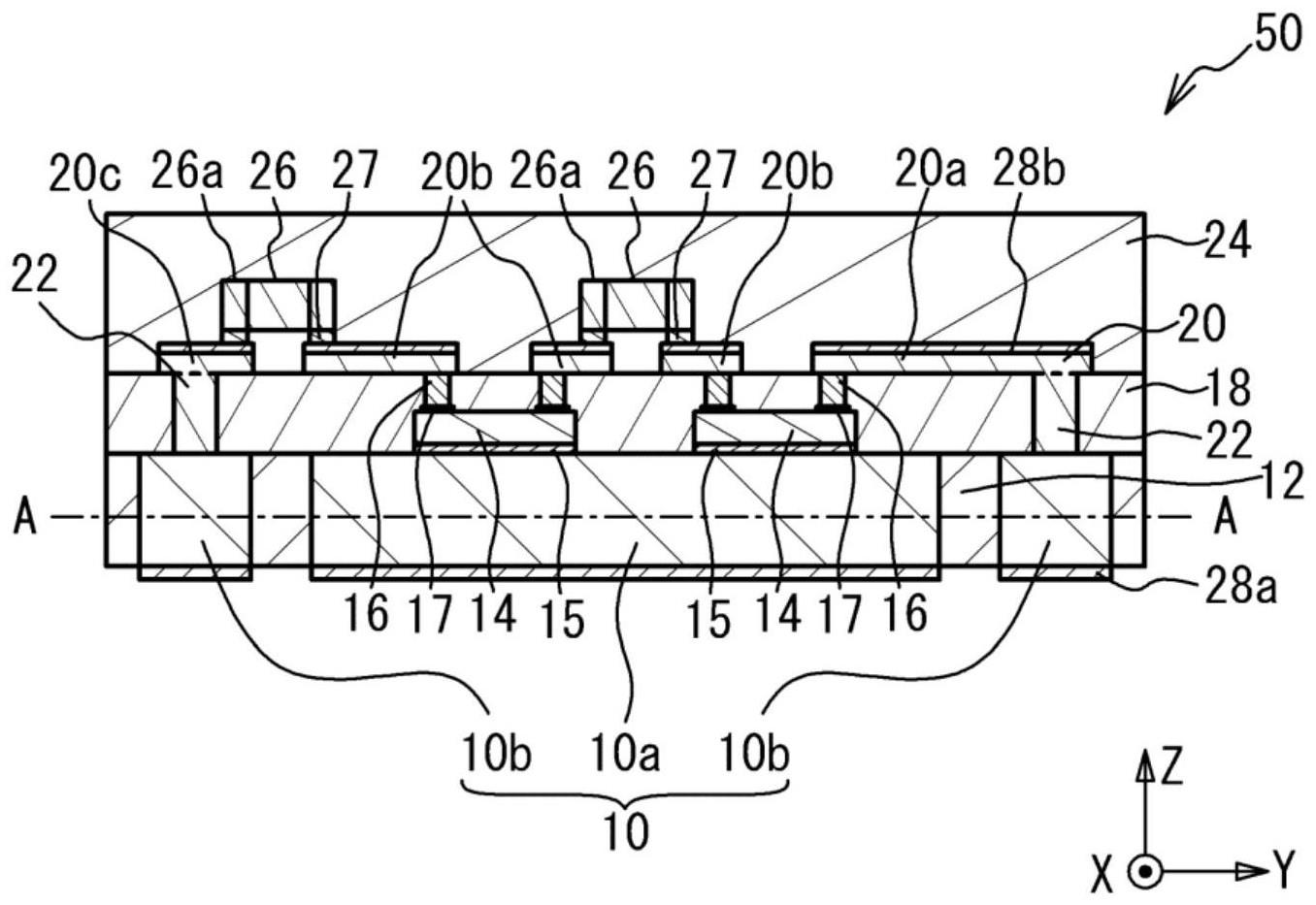

2、本公开的一个实施方式是半导体装置,具备:金属板,具备基底部和与所述基底部分离的端子部;树脂层,被设于所述基底部与所述端子部之间并且被设为在俯视方向上包围所述金属板,所述基底部和所述端子部各自的上表面和下表面在所述树脂层露出;半导体芯片,搭载于所述基底部上;第一绝缘层,以覆盖所述半导体芯片的方式被设于所述金属板和所述树脂层上;以及一个或多个布线,设于所述第一绝缘层上,至少一个布线将所述半导体芯片与所述端子部电连接。

3、本公开的一个实施方式是半导体装置的制造方法,包括以下工序:在具备多个区域和连接部的引线框架中的基底部、端子部以及所述连接部之间形成树脂层,其中,所述多个区域具备在各个区域内彼此分离的所述基底部和所述端子部,所述连接部在所述多个区域中的邻接的区域中将一个区域内的所述基底部和所述端子部与另一个区域内的所述基底部和所述端子部连接;在所述多个区域内的所述基底部上分别搭载半导体芯片;以覆盖所述半导体芯片的方式在所述引线框架和所述树脂层上形成绝缘层;在所述绝缘层上形成将所述半导体芯片与所述端子部电连接的布线;以及在形成所述布线的工序后,通过对所述邻接的区域之间的所述连接部和所述树脂层进行切割,形成与所述多个区域对应的多个半导体装置。

4、发明效果

5、根据本公开,能提供能实现低成本化的半导体装置及其制造方法。

技术特征:

1.一种半导体装置,具备:

2.根据权利要求1所述的半导体装置,其中,

3.根据权利要求1或2所述的半导体装置,具备:

4.根据权利要求1至3中任一项所述的半导体装置,其中,

5.根据权利要求1至4中任一项所述的半导体装置,具备:

6.根据权利要求1至5中任一项所述的半导体装置,其中,

7.根据权利要求1至6中任一项所述的半导体装置,具备:

8.一种半导体装置的制造方法,包括以下工序:

技术总结

本发明提供能实现低成本化的半导体装置及其制造方法。半导体装置(50)具备:金属板(10),具备基底部(10a)和与所述基底部分离的端子部(10b);树脂层(12),被设于所述基底部与所述端子部之间并且被设为在俯视方向上包围所述金属板,所述基底部和所述端子部的上表面和下表面在所述树脂层露出;半导体芯片(14),搭载于所述基底部上;第一绝缘层(18),以覆盖所述半导体芯片的方式被设于所述金属板和所述树脂层上;以及一个或多个布线(20),设于所述第一绝缘层上,至少一个布线(20a)将所述半导体芯片与所述端子部电连接。

技术研发人员:森山豊,桥长达也

受保护的技术使用者:住友电气工业株式会社

技术研发日:

技术公布日:2024/1/15

- 还没有人留言评论。精彩留言会获得点赞!