悬梁结构的形成方法与流程

本申请涉及半导体集成电路制造,具体涉及一种悬梁结构的形成方法。

背景技术:

1、图像传感器中,互补金属氧化物半导体图像传感器(complementary metal oxidesemiconductor contact image sensor,cis)是采用cmos器件制作的图像传感器,由于其具有集成度高、供电电压低和技术门槛低等优势,广泛应用于摄影摄像、安防系统、智能便携电话以及医疗电子等领域。

2、cis的感光度与像素区(pixel)的尺寸大小强相关,传统的光电二极管(photodiode,pd)是通过光刻工艺和离子注入工艺形成,会受到光阻的深宽比以及离子注入的深度和浓度的限制。为了在小尺寸的像素上提高感光度,可纵向拓展pd的空间,以避开光阻深宽比的限制,鉴于此,相关技术中提出了在cis中形成悬梁结构,在形成深层的pd后,再形成表面的器件结构,可避开离子注入和光刻的工艺极限。

3、然而,由于悬梁结构具有高深宽比,因此在对其进行掺杂的外延层填充时,会有较高的几率使深沟槽的开口被提前封口,掺杂的外延层不能填充在整个深沟槽的表面,从而降低了器件的可靠性和良率。

技术实现思路

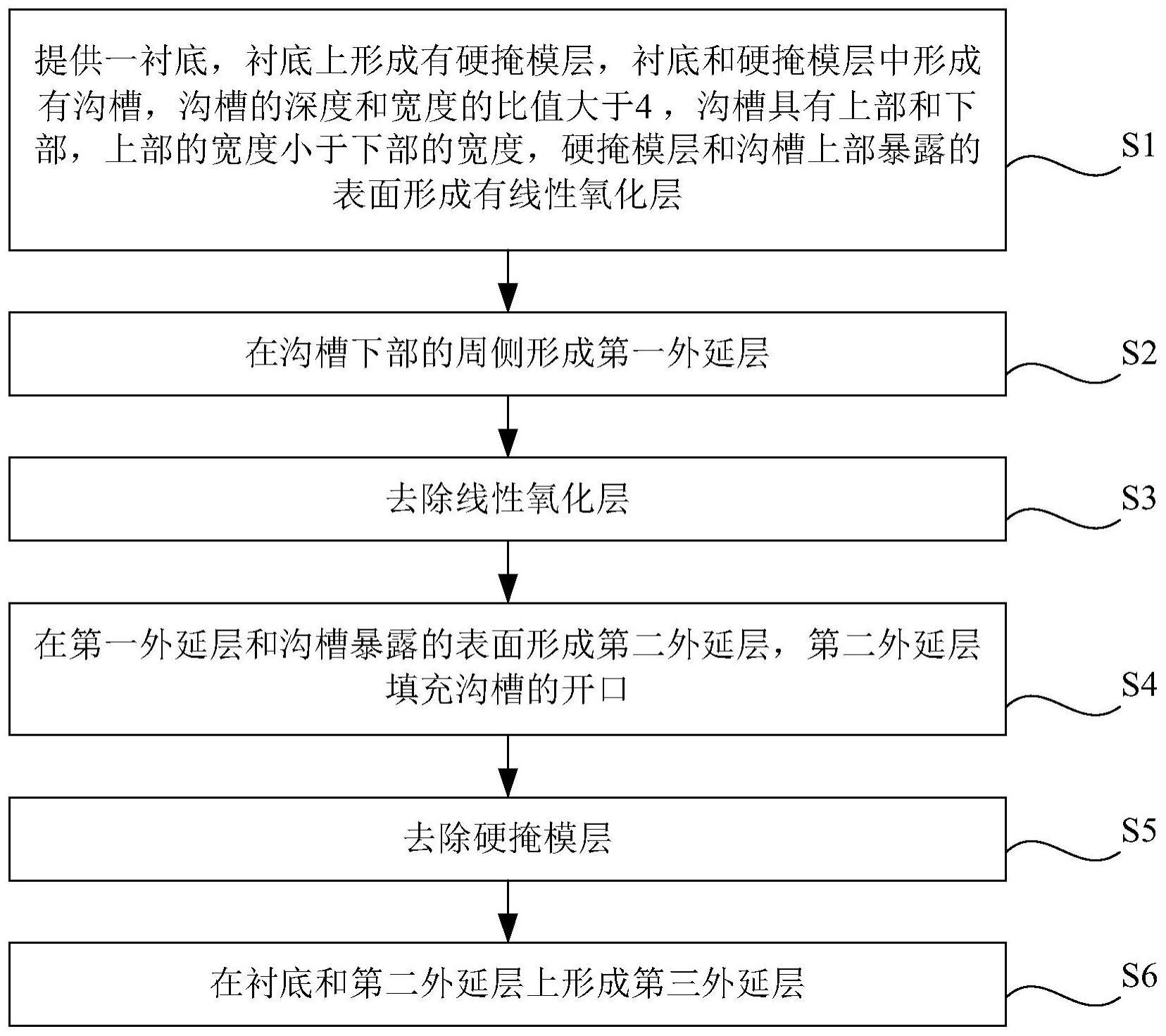

1、本申请提供了一种悬梁结构的形成方法,可以解决相关技术中提供的悬梁结构的形成方法在填充外延层时容易提前封口的问题,该方法包括:

2、提供一衬底,所述衬底上形成有硬掩模层,所述衬底和硬掩模层中形成有沟槽,所述沟槽的深度和宽度的比值大于4,所述沟槽具有上部和下部,所述上部的宽度小于所述下部的宽度,所述硬掩模层和所述沟槽上部暴露的表面形成有线性氧化层;

3、在所述沟槽下部的周侧形成第一外延层;

4、去除所述线性氧化层;

5、在所述第一外延层和所述沟槽暴露的表面形成第二外延层,所述第二外延层填充所述沟槽的开口;

6、去除所述硬掩模层;

7、在所述衬底和所述第二外延层上形成第三外延层。

8、在一些实施例中,所述衬底从下而上依次包括硅衬底和外延层,所述外延层中掺杂有第二类型的杂质。

9、在一些实施例中,所述硬掩模层包括氮化硅层。

10、在一些实施例中,所述第二外延层中掺杂有第一类型的杂质。

11、在一些实施例中,所述去除所述硬掩模层,包括:

12、进行第一次平坦化处理,使所述沟槽开口处的第二外延层的表面不突出;

13、去除所述硬掩模层;

14、进行第二次平坦化处理。

15、在一些实施例中,所述去除所述线性氧化层,包括:

16、通过湿法刻蚀工艺去除所述线性氧化层。

17、在一些实施例中,所述第一外延层的厚度为70纳米至200纳米。

18、本申请技术方案,至少包括如下优点:

19、通过先在深沟槽中形成第一外延层,然后形成第二外延层,最后形成第三外延层的方式形成深层的pd,能够改善生沟槽提前封口的问题,使掺杂的第二外延层填满整个深沟槽区域,改善了外延层的形貌,在一定程度上提高了器件的可靠性和良率。

技术特征:

1.一种悬梁结构的形成方法,其特征在于,所述方法应用于cis的制作工艺中,所述方法包括:

2.根据权利要求1所述的方法,其特征在于,所述衬底从下而上依次包括硅衬底和外延层,所述外延层中掺杂有第二类型的杂质。

3.根据权利要求2所述的方法,其特征在于,所述硬掩模层包括氮化硅层。

4.根据权利要求3所述的方法,其特征在于,所述第二外延层中掺杂有第一类型的杂质。

5.根据权利要求4所述的方法,其特征在于,所述去除所述硬掩模层,包括:

6.根据权利要求1至5任一所述的方法,其特征在于,所述去除所述线性氧化层,包括:

7.根据权利要求6所述的方法,其特征在于,所述第一外延层的厚度为70纳米至200纳米。

技术总结

本申请公开了一种悬梁结构的形成方法,该方法应用于CIS的制作工艺中,包括:提供一衬底,衬底上形成有硬掩模层,衬底和硬掩模层中形成有沟槽,沟槽的深度和宽度的比值大于4,沟槽具有上部和下部,上部的宽度小于下部的宽度,硬掩模层和沟槽上部暴露的表面形成有线性氧化层;在沟槽下部的周侧形成第一外延层;去除线性氧化层;在第一外延层和沟槽暴露的表面形成第二外延层,第二外延层填充沟槽的开口;去除硬掩模层;在衬底和第二外延层上形成第三外延层。本申请通过先在深沟槽中形成第一外延层,然后形成第二外延层,最后形成第三外延层的方式形成深层的PD,能够改善生沟槽提前封口的问题。

技术研发人员:郑晓辉,张栋,范晓,王函,陈广龙

受保护的技术使用者:华虹半导体(无锡)有限公司

技术研发日:

技术公布日:2024/1/12

- 还没有人留言评论。精彩留言会获得点赞!