一种屏蔽栅沟槽场效应晶体管及其制作方法与流程

本发明属于半导体,涉及一种屏蔽栅沟槽场效应晶体管及其制作方法。

背景技术:

1、屏蔽栅沟槽场效应晶体管(shielding gate trench mosfet,简称sgt-mosfet)作为一种先进的功率mosfet器件技术,通过引入屏蔽栅电极降低器件栅漏交叠面积,进而降低栅漏电容,达到提高开关速度,降低器件动态损耗的目的,提高了系统使用效率。

2、为了提高器件效率,sgt-mosfet的单元间距不断缩小,单元间距比例的缩小增加了mosfet的增益,使得器件在线性工作模式下更容易发生热失控,降低了器件的安全工作区(soa)性能,即降低了器件处理大电压大电流产生的高功耗的能力。

3、在负载开关和热插拔等应用场景下,选用mosfet需要考虑的其中一个重点便是器件的安全工作区(soa)性能。

4、如何提升sgt mosfet的soa性能,以增强其在各类应用场景下的适用性,成为本领域技术人员亟待解决的一个重要技术问题。

5、应该注意,上面对技术背景的介绍只是为了方便对本申请的技术方案进行清楚、完整的说明,并方便本领域技术人员的理解而阐述的。不能仅仅因为这些方案在本申请的背景技术部分进行了阐述而认为上述技术方案为本领域技术人员所公知。

技术实现思路

1、鉴于以上所述现有技术的缺点,本发明的目的在于提供一种屏蔽栅沟槽场效应晶体管及其制作方法,用于解决现有技术中屏蔽栅沟槽场效应晶体管的安全工作区性能有待提高的问题。

2、为实现上述目的及其他相关目的,本发明提供一种屏蔽栅沟槽场效应晶体管的制作方法,其特征在于,包括以下步骤:

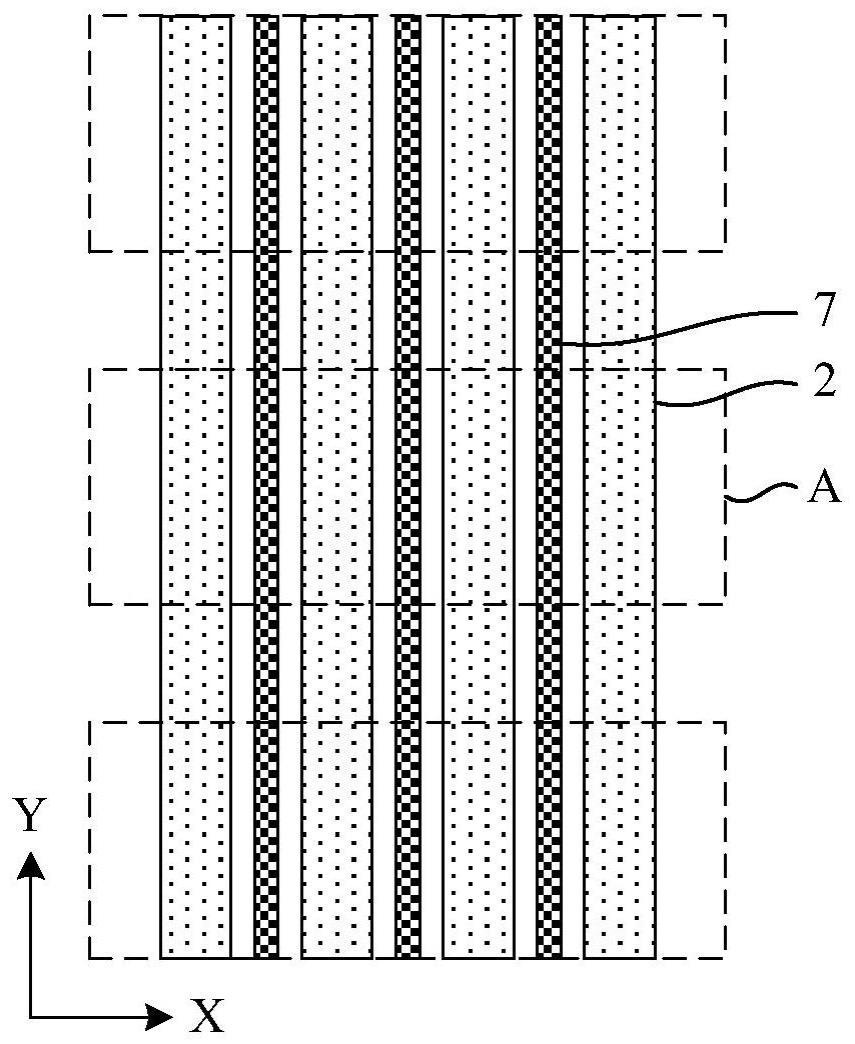

3、提供一半导体层,形成沿x方向间隔排列并往y方向延伸的多个元胞区沟槽于所述半导体层中,所述x方向与所述y方向均平行于所述半导体层所在平面并相互垂直;

4、形成沟槽栅结构于所述元胞区沟槽中;

5、形成体区于所述半导体层的上表层,所述体区分布于所述元胞区沟槽的两侧;

6、形成阻挡层于所述半导体层上方,并形成多个开口于所述阻挡层中以定义多个分立设置的离子注入区;

7、基于多个所述离子注入区对所述半导体层进行离子注入以形成源区于所述体区的上表层;

8、形成层间介质层于所述半导体层上方;

9、形成沿y方向延伸的接触槽于相邻两个所述元胞区沟槽之间,所述接触槽垂向贯穿所述层间介质层、所述源区并延伸至所述体区中;

10、形成电极层于所述层间介质层上方,所述电极层还填充进所述接触槽中。

11、可选地,多个所述离子注入区包括沿y方向间隔排列的多个x向延伸型离子注入区,所述x向延伸型离子注入区沿x方向跨越多个所述元胞区沟槽中的至少三个。

12、可选地,多个所述离子注入区包括沿x方向间隔排列的多个y向延伸型离子注入区,其中,多个所述元胞区沟槽两两一组,一组所述元胞区沟槽对应一条所述y向延伸型离子注入区,对于每组所述元胞区沟槽,所述y向延伸型离子注入区跨越两条所述元胞区沟槽,且在x方向上,所述y向延伸型离子注入区的两端不超过一组所述元胞区沟槽的两端。

13、可选地,所述y向延伸型离子注入区包括沿y方向间隔排列的多个子离子注入区。

14、可选地,所述沟槽栅结构包括下层多晶硅、上层多晶硅、隔离层、第一介质层及第二介质层,所述上层多晶硅位于所述下层多晶硅上方,所述隔离层位于所述下层多晶硅与所述上层多晶硅之间,所述第一介质层位于所述元胞区沟槽的内壁与所述下层多晶硅的外壁之间,所述第二介质层位于所述元胞区沟槽的内壁与所述上层多晶硅的外壁之间。

15、本发明还提供一种屏蔽栅沟槽场效应晶体管,包括:

16、半导体层;

17、多个元胞区沟槽,位于所述半导体层中,多个所述元胞区沟槽沿x方向间隔排列并往y方向延伸,所述x方向与所述y方向均平行于所述半导体层所在平面并相互垂直;

18、沟槽栅结构,位于所述元胞区沟槽中;

19、体区,位于所述半导体层的上表层并分布于所述元胞区沟槽的两侧;

20、源区,位于所述体区的上表层,其中,所述源区位于预先定义的多个离子注入区中,多个所述离子注入区分立设置;

21、层间介质层,位于所述半导体层上方;

22、接触槽,沿y方向延伸并位于相邻两个所述元胞区沟槽之间,所述接触槽垂向贯穿所述层间介质层、所述源区并延伸至所述体区中;

23、电极层,位于所述层间介质层上方,所述电极层还填充进所述接触槽中。

24、可选地,多个所述离子注入区包括沿y方向间隔排列的多个x向延伸型离子注入区,所述x向延伸型离子注入区沿x方向跨越多个所述元胞区沟槽中的至少三个。

25、可选地,多个所述离子注入区包括沿x方向间隔排列的多个y向延伸型离子注入区,其中,多个所述元胞区沟槽两两一组,一组所述元胞区沟槽对应一条所述y向延伸型离子注入区,对于每组所述元胞区沟槽,所述y向延伸型离子注入区跨越两条所述元胞区沟槽,且在x方向上,所述y向延伸型离子注入区的两端不超过一组所述元胞区沟槽的两端。

26、可选地,所述y向延伸型离子注入区包括沿y方向间隔排列的多个子离子注入区。

27、可选地,所述沟槽栅结构包括下层多晶硅、上层多晶硅、隔离层、第一介质层及第二介质层,所述上层多晶硅位于所述下层多晶硅上方,所述隔离层位于所述下层多晶硅与所述上层多晶硅之间,所述第一介质层位于所述元胞区沟槽的内壁与所述下层多晶硅的外壁之间,所述第二介质层位于所述元胞区沟槽的内壁与所述上层多晶硅的外壁之间。

28、如上所述,本发明的屏蔽栅沟槽场效应晶体管的制作方法中,在通过离子注入形成源区时定义了多个分立设置的离子注入区,通过这种方式,器件元胞区没有进行源区离子注入的区域无法形成能够提供电子的源区,即器件在工作时此区域不产生电流,能够有效降低器件的电流密度,同时器件不产生电流的区域也能够改善器件整体的散热能力,最终提升了器件的安全工作区性能。

技术特征:

1.一种屏蔽栅沟槽场效应晶体管的制作方法,其特征在于,包括以下步骤:

2.根据权利要求1所述的屏蔽栅沟槽场效应晶体管的制作方法,其特征在于:多个所述离子注入区包括沿y方向间隔排列的多个x向延伸型离子注入区,所述x向延伸型离子注入区沿x方向跨越多个所述元胞区沟槽中的至少三个。

3.根据权利要求1所述的屏蔽栅沟槽场效应晶体管的制作方法,其特征在于:多个所述离子注入区包括沿x方向间隔排列的多个y向延伸型离子注入区,其中,多个所述元胞区沟槽两两一组,一组所述元胞区沟槽对应一条所述y向延伸型离子注入区,对于每组所述元胞区沟槽,所述y向延伸型离子注入区跨越两条所述元胞区沟槽,且在x方向上,所述y向延伸型离子注入区的两端不超过一组所述元胞区沟槽的两端。

4.根据权利要求3所述的屏蔽栅沟槽场效应晶体管的制作方法,其特征在于:所述y向延伸型离子注入区包括沿y方向间隔排列的多个子离子注入区。

5.根据权利要求1所述的屏蔽栅沟槽场效应晶体管的制作方法,其特征在于:所述沟槽栅结构包括下层多晶硅、上层多晶硅、隔离层、第一介质层及第二介质层,所述上层多晶硅位于所述下层多晶硅上方,所述隔离层位于所述下层多晶硅与所述上层多晶硅之间,所述第一介质层位于所述元胞区沟槽的内壁与所述下层多晶硅的外壁之间,所述第二介质层位于所述元胞区沟槽的内壁与所述上层多晶硅的外壁之间。

6.一种屏蔽栅沟槽场效应晶体管,其特征在于,包括:

7.根据权利要求6所述的屏蔽栅沟槽场效应晶体管,其特征在于:多个所述离子注入区包括沿y方向间隔排列的多个x向延伸型离子注入区,所述x向延伸型离子注入区沿x方向跨越多个所述元胞区沟槽中的至少三个。

8.根据权利要求6所述的屏蔽栅沟槽场效应晶体管,其特征在于:多个所述离子注入区包括沿x方向间隔排列的多个y向延伸型离子注入区,其中,多个所述元胞区沟槽两两一组,一组所述元胞区沟槽对应一条所述y向延伸型离子注入区,对于每组所述元胞区沟槽,所述y向延伸型离子注入区跨越两条所述元胞区沟槽,且在x方向上,所述y向延伸型离子注入区的两端不超过一组所述元胞区沟槽的两端。

9.根据权利要求8所述的屏蔽栅沟槽场效应晶体管,其特征在于:所述y向延伸型离子注入区包括沿y方向间隔排列的多个子离子注入区。

10.根据权利要求6所述的屏蔽栅沟槽场效应晶体管,其特征在于:所述沟槽栅结构包括下层多晶硅、上层多晶硅、隔离层、第一介质层及第二介质层,所述上层多晶硅位于所述下层多晶硅上方,所述隔离层位于所述下层多晶硅与所述上层多晶硅之间,所述第一介质层位于所述元胞区沟槽的内壁与所述下层多晶硅的外壁之间,所述第二介质层位于所述元胞区沟槽的内壁与所述上层多晶硅的外壁之间。

技术总结

本发明提供一种屏蔽栅沟槽场效应晶体管及其制作方法,该制作方法包括以下步骤:形成沿X方向间隔排列并往Y方向延伸的多个元胞区沟槽于半导体层中;形成沟槽栅结构于元胞区沟槽中;形成体区于半导体层的上表层;形成阻挡层于半导体层上方,并形成多个开口于阻挡层中以定义多个分立设置的离子注入区;基于多个离子注入区对半导体层进行离子注入以形成源区于体区的上表层;形成层间介质层;形成接触槽;形成电极层。本发明在通过离子注入形成源区时定义了多个分立设置的离子注入区,通过这种方式,器件元胞区没有进行源区离子注入的区域无法形成能够提供电子的源区,从而能够降低器件的电流密度,改善器件的散热能力,提升器件的安全工作区性能。

技术研发人员:陈开宇,胡磊

受保护的技术使用者:瑶芯微电子科技(上海)有限公司

技术研发日:

技术公布日:2024/1/12

- 还没有人留言评论。精彩留言会获得点赞!