半导体器件及其制造方法与流程

本发明涉及半导体集成电路制造领域,特别涉及一种半导体器件及其制造方法。

背景技术:

1、目前通常采用应力记忆技术(smt,stress memorization technology)来提升nmos器件的电子迁移率和pmos器件的空穴迁移率。以提升nmos器件的电子迁移率为例,其步骤包括:在侧墙和源漏离子注入工艺完成之后,在nmos器件区和pmos器件区上沉积高张应力的氮化硅层,并通过高温退火工艺将张应力传递给nmos器件的源漏和栅极而提升nmos器件的电子迁移率,最后再去除氮化硅层。但是,氮化硅层中的张应力也会传递至pmos器件的源漏和栅极,会降低pmos器件的空穴迁移率,从而影响pmos器件的性能。

2、其中,为了使得更多的张应力传递至nmos器件区中而进一步提升nmos器件的电子迁移率,会沉积更厚的氮化硅层;但同时会导致更厚的氮化硅层中的张应力传递至pmos器件区,从而影响pmos器件的性能。因此,为了提升nmos器件的性能的同时还能避免降低pmos器件的性能,在沉积更厚的氮化硅层之后且在高温退火工艺之前,额外增加一道光刻和刻蚀工艺,以去除pmos器件区上的氮化硅层,仅保留nmos器件区上的氮化硅层。但是,这种方法会额外增加一道光刻和刻蚀工艺,进而导致增加芯片制造成本。

3、因此,如何在提升nmos器件和pmos器件中的其中一个器件的性能且避免降低另一器件的性能的同时,还能避免增加芯片制造成本是亟需解决的问题。

技术实现思路

1、本发明的目的在于提供一种半导体器件及其制造方法,使得在提升nmos器件和pmos器件中的其中一个器件的性能且避免降低另一器件的性能的同时,还能避免增加芯片制造成本。

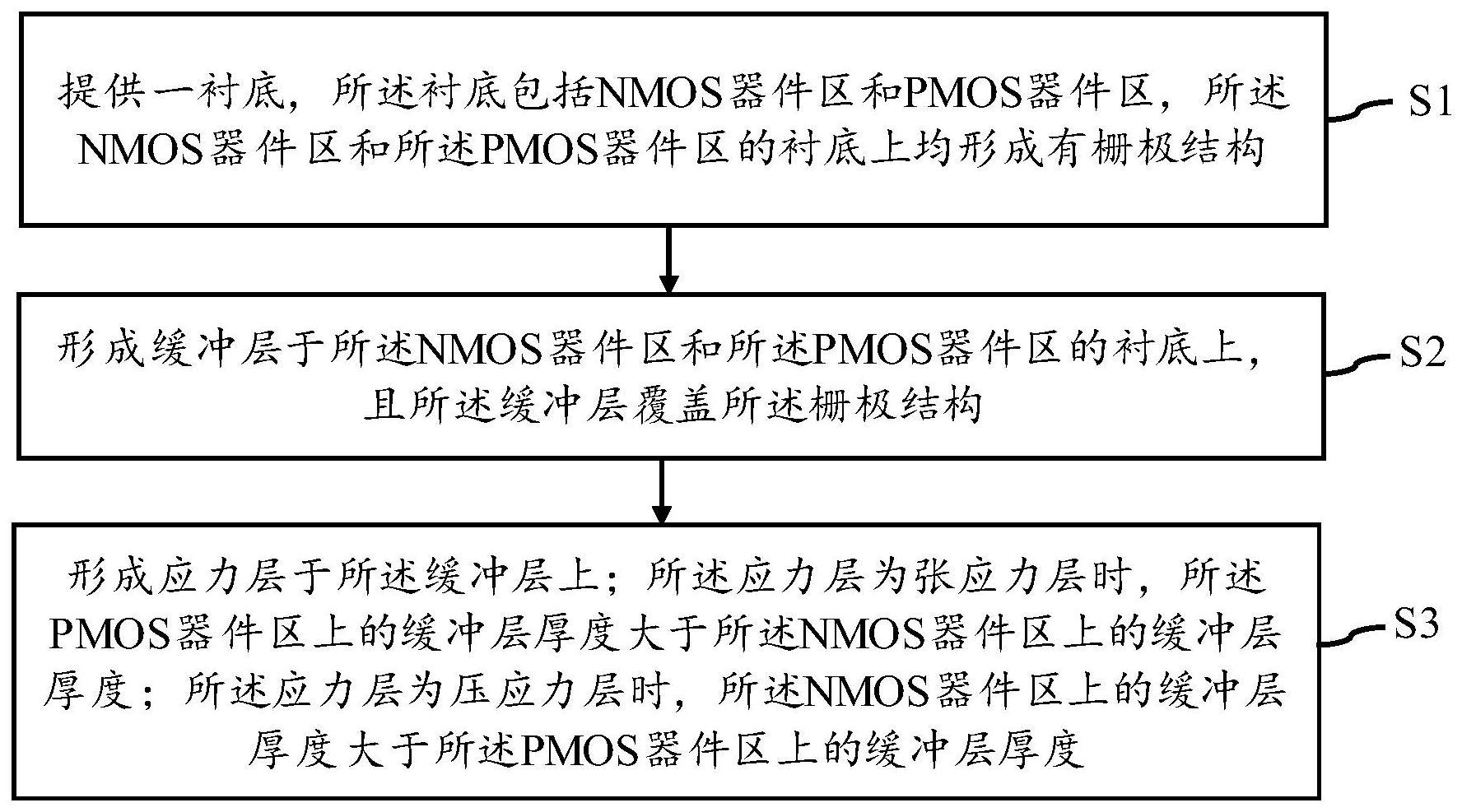

2、为实现上述目的,本发明提供了一种半导体器件的制造方法,包括:

3、提供一衬底,所述衬底包括nmos器件区和pmos器件区,所述nmos器件区和所述pmos器件区的衬底上均形成有栅极结构;

4、形成缓冲层于所述nmos器件区和所述pmos器件区的衬底上,且所述缓冲层覆盖所述栅极结构;

5、形成应力层于所述缓冲层上;所述应力层为张应力层时,所述pmos器件区上的缓冲层厚度大于所述nmos器件区上的缓冲层厚度;所述应力层为压应力层时,所述nmos器件区上的缓冲层厚度大于所述pmos器件区上的缓冲层厚度。

6、可选地,所述应力层为张应力层时,在形成所述应力层于所述缓冲层上之前,所述半导体器件的制造方法还包括:

7、形成第一源极区和第一漏极区于所述nmos器件区的所述栅极结构两侧的衬底中,形成所述第一源极区和所述第一漏极区与形成所述缓冲层采用同一图案化的光刻胶层为掩膜;

8、所述应力层为压应力层时,在形成所述应力层于所述缓冲层上之前,所述半导体器件的制造方法还包括:

9、形成第二源极区和第二漏极区于所述pmos器件区的所述栅极结构两侧的衬底中,形成所述第二源极区和所述第二漏极区与形成所述缓冲层采用同一图案化的光刻胶层为掩膜。

10、可选地,所述应力层为张应力层时;

11、形成所述缓冲层于所述nmos器件区和所述pmos器件区的衬底上的步骤包括:

12、形成第一缓冲层于所述nmos器件区和所述pmos器件区的衬底上,且所述第一缓冲层覆盖所述栅极结构;

13、去除所述nmos器件区上的第一缓冲层;

14、形成第二缓冲层于所述nmos器件区的所述衬底和所述栅极结构上以及所述pmos器件区的第一缓冲层上;

15、或者,形成所述缓冲层于所述nmos器件区和所述pmos器件区的衬底上的步骤包括:

16、形成缓冲层于所述nmos器件区和所述pmos器件区的衬底上,且所述缓冲层覆盖所述栅极结构;

17、去除所述nmos器件区上的部分厚度的所述缓冲层。

18、可选地,在去除所述nmos器件区上的第一缓冲层之前或之后,或者,在去除所述nmos器件区上的部分厚度的所述缓冲层之前或之后,所述半导体器件的制造方法还包括:

19、形成第一源极区和第一漏极区于所述nmos器件区的所述栅极结构两侧的衬底中,其中,形成所述第一源极区和所述第一漏极区与去除所述nmos器件区上的第一缓冲层或者去除所述nmos器件区上的部分厚度的所述缓冲层采用同一图案化的光刻胶层为掩膜。

20、可选地,在去除所述nmos器件区上的第一缓冲层之后或者在去除所述nmos器件区上的部分厚度的所述缓冲层之后,所述半导体器件的制造方法还包括:

21、形成第二源极区和第二漏极区于所述pmos器件区的所述栅极结构两侧的衬底中。

22、可选地,所述应力层为压应力层时;

23、形成所述缓冲层于所述nmos器件区和所述pmos器件区的衬底上的步骤包括:

24、形成第一缓冲层于所述nmos器件区和所述pmos器件区的衬底上,且所述第一缓冲层覆盖所述栅极结构;

25、去除所述pmos器件区上的第一缓冲层;

26、形成第二缓冲层于所述pmos器件区的所述衬底和所述栅极结构上以及所述nmos器件区的第一缓冲层上;

27、或者,形成所述缓冲层于所述nmos器件区和所述pmos器件区的衬底上的步骤包括:

28、形成缓冲层于所述nmos器件区和所述pmos器件区的衬底上,且所述缓冲层覆盖所述栅极结构;

29、去除所述pmos器件区上的部分厚度的所述缓冲层。

30、可选地,在去除所述pmos器件区上的第一缓冲层之前或之后,或者,在去除所述pmos器件区上的部分厚度的所述缓冲层之前或之后,所述半导体器件的制造方法还包括:

31、形成第二源极区和第二漏极区于所述pmos器件区的所述栅极结构两侧的衬底中,其中,形成所述第二源极区和所述第二漏极区与去除所述pmos器件区上的第一缓冲层或者去除所述pmos器件区上的部分厚度的所述缓冲层采用同一图案化的光刻胶层为掩膜。

32、可选地,在去除所述pmos器件区上的第一缓冲层之后或者在去除所述pmos器件区上的部分厚度的所述缓冲层之后,所述半导体器件的制造方法还包括:

33、形成第一源极区和第一漏极区于所述nmos器件区的所述栅极结构两侧的衬底中。

34、可选地,所述半导体器件的制造方法还包括:

35、执行退火工艺;

36、去除所述应力层。

37、本发明还提供一种半导体器件,包括:

38、衬底,所述衬底包括nmos器件区和pmos器件区,所述nmos器件区和所述pmos器件区的衬底上均形成有栅极结构;

39、缓冲层,形成于所述nmos器件区和所述pmos器件区的衬底上,且所述缓冲层覆盖所述栅极结构;

40、应力层,形成于所述缓冲层上;所述应力层为张应力层时,所述pmos器件区上的缓冲层厚度大于所述nmos器件区上的缓冲层厚度;所述应力层为压应力层时,所述nmos器件区上的缓冲层厚度大于所述pmos器件区上的缓冲层厚度。

41、可选地,所述应力层的材质包括氮化硅,所述缓冲层的材质包括氧化硅。

42、可选地,所述半导体器件还包括:

43、第一源极区和第一漏极区,形成于所述nmos器件区的所述栅极结构两侧的衬底中;

44、第二源极区和第二漏极区,形成于所述pmos器件区的所述栅极结构两侧的衬底中。

45、可选地,所述nmos器件区的衬底中形成有p阱,所述第一源极区和所述第一漏极区形成于所述p阱的顶部;所述pmos器件区的衬底中形成有n阱,所述第二源极区和所述第二漏极区形成于所述n阱的顶部。

46、与现有技术相比,本发明的技术方案具有以下有益效果:

47、1、本发明的半导体器件的制造方法,通过形成缓冲层于nmos器件区和pmos器件区的衬底上,且所述缓冲层覆盖栅极结构;去除所述nmos器件区上的缓冲层;形成应力层于所述缓冲层上;所述应力层为张应力层时,所述pmos器件区上的缓冲层厚度大于所述nmos器件区上的缓冲层厚度;所述应力层为压应力层时,所述nmos器件区上的缓冲层厚度大于所述pmos器件区上的缓冲层厚度,使得在提升nmos器件和pmos器件中的其中一个器件的性能且避免降低另一器件的性能的同时,还能避免增加芯片制造成本。

48、2、本发明的半导体器件,由于包括:缓冲层,形成于所述nmos器件区和所述pmos器件区的衬底上,且所述缓冲层覆盖所述栅极结构;应力层,形成于所述缓冲层上;所述应力层为张应力层时,所述pmos器件区上的缓冲层厚度大于所述nmos器件区上的缓冲层厚度;所述应力层为压应力层时,所述nmos器件区上的缓冲层厚度大于所述pmos器件区上的缓冲层厚度,使得在提升nmos器件和pmos器件中的其中一个器件的性能且避免降低另一器件的性能的同时,还能避免增加芯片制造成本。

- 还没有人留言评论。精彩留言会获得点赞!