阵列基板及其制备方法、显示装置与流程

本公开属于显示,具体涉及一种阵列基板及其制备方法、显示装置。

背景技术:

1、静电释放(electro-static discharge,esd)即两物电位差不相等,经由接触或感应所产生的放电现象。它存在于环境之中,放电作用通过线路时,电流脉冲无法被具保护的线路所疏通掉,瞬间通过的电流脉冲会将材料内部的温度提升至熔点,因此造成元件损伤。

2、影响静电大小的因素主要有不纯物的混入,不纯物的导电度高带静电量低、表面状态接触面积与压力(即接触面积越大),带静电越高,压力越大;带静电越高,即分离速度越快;带静电越高,元件受到esd冲击会产生剧变失效。元件在受到esd冲击,遭受到彻底破坏,元件不再有功能,这种失效是永久性的,这种esd可能使金属熔化,显示界面破坏,介电层破坏,这通常是因为在元件局部区域有高能量密度的放电所造成。元件受esd影响会存在潜在缺陷。这类缺陷比较难侦测,元件受到部分的伤害,有某程度的劣化,虽还有正常的功能,但是其生命周期明显的变短,若系统中有这种元件,常常会提早报废。

3、栅极绝缘层异物,是指到在栅极绝缘层沉积过程中因为腔室中的异物掉落,或者前制程异物未完全清理干净,此类异物会导致栅极绝缘层覆盖性不好,在源漏电极成膜时,会发生源漏电极和栅极金属的短路。

4、水汽引起的铜生长,在高温高湿环境中,由于温度和水汽的影响,铜金属的活性增强,容易在栅极绝缘层中发生铜离子的扩散。在加电显示时,由于栅极线和数据线存在电压差,跨线位置电流密度增加,更容易引起栅极绝缘层的微裂纹,微空洞的膜层缺陷,最终形成栅极线和数据线的短路。

5、由于跨线位置的栅极绝缘层相对较薄,基于以上三种原因,两层跨线位置金属更容易发生的短路,造成显示区的线类不良,也会造成周边区例如栅极驱动区黑屏及线类不良。

技术实现思路

1、本公开旨在至少解决现有技术中存在的技术问题之一,提供了一种阵列基板及其制备方法、显示装置

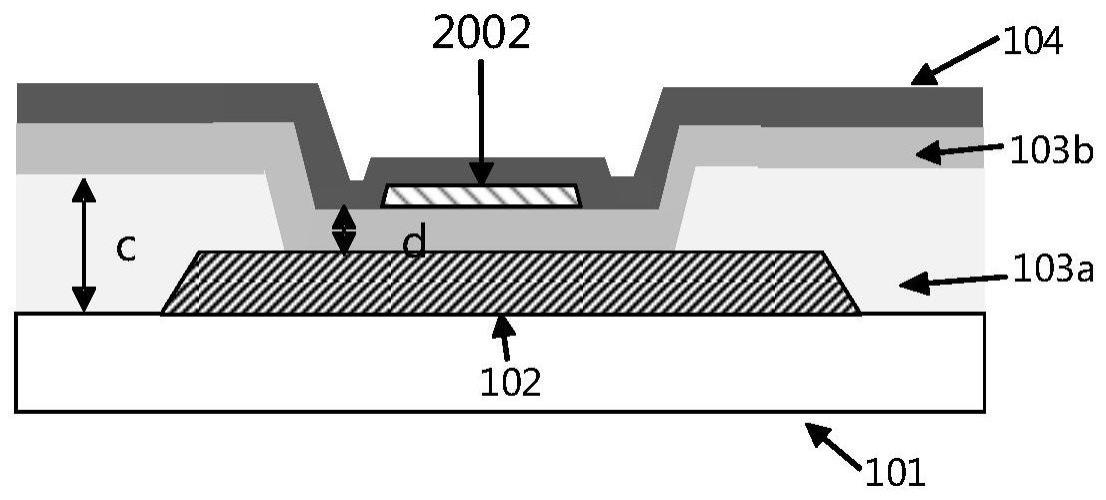

2、第一方面,本公开实施例提供了一种阵列基板,所述阵列基板包括:基底、位于所述基底且沿着背离所述基底方向依次设置的栅极线、第一栅极绝缘层、第二栅极绝缘层和数据线;所述栅极线和所述数据线交叉设置;所述第一栅极绝缘层的厚度大于或等于所述栅极线的厚度;所述阵列基板还包括:位于所述基底上的多个薄膜晶体管;所述薄膜晶体管包括:栅极;所述栅极为所述栅极线的一部分;

3、所述第一栅极绝缘层在所述栅极和所述数据线交叉位置设置有第一过孔;所述第一过孔在所述基底上的正投影落在所述栅极在所述基底上的正投影内;

4、所述第二栅极绝缘层和所述数据线在所述第一过孔处连续设置。

5、可选地,所述第一过孔在所述基底上的正投影与所述栅极在所述基底上正投影邻近的边缘之间的距离为0至10微米。

6、可选地,所述薄膜晶体管还包括:位于所述第二栅极绝缘层上的半导体层;

7、所述半导体层在所述基底上的正投影落在所述第一过孔在所述基底上的正投影内。

8、可选地,所述第二栅极绝缘层的厚度小于所述第一栅极绝缘层的厚度。

9、可选地,所述第一栅极绝缘层、所述第二栅极绝缘层的厚度为1000埃至10000埃。

10、可选地,所述薄膜晶体管还包括:位于所述第二栅极绝缘层上的源极和漏极;

11、所述源极和所述漏极分别与所述半导体层的两端电连接。

12、可选地,所述源极与所述数据线电连接,且二者为一体成型结构。

13、可选地,所述阵列基板还包括:位于所述源极和所述漏极上的钝化层、及位于所述钝化层上的像素电极;

14、所述像素电极通过贯穿所述钝化层的第二过孔与所述漏极电连接。

15、第二方面,本公开实施例提供了一种显示装置,所述显示装置包括如上述提供的阵列基板。

16、第三方面,本公开实施例提供了一种阵列基板的制备方法,所述阵列基板的制备方法包括:

17、在基底上形成栅极线;其中,薄膜晶体管的栅极为所述栅极线的一部分;

18、在所述栅极线上形成第一栅极绝缘层,并在所述第一栅极绝缘层与所述栅极对应的位置形成第一过孔;所述第一过孔在所述基底上的正投影落在所述栅极在所述基底上的正投影内;

19、在所述第一栅极绝缘层上形成第二栅极绝缘层和数据线,其中,所述第二栅极绝缘层和所述数据线在所述第一过孔处连续设置。

技术特征:

1.一种阵列基板,其特征在于,所述阵列基板包括:基底、位于所述基底且沿着背离所述基底方向依次设置的栅极线、第一栅极绝缘层、第二栅极绝缘层和数据线;所述栅极线和所述数据线交叉设置;所述第一栅极绝缘层的厚度大于或等于所述栅极线的厚度;所述阵列基板还包括:位于所述基底上的多个薄膜晶体管;所述薄膜晶体管包括:栅极;所述栅极为所述栅极线的一部分;

2.根据权利要求1所述的阵列基板,其特征在于,所述第一过孔在所述基底上的正投影与所述栅极在所述基底上正投影邻近的边缘之间的距离为0至10微米。

3.根据权利要求1所述的阵列基板,其特征在于,所述薄膜晶体管还包括:位于所述第二栅极绝缘层上的半导体层;

4.根据权利要求3所述的阵列基板,其特征在于,所述第二栅极绝缘层的厚度小于所述第一栅极绝缘层的厚度。

5.根据权利要求4所述的阵列基板,其特征在于,所述第一栅极绝缘层、所述第二栅极绝缘层的厚度为1000埃至10000埃。

6.根据权利要求3所述的阵列基板,其特征在于,所述薄膜晶体管还包括:位于所述第二栅极绝缘层上的源极和漏极;

7.根据权利要求6所述的阵列基板,其特征在于,所述源极与所述数据线电连接,且二者为一体成型结构。

8.根据权利要求6所述的阵列基板,其特征在于,所述阵列基板还包括:位于所述源极和所述漏极上的钝化层、及位于所述钝化层上的像素电极;

9.一种显示装置,其特征在于,所述显示装置包括如权利要求1至8任一项所述的阵列基板。

10.一种阵列基板的制备方法,其特征在于,所述阵列基板的制备方法包括:

技术总结

本公开提供一种阵列基板及其制备方法、显示装置,属于显示技术领域,其可解决现有的栅极线与数据线跨线的位置容易发生短路的问题。本公开的阵列基板包括:基底、位于基底且沿着背离基底方向依次设置的栅极线、第一栅极绝缘层、第二栅极绝缘层和数据线;栅极线和数据线交叉设置;第一栅极绝缘层的厚度大于或等于栅极线的厚度;阵列基板还包括:位于基底上的多个薄膜晶体管;薄膜晶体管包括:栅极;栅极为栅极线的一部分;第一栅极绝缘层在栅极和数据线交叉位置设置有第一过孔;第一过孔在基底上的正投影落在栅极在基底上的正投影内;第二栅极绝缘层和数据线在第一过孔处连续设置。

技术研发人员:王海宏,古宏刚,陈旭,孙语琳,袁玲

受保护的技术使用者:京东方科技集团股份有限公司

技术研发日:

技术公布日:2024/1/13

- 还没有人留言评论。精彩留言会获得点赞!