一种共源共栅型氮化镓器件及其制备方法、芯片与流程

本申请属于半导体器件,尤其涉及一种共源共栅型氮化镓器件及其制备方法、芯片。

背景技术:

1、共源共栅型氮化镓器件(gan cascode)是利用低压硅基金氧半场效晶体管(metal-oxide-semiconductor field-effect transistor,mosfet)与高压氮化镓高电子迁移率晶体管(gan high electron mobility transistor,gan hemt)组合而成的器件,该gan cascode器件集成了hemt的高耐压、高迁移率和低压mos的高可靠性优点,在当前gan的高压应用市场倍受欢迎。

2、但是,目前的gan cascode器件还存在的一个问题是无法很好的控制器件的电压变化率(dv/dt),从而导致器件存在电磁干扰(emi)效应,使得器件的开关损耗增加,限制了gan cascode的应用场景。

技术实现思路

1、本申请提供了一种共源共栅型氮化镓器件及其制备方法、芯片,旨在解决目前的gan cascode器件存在电磁干扰(emi)效应的问题。

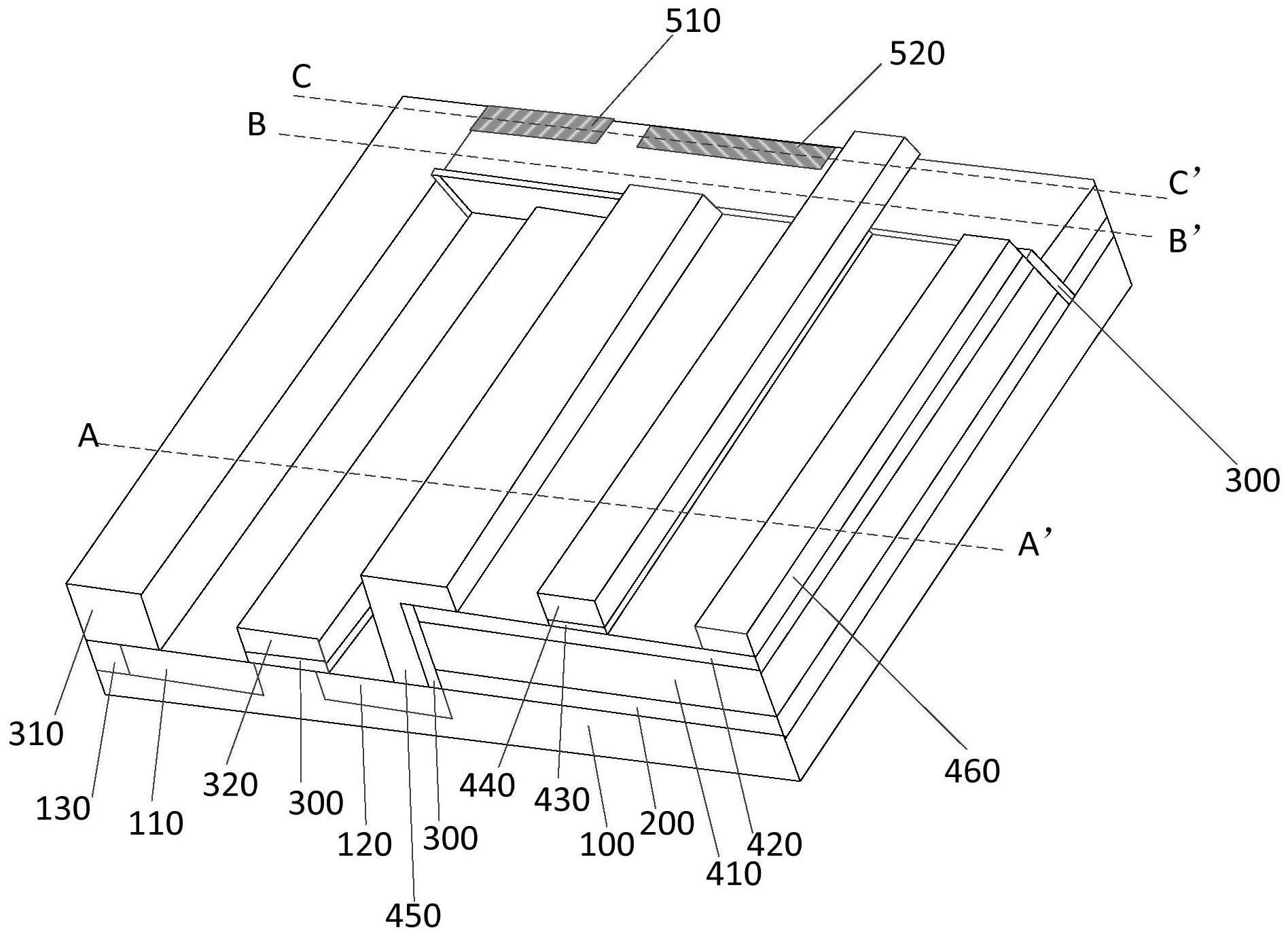

2、为了解决上述技术问题,本申请实施例第一方面提供了一种共源共栅型氮化镓器件,包括:

3、p型半导体衬底;

4、第一n型重掺杂区、第二n型重掺杂区、p型重掺杂区,分别形成于所述p型半导体衬底上的第一预设区域;其中,所述p型重掺杂区和所述第二n型重掺杂区位于所述第一n型重掺杂区的两侧,所述第一n型重掺杂区与所述第二n型重掺杂区互不接触;

5、l形缓冲层,形成于所述p型半导体衬底上,所述l形缓冲层的水平部和垂直部分别位于所述p型半导体衬底上的所述第一预设区域和第二预设区域;

6、隔离层,形成于所述第一n型重掺杂区、所述第二n型重掺杂区以及所述p型半导体衬底上的部分区域;其中,所述隔离层与所述l形缓冲层接触;

7、源极金属层,形成于所述隔离层的第一通孔内,且与所述p型重掺杂区与所述第一n型重掺杂区接触;

8、第一栅极金属层,形成于所述隔离层内,且位于所述第一n型重掺杂区与所述第二n型重掺杂区之间的中心线位置;

9、漂移层和势垒层,依次层叠形成于所述l形缓冲层上,且所述漂移层的形状与所述l形缓冲层的形状相同;

10、盖帽层和第二栅极金属层,依次层叠形成于所述势垒层上,且所述盖帽层位于所述第二栅极金属层和所述漂移层之间;

11、p型氮化镓掺杂区、n型氮化镓掺杂区,分别形成于所述漂移层上且所述n型氮化镓掺杂区位于所述p型氮化镓掺杂区与所述第二栅极金属层之间;

12、接触金属层,形成于所述隔离层上的第二通孔,且与所述第二n型重掺杂区和所述势垒层接触;

13、漏极金属层,形成于所述势垒层上,且与所述接触金属层分别位于所述第二栅极金属层的两侧。

14、在一个实施例中,所述隔离层还用于将所述第一栅极金属层与所述漂移层隔离。

15、在一个实施例中,所述p型重掺杂区与所述第一n型重掺杂区接触。

16、在一个实施例中,所述源极金属层、所述第二栅极金属层、所述第一n型重掺杂区、所述第二n型重掺杂区、所述p型重掺杂区的长度相同;所述源极金属层与所述p型氮化镓掺杂区接触。

17、在一个实施例中,所述n型氮化镓掺杂区和所述p型氮化镓掺杂区均与所述隔离层互不接触。

18、在一个实施例中,所述p型氮化镓掺杂区与所述n型氮化镓掺杂区互不接触。

19、在一个实施例中,所述第二栅极金属层与所述n型氮化镓掺杂区互不接触。

20、在一个实施例中,所述势垒层位于所述漂移层的垂直部上,所述n型氮化镓掺杂区和所述p型氮化镓掺杂区位于所述漂移层的水平部上。

21、本申请实施例第二方面还提供了一种共源共栅型氮化镓器件的制备方法,所述制备方法包括:

22、在p型半导体衬底的第一预设区域形成第一n型重掺杂区、第二n型重掺杂区、p型重掺杂区;其中,所述p型重掺杂区和所述第二n型重掺杂区位于所述第一n型重掺杂区的两侧,所述第一n型重掺杂区与所述第二n型重掺杂区互不接触;

23、在所述p型半导体衬底上形成l形缓冲层;其中,所述l形缓冲层的水平部和垂直部分别位于所述p型半导体衬底上的所述第一预设区域和第二预设区域;

24、在所述第一n型重掺杂区、所述第二n型重掺杂区以及所述p型半导体衬底上的部分区域上形成隔离层;其中,所述隔离层与所述l形缓冲层接触;

25、在所述隔离层的第一通孔内形成源极金属层;其中,源极金属层与所述p型重掺杂区以及所述第一n型重掺杂区接触;

26、在所述隔离层上形成第一栅极金属层,并在所述第一栅极金属层上形成隔离材料,以使所述隔离层包裹所述第一栅极金属层;其中,所述第一栅极金属层位于所述第一n型重掺杂区与所述第二n型重掺杂区之间的中心线位置;

27、在所述l形所述缓冲层上依次形成漂移层和势垒层;其中,所述漂移层的形状与所述l形缓冲层的形状相同;

28、在所述势垒层上形成盖帽层和第二栅极金属层;其中,所述盖帽层位于所述第二栅极金属层和所述漂移层之间;

29、在所述漂移层上形成p型氮化镓掺杂区、n型氮化镓掺杂区;其中,所述n型氮化镓掺杂区位于所述p型氮化镓掺杂区与所述第二栅极金属层之间;

30、在所述隔离层上的第二通孔形成接触金属层;其中,所述接触金属层与所述第二n型重掺杂区和所述势垒层接触;

31、在所述势垒层上形成漏极金属层;其中,所述漏极金属层与所述接触金属层分别位于所述第二栅极金属层的两侧。

32、本申请实施例第三方面还提供了一种芯片,包括如上述任一项实施例所述的共源共栅型氮化镓器件;或者包括由上述实施例所述的制备方法制备的共源共栅型氮化镓器件。

33、本申请实施例与现有技术相比存在的有益效果是:

34、通过在p型半导体衬底上形成第一n型重掺杂区、第二n型重掺杂区、p型重掺杂区、源极金属层、接触金属层、隔离层以及第一栅极金属层,进而形成mos器件,由接触金属层、漏极金属层、漂移层、势垒层、盖帽层以及第二栅极金属层形成hemt结构,并在源极金属层和第二栅极金属层之间通过p型掺杂和n型掺杂的方式形成快恢复二极管,并由隔离层隔离快恢复二极管与mos器件的有源区,在快恢复二极管与隔离层之间形成用于链接源极金属层和第二栅极金属层的栅极电阻,从而在氮化镓hemt器件的栅极基于快恢复二极管钳位链接电阻,达到将hemt的驱动回路的开通回路与关断回路分离的目的,既保证了hemt器件的开通速度,也可以消除电压变化过快导致的电磁效应,增强了共源共栅型氮化镓器件的性能和稳定性。

技术特征:

1.一种共源共栅型氮化镓器件,其特征在于,所述共源共栅型氮化镓器件包括:

2.根据权利要求1所述的共源共栅型氮化镓器件,其特征在于,所述隔离层还用于将所述第一栅极金属层与所述漂移层隔离。

3.根据权利要求1所述的共源共栅型氮化镓器件,其特征在于,所述p型重掺杂区与所述第一n型重掺杂区接触。

4.根据权利要求3所述的共源共栅型氮化镓器件,其特征在于,所述源极金属层、所述第二栅极金属层、所述第一n型重掺杂区、所述第二n型重掺杂区、所述p型重掺杂区的长度相同;

5.根据权利要求4所述的共源共栅型氮化镓器件,其特征在于,所述n型氮化镓掺杂区和所述p型氮化镓掺杂区均与所述隔离层互不接触。

6.根据权利要求1-5任一项所述的共源共栅型氮化镓器件,其特征在于,所述p型氮化镓掺杂区与所述n型氮化镓掺杂区互不接触。

7.根据权利要求1-5任一项所述的共源共栅型氮化镓器件,其特征在于,所述第二栅极金属层与所述n型氮化镓掺杂区互不接触。

8.根据权利要求1-5任一项所述的共源共栅型氮化镓器件,其特征在于,所述势垒层位于所述漂移层的垂直部上,所述n型氮化镓掺杂区和所述p型氮化镓掺杂区位于所述漂移层的水平部上。

9.一种共源共栅型氮化镓器件的制备方法,其特征在于,所述制备方法包括:

10.一种芯片,其特征在于,包括如权利要求1-8任一项所述的共源共栅型氮化镓器件;或者包括由权利要求9所述的制备方法制备的共源共栅型氮化镓器件。

技术总结

本申请属于半导体技术领域,提供了一种共源共栅型氮化镓器件及其制备方法、芯片,通过在P型半导体衬底上形成第一N型重掺杂区、第二N型重掺杂区、P型重掺杂区、源极金属层、接触金属层、隔离层以及第一栅极金属层,进而形成MOS器件,由接触金属层、漏极金属层、漂移层、势垒层、盖帽层以及第二栅极金属层形成HEMT器件,在源极金属层和第二栅极金属层之间形成快恢复二极管,由隔离层隔离PN结与MOS器件的有源区,在快恢复二极管与隔离层之间形成用于链接源极金属层和第二栅极金属层的栅极电阻,从而将HEMT的驱动回路的开通回路与关断回路分离,既保证了HEMT器件的开通速度,也可以消除电压变化过快导致的电磁效应。

技术研发人员:刘杰

受保护的技术使用者:天狼芯半导体(成都)有限公司

技术研发日:

技术公布日:2024/1/13

- 还没有人留言评论。精彩留言会获得点赞!