一种多异构芯片的晶圆级封装结构的制作方法与流程

本发明涉及半导体封装,尤其涉及一种多异构芯片的晶圆级封装结构的制作方法。

背景技术:

1、晶圆级封装(wlp,wafer leve l package)指的是直接在晶圆上进行大多数或是全部的封装测试程序,之后再进行切割(s i ngu l at i on)制成单颗组件。wlp封装具有较小封装尺寸与较佳电性表现的优势,目前多用于低脚数消费性i c的封装应用。例如,中国专利cn 114823592 a公开的一种晶上系统结构及其制备方法,该晶上系统结构是一种晶圆级封装结构,包括晶圆基板、集成芯粒、系统配置板和系统散热模组。

2、然而,现有的晶圆级封装结构存在晶圆级多芯片连接的数量有限,晶圆级芯片间互连线的数量受限,晶圆级芯片间带宽受限,并且需要借道转接板或者基板或者pcb板,晶圆级芯片间通信通路长,此外,还存在供电通路长,散热效果差等问题。

技术实现思路

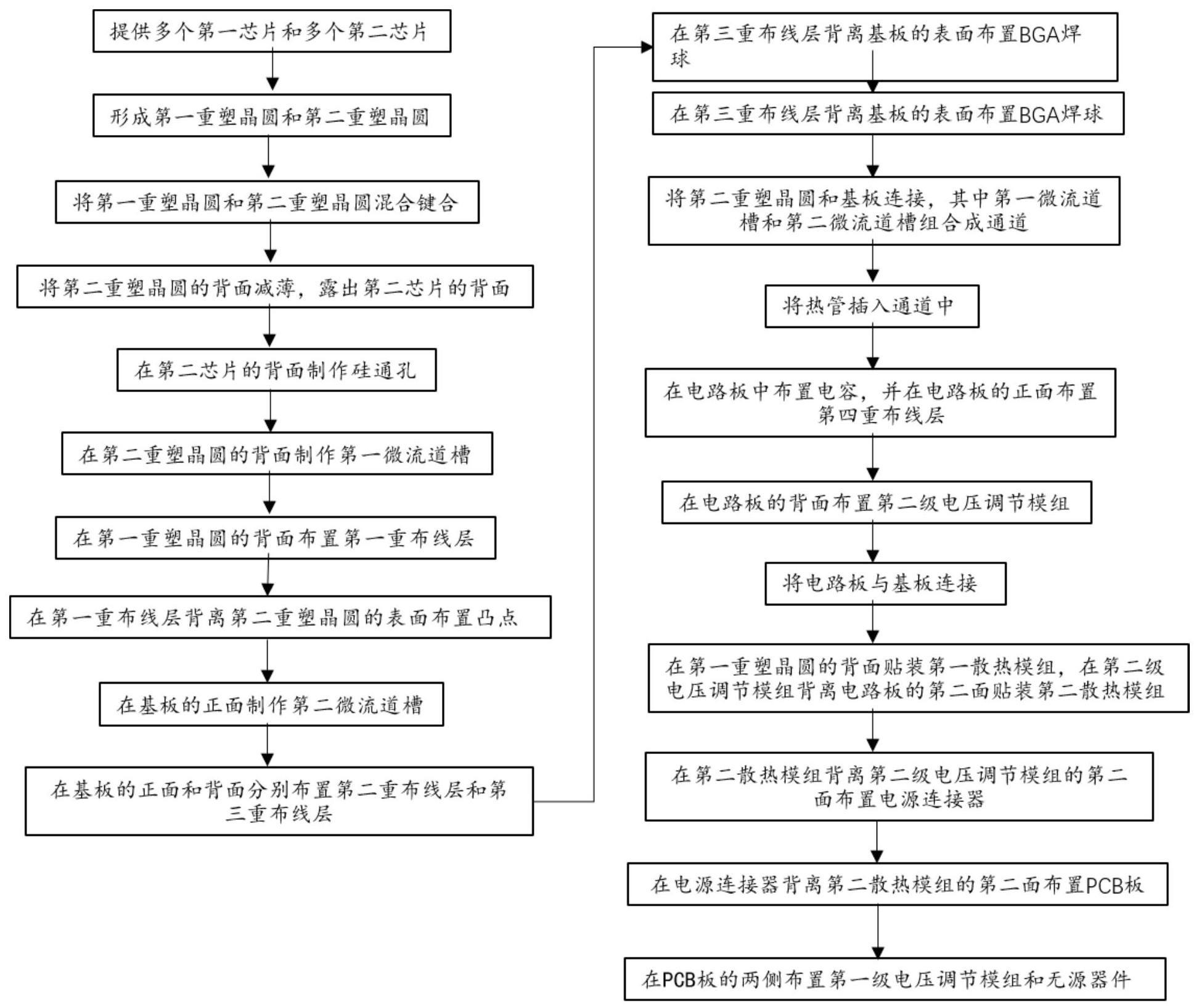

1、为解决现有技术中的上述问题中的至少一部分问题,本发明提供一种多异构芯片的晶圆级封装结构的制作方法,包括:

2、将多个第一芯片塑封形成第一重塑晶圆,将多个第二芯片塑封形成第二重塑晶圆,其中第一芯片与第二芯片不同;

3、将第一重塑晶圆和第二重塑晶圆混合键合,其中第一芯片正面的电极与第二芯片正面的电极键合。

4、进一步地,第一重塑晶圆中的第一芯片与第二重塑晶圆中的第二芯片错位互连,其中一个第二芯片与相邻的多个第一芯片通过电极混合键合电连接。

5、进一步地,还包括:

6、将第二重塑晶圆的背面减薄,露出第二芯片的背面;

7、在第二芯片的背面制作硅通孔,其中硅通孔电连接第二芯片正面的电极;

8、在第二重塑晶圆的背面制作第一微流道槽;

9、在第二重塑晶圆的背面布置第一重布线层,其中第一重布线层与硅通孔电连接;以及

10、在第一重布线层背离第二重塑晶圆的表面布置凸点。

11、进一步地,还包括:

12、在基板的正面制作第二微流道槽;

13、在基板的正面和背面分别布置第二重布线层和第三重布线层;

14、在第三重布线层背离基板的表面布置bga焊球;

15、通过将凸点与基板正面第二重布线层连接,以将第二重塑晶圆和基板连接,其中第二重塑晶圆和基板连接后,第二微流道槽与第一微流道槽对齐组合成通道;

16、将热管插入通道中。

17、进一步地,还包括:在电路板中布置电容,并在电路板的正面布置第四重布线层;

18、在电路板的背面布置第二级电压调节模组,其中第二级电压调节模组与电路板中的电容电连接;

19、通过将电路板正面的第四重布线层与bga焊球连接以将电路板与基板连接。

20、进一步地,还包括:

21、在第一重塑晶圆的背面贴装第一散热模组,在第二级电压调节模组背离电路板的第二面贴装第二散热模组;

22、在第二散热模组背离第二级电压调节模组的第二面布置电源连接器;

23、在电源连接器背离第二散热模组的第二面布置pcb板;

24、在pcb板的两侧布置第一级电压调节模组和无源器件。

25、进一步地,热管的直径等于第一微流道槽的深度、第二微流道槽的深度、第一重布线层的厚度、第二重布线层的厚度以及凸点的高度的和;

26、所述热管纵向排布在基板的正面,且位于凸点之间的间隙。

27、进一步地,所述在电路板中布置电容包括:

28、在电路板中刻蚀出凹槽,并在每个凹槽的内壁布置两个相对的金属管,作为电容的上极板和下极板,然后在凹槽内布置绝缘材料形成隔离层,形成电容。

29、进一步地,所述第二散热模组中具有预留孔。

30、进一步地,所述电源连接器与所述第二级电压调节模组利用线路通过第二散热模组的预留孔电连接。

31、本发明至少具有下列有益效果:本发明公开的一种多异构芯片的晶圆级封装结构的制作方法,通过将计算芯片与接口芯片塑封成两个重塑晶圆,并将两个重塑晶圆键合,使得两个重塑晶圆中可以连接多达几十个异构芯片,而且异构芯片之间直接通过芯片上的电极连接,极大提升了计算芯片与接口芯片之间连线数量,能够从几百个到几十万个,使得带宽从gb/s提升到tb/s,且通信链路缩短;通过该制作方法制作的圆级封装结构采用垂直供电结构进行供电,缩短供电通路的长度;通过该制作方法制作的圆级封装结构的不同位置布置3个散热模组,其中中间的热管散热模组直接与芯片接触,达到近热源高效散热的目标,提升了散热效果,而且热管不需要进液口和出液口,液体内部循环工作,热管利用液体蒸发和冷凝循环能够实现最有效的传热方式,能够为芯片快速散热,散热效果优良。

技术特征:

1.一种多异构芯片的晶圆级封装结构的制作方法,其特征在于,包括:

2.根据权利要求1所述的多异构芯片的晶圆级封装结构的制作方法,其特征在于,第一重塑晶圆中的第一芯片与第二重塑晶圆中的第二芯片错位互连,其中一个第二芯片与相邻的多个第一芯片通过电极混合键合电连接。

3.根据权利要求1所述的多异构芯片的晶圆级封装结构的制作方法,其特征在于,还包括:

4.根据权利要求3所述的多异构芯片的晶圆级封装结构的制作方法,其特征在于,还包括:

5.根据权利要求4所述的多异构芯片的晶圆级封装结构的制作方法,其特征在于,还包括:在电路板中布置电容,并在电路板的正面布置第四重布线层;

6.根据权利要求5所述的多异构芯片的晶圆级封装结构的制作方法,其特征在于,还包括:

7.根据权利要求4所述的多异构芯片的晶圆级封装结构的制作方法,其特征在于,热管的直径等于第一微流道槽的深度、第二微流道槽的深度、第一重布线层的厚度、第二重布线层的厚度以及凸点的高度的和;

8.根据权利要求5所述的多异构芯片的晶圆级封装结构的制作方法,其特征在于,所述在电路板中布置电容包括:

9.根据权利要求6所述的多异构芯片的晶圆级封装结构的制作方法,其特征在于,所述第二散热模组中具有预留孔。

10.根据权利要求9所述的多异构芯片的晶圆级封装结构的制作方法,其特征在于,所述电源连接器与所述第二级电压调节模组利用线路通过第二散热模组的预留孔电连接。

技术总结

本发明涉及一种多异构芯片的晶圆级封装结构的制作方法,包括:将多个第一芯片塑封形成第一重塑晶圆,将多个第二芯片塑封形成第二重塑晶圆,其中第一芯片与第二芯片不同;将第一重塑晶圆和第二重塑晶圆混合键合,其中第一芯片正面的电极与第二芯片正面的电极键合。通过将第一芯片与第二芯片塑封成两个重塑晶圆,并将两个重塑晶圆键合,使得两个重塑晶圆中可以连接多达几十个异构芯片,而且异构芯片之间直接通过芯片上的电极连接,极大提升了计算芯片与接口芯片之间连线数量,并使得带宽提升,且通信链路缩短。

技术研发人员:姜申飞,朱小云,胡杨,潘岳,李霞,王立华,王磊,郝培霖,莫志文

受保护的技术使用者:上海人工智能创新中心

技术研发日:

技术公布日:2024/1/14

- 还没有人留言评论。精彩留言会获得点赞!