一种半导体结构及其制备方法与流程

本发明涉及半导体,尤其涉及但不限于一种三维堆叠半导体结构及其制备该三维堆叠半导体结构的方法。

背景技术:

1、按照摩尔定律,继续通过缩小晶体管的特征尺寸来提升集成电路的性能,已变得越发困难。三维集成电路(three dimensional integrated circuit,3d ic)作为超越摩尔定律的重要研究和应用方向,将根本改变集成电路的发展趋势。3d ic是将两个或两个以上的功能芯片在垂直方向上进行堆叠,采用如混合键合(hybrid bonding)或tsv(throughsilicon via,硅通孔)或微凸块(micro bump)等技术实现电气互连,形成三维堆叠芯片。

2、相关技术中有一种高带宽存储器(high bandwidth memory,hbm)的技术可以将多个相同的晶圆或芯片在垂直方向上堆叠封装起来,其制成的三维堆叠芯片可以实现高密度的互连,芯片直接互连使得信号传输路径更短,速度更快,且为实现具有复杂功能的芯片提供可能,而且3d ic封装大大减小了封装体的尺寸。

3、相关技术中,多个相同晶圆或芯片的制造工艺过程中,需要采用光刻工艺对其进行图案化,均需要使用到对准技术。在对准工艺时所使用的激光可以穿透堆叠后多个晶圆或芯片的厚度,当使用多个相同晶圆或芯片堆叠时各晶圆或芯片上的对准标记所在的位置也都是相同的,就会导致在对准时当前晶圆或芯片上的对准标记的图形和信号受到下面一个晶圆或芯片上的对准标记的影响,这样的对准问题是导致三维堆叠芯片对准偏差的主要因素。

4、如何在三维堆叠芯片制备工艺中减少对准偏差,提高对准精度,增加光刻工艺整体性能是当下亟待解决的问题。

技术实现思路

1、本发明解决的技术问题是提供一种三维堆叠半导体结构及其制备该三维堆叠半导体结构的方法,以解决现有技术中三维堆叠半导体结构中的对准标记相互影响导致对准偏差的技术问题。

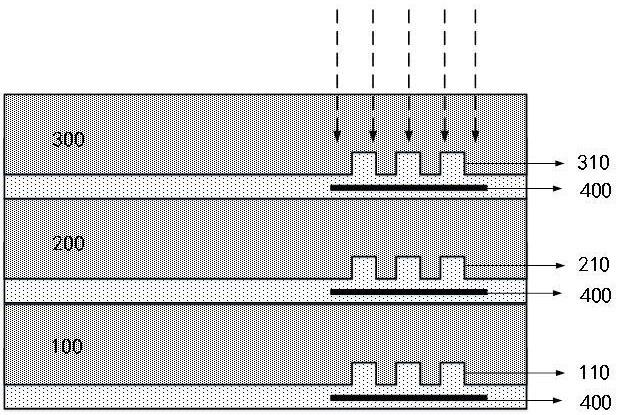

2、为解决上述技术问题,本发明技术方案提供一种半导体结构,包括:第一晶圆层100,其具有第一表面和第二表面,所述第一晶圆层100的第一表面上具有第一图形结构110,所述第一图形结构110上方具有光阻挡层400;第二晶圆层200,其具有第一表面和第二表面,所述第二晶圆层200的第一表面上具有第二图形结构210,所述第二图形结构210上方具有光阻挡层400,所述第二晶圆层200堆叠在所述第一晶圆层100上。

3、进一步的,还包括:第三晶圆层300,其具有第一表面和第二表面,所述第三晶圆层300的第一表面上具有第三图形结构310,所述第三图形结构310上方具有光阻挡层400,所述第三晶圆层300堆叠在所述第二晶圆层200上。

4、进一步的,所述第一晶圆层100、所述第二晶圆层200、所述第三晶圆层300的第一表面为晶圆层的正面,其上具有有源区;所述第一晶圆层100、所述第二晶圆层200、所述第三晶圆层300的第二表面为晶圆层的背面,其上具有键合结构。

5、进一步的,在垂直投影方向上,所述光阻挡层400完全遮挡住所述第一图形结构110、所述第二图形结构210、所述第三图形结构310。

6、进一步的,所述光阻挡层400为单独设置在所述第一图形结构110、所述第二图形结构210、所述第三图形结构310上方的一层结构。

7、进一步的,所述光阻挡层400为晶圆制备过程中的一功能层结构,延伸至所述第一图形结构110、所述第二图形结构210、所述第三图形结构310上方。

8、进一步的,所述光阻挡层400采用透光率小吸光度大的材料层制备形成的。

9、进一步的,所述光阻挡层400采用金属钨层制备形成的。

10、本发明技术方案还提供一种半导体结构的制备方法,所述制备方法包括:

11、提供第一晶圆层100,其具有第一表面和第二表面,在所述第一晶圆层100的第一表面上形成第一图形结构110;

12、在所述第一图形结构110沉积上第一介质层,对所述第一介质层进行平坦化;

13、在所述第一介质层上沉积一层光阻挡材料层;

14、对所述光阻挡材料层进行图案化形成光阻挡层400,所述光阻挡层400位于所述第一图形结构110上方;

15、在所述光阻挡层400上沉积上第二介质层,对所述第二介质层进行平坦化;

16、进一步的,将所述第一晶圆层100的第一表面堆叠在载体晶圆层上并进行翻转,对所述第一晶圆层100的第二表面进行减薄工艺。

17、进一步的,提供第二晶圆层200,其具有第一表面和第二表面,在所述第二晶圆层200的第一表面上形成第二图形结构210;

18、在所述第二图形结构210沉积上第一介质层,对所述第一介质层进行平坦化;

19、在所述第一介质层上沉积一层光阻挡材料层;

20、对所述光阻挡材料层进行图案化形成光阻挡层400,所述光阻挡层400位于所述第二图形结构210上方;

21、在所述光阻挡层上沉积上第二介质层,对所述第二介质层进行平坦化;

22、将所述第二晶圆层200的第一表面堆叠在所述第一晶圆层100的第二表面上并进行翻转,对所述第二晶圆层200的第二表面进行减薄工艺。

23、进一步的,提供第三晶圆层300,其具有第一表面和第二表面,在所述第三晶圆层300的第一表面上形成第三图形结构310;

24、在所述第三图形结构310沉积上第一介质层,对所述第一介质层进行平坦化;

25、在所述第一介质层上沉积一层光阻挡材料层;

26、对所述光阻挡材料层进行图案化形成光阻挡层400,所述光阻挡层400位于所述第三图形结构310上方;

27、在所述光阻挡层400上沉积上第二介质层,对所述第二介质层进行平坦化;

28、将所述第三晶圆层300的第一表面堆叠在所述第二晶圆层200的第二表面上并进行翻转,对所述第三晶圆层300的第二表面进行减薄工艺。

29、进一步的,所述第一晶圆层100、所述第二晶圆层200、所述第三晶圆层300的第一表面为晶圆层的正面,其上具有有源区;所述第一晶圆层100、所述第二晶圆层200、所述第三晶圆层300的第二表面为晶圆层的背面,其上具有键合结构。

30、进一步的,在垂直投影方向上,所述光阻挡层400完全遮挡住所述第一图形结构110、所述第二图形结构210、所述第三图形结构310。

31、进一步的,所述光阻挡层400为单独设置在所述第一图形结构110、所述第二图形结构210、所述第三图形结构310上方的一层结构。

32、进一步的,所述光阻挡层400为晶圆制备过程中的一功能层结构,延伸至所述第一图形结构110、所述第二图形结构210、所述第三图形结构310上方。

33、进一步的,所述光阻挡层400采用透光率小吸光度大的材料层制备形成的。

34、进一步的,所述光阻挡层400采用金属钨层制备形成的。

35、综上所述,本发明的半导体结构及其制备方法具有下列优点:

36、1、本发明提供的半导体结构可以使多片堆叠的相同晶圆或芯片在制造对准标记层时使用相同的光刻掩模版,无需像现有技术中通过不停地更换对准标记层的光刻掩模版来制备对准标记位置不同的晶圆或芯片,这样大大减少了晶圆制造过程中的复杂度以及生产成本;

37、2、本发明提供的半导体结构中的多片晶圆层可以做成完全相同的晶圆层,可以彼此之间相互替换,减少晶圆特殊配对过程中造成的浪费;

38、3、本发明提供的半导体结构中的多片晶圆层制作过程中可使用相同的光刻掩模版,避免了现有技术中制作多块不同的光刻掩模版的情况,大大减少光刻掩模版的制造成本;

39、4、本发明提供的半导体结构中的光阻挡层,能有效避免光刻对准工艺时,下层晶圆上的对准标记结构对上层晶圆上的对准标记结构的干扰,大大减少对准偏差,提高对准精度。

- 还没有人留言评论。精彩留言会获得点赞!