一种具有GaN基多沟道凹槽MIS结合PN结栅的垂直晶体管及其制作方法与流程

本发明涉及微电子器件技术及工艺领域,具体是指一种具有gan基多沟道凹槽mis结合pn结栅的垂直晶体管及其制作方法。

背景技术:

1、继第一代半导体si和ge以及第二代半导体gaas之后的以gan为代表的第三代半导体材料,因为其所具有的优良的特性,在现代电子技术领域具有得天独厚的应用优势。

2、gan因为禁带宽度大,击穿电场高,电子饱和速度大使其具有耐高温,耐高压,抗辐射的优良特性。这些优良的特性使得第三代半导体gan在电力电子领域的应用具有极强的竞争力。

3、特别是其与algan材料结合,因为其自身所具有的自发极化和两者结合产生的压电极化效应,在结合成异质结之后,可以在异质结界面形成具有极高迁移率的二维电子气,而且形成的电子气密度可以通过调节algan势垒层的厚度和al组分进行调控。

4、以这一异质结为基础制备的高电子迁移率晶体管hemt器件,在高频大功率方面具有十分巨大的应用空间。尤其是多沟道结构的gan基hemt器件因其所具有的大电流特性,在电力电子领域十分具有优势。

5、所以,近年来对多沟道器件的研究十分广泛,也十分具有诱惑力,是国内外研究者都比较关注的研究方向。而且,这种algan/gan组合所形成的异质结构不断叠加形成的多沟道层,可以进一步提高器件的输出饱和电流。

6、然而目前所形成的多沟道器件结构中,大多采用的平面栅极结构,其对栅极下方更深沟道的2deg的控制能力因为距离太远有所下降,同时也因为栅极金属与半导体材料所形成的肖特基接触也可能造成器件的栅极漏电大幅度提高。所形成的高饱和输出电流的器件可能会因为漏电区域增多而降低整体器件的耐压能力。

7、所以,一种测量更加精确的用于x射线探伤机的辅助装置成为人们亟待解决的问题。

技术实现思路

1、本发明要解决的技术问题是然而目前所形成的多沟道器件结构中,大多采用的平面栅极结构,其对栅极下方更深沟道的2deg的控制能力因为距离太远有所下降,同时也因为栅极金属与半导体材料所形成的肖特基接触也可能造成器件的栅极漏电大幅度提高。所形成的高饱和输出电流的器件可能会因为漏电区域增多而降低整体器件的耐压能力。

2、为解决上述技术问题,本发明提供的技术方案为:一种具有gan基多沟道凹槽mis结合pn结栅的垂直晶体管,所述垂直晶体管包括gan衬底层、n-gan渡越层、gan外延层、多沟道结构、栅极凹槽、栅极叠层结构、源极窗口、源极、漏极和栅极;

3、所述多沟道结构包括多层相间的gan沟道层和algan势垒层;

4、所述栅极叠层结构包括由下至上叠设的n型gan外延层、p型gan外延层、栅槽介质层;

5、所述n-gan渡越层设置于gan衬底层上,所述gan外延层设置于n-gan渡越层上,所述多沟道结构设置于gan外延层上,所述栅极凹槽设置于多沟道结构中心处,所述栅极叠层结构设置于栅极凹槽中,所述源极窗口设置于多沟道结构外侧面上,所述源极设置于源极窗口中,所述漏极设置于gan衬底层下侧面上,所述栅极设置于栅极叠层结构上,所述gan外延层具有电流阻挡层。

6、进一步的,所述n-gan渡越层的厚度为3-30um,所述gan外延层的厚度为1-3um,所述gan沟道层的厚度为50-100nm,algan势垒层的厚度为20-50nm,所述n型gan外延层的厚度为10-20nm,所述p型gan外延层的厚度为10-20nm,所述栅槽介质层的厚度为30nm,所述源极窗口的厚度为5-10um。

7、进一步的,所述栅极叠层结构与栅极凹槽形成mis接触。

8、一种具有gan基多沟道凹槽mis结合pn结栅的垂直晶体管的制作方法,包含一种具有gan基多沟道凹槽mis结合pn结栅的垂直晶体管,所述垂直晶体管的制作方法如下所示:

9、步骤1、选取自支撑gan材料作为衬底层;

10、步骤2、在自支撑gan衬底层上,生长n-gan外延层,作为载流子渡越层,提高器件击穿电压;

11、步骤3、在n-gan渡越层上,生长gan外延层,在gan外延层形成部分电流阻挡层,使得电流集中垂直流动;

12、步骤4、通过mocvd工艺外延生长多层algan势垒层和gan沟道层,形成多沟道结构;

13、步骤5、通过干法选择性刻蚀形成栅极凹槽;

14、步骤6、将n型gan外延层、p型gan外延层以及栅槽介质层三者相结合形成栅极叠层结构叠设于栅极凹槽中;

15、步骤7、除去最上层的algan/gan异质结构,形成源极窗口;

16、步骤8、在步骤7形成的最上层的源极窗口上沉淀源极金属;

17、步骤9、在最下层的自支撑gan上淀积漏极金属;

18、步骤10、在完成台面隔离的基片上进行栅电极光刻,在步骤6形成的凹槽叠层上完成金属淀积,形成栅极。

19、本发明与现有技术相比的优点在于:本发明通过实现垂直结构使得器件电流可以垂直流通,使得gan材料的高击穿特性得到更加充分地体现,同时在单位面积上增大器件有源区从而实现更高的电流密度,相比于横向hemt,单位面积电流密度更高,适合商业化;

20、本发明利用algan/gan异质结多层叠加所形成的多沟道结构,能够生成更多的2deg,使得整体器件的2deg浓度得到大幅度提高,从而可以极大的提高器件的饱和输出电流,从而使得器件的功率有所提高,使得在大功率应用方面具有极大的优势;

21、本发明通过将凹栅mis结构与pn结相结合起来,除了在栅极处刻槽引入介质层之外,还引入了pn结,形成pn结和介质的叠层结构,极大地抑制了器件的栅极漏电,提高器件的栅极的耐压能力,从而使得栅极电压摆幅得到大幅度提高。同时凹栅结构的引入使得器件的栅极能够很好的控制距离较远的沟道,从而提高器件的栅控能力;本发明设计合理,值得大力推广。

技术特征:

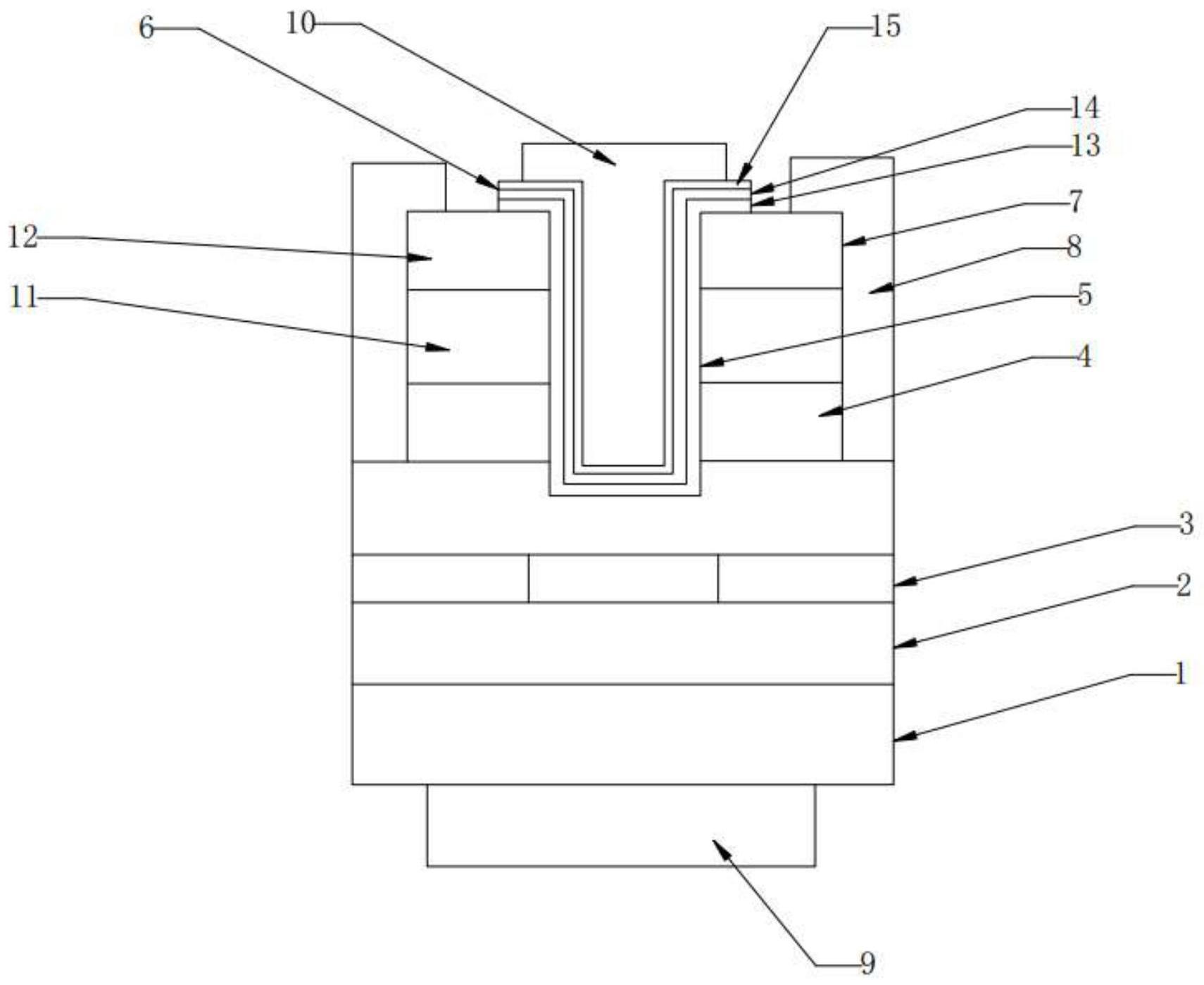

1.一种具有gan基多沟道凹槽mis结合pn结栅的垂直晶体管,其特征在于:所述垂直晶体管包括gan衬底层(1)、n-gan渡越层(2)、gan外延层(3)、多沟道结构(4)、栅极凹槽(5)、栅极叠层结构(6)、源极窗口(7)、源极(8)、漏极(9)和栅极(10);

2.根据权利要求1所述的一种具有gan基多沟道凹槽mis结合pn结栅的垂直晶体管,其特征在于:所述n-gan渡越层(2)的厚度为3-30um,所述gan外延层(3)的厚度为1-3um,所述gan沟道层(11)的厚度为50-100nm,algan势垒层(12)的厚度为20-50nm,所述n型gan外延层(13)的厚度为10-20nm,所述p型gan外延层(14)的厚度为10-20nm,所述栅槽介质层(15)的厚度为30nm,所述源极窗口(7)的厚度为5-10um。

3.根据权利要求1所述的一种具有gan基多沟道凹槽mis结合pn结栅的垂直晶体管,其特征在于:所述栅极叠层结构(6)与栅极凹槽(5)形成mis接触。

4.一种具有gan基多沟道凹槽mis结合pn结栅的垂直晶体管的制作方法,包含权利要求1-3所述的一种具有gan基多沟道凹槽mis结合pn结栅的垂直晶体管,其特征在于:所述垂直晶体管的制作方法如下所示:

技术总结

本发明专利公开了一种具有GaN基多沟道凹槽MIS结合PN结栅的垂直晶体管及其制作方法,所述垂直晶体管包括GaN衬底层、n‑GaN渡越层、GaN外延层、多沟道结构、栅极凹槽、栅极叠层结构、源极窗口、源极、漏极和栅极;所述多沟道结构包括多层相间的GaN沟道层和AlGaN势垒层;所述栅极叠层结构包括由下至上叠设的n型GaN外延层、p型GaN外延层、栅槽介质层;本发明通过实现垂直结构使得器件电流可以垂直流通,使得GaN材料的高击穿特性得到更加充分地体现,同时在单位面积上增大器件有源区从而实现更高的电流密度,相比于横向HEMT,单位面积电流密度更高,适合商业化。

技术研发人员:白俊春,程斌,平加峰,贾永

受保护的技术使用者:上海格晶半导体有限公司

技术研发日:

技术公布日:2024/1/13

- 还没有人留言评论。精彩留言会获得点赞!