半导体器件的制备方法与流程

本发明涉及半导体,尤其涉及一种半导体器件的制备方法。

背景技术:

1、在半导体器件的制备工艺中,形成栅极结构、源区和漏区后,为了降低互连工艺中的接触电阻,会先在源区、漏区及栅极结构上形成金属硅化物。形成金属硅化物的步骤是先形成金属层覆盖衬底及栅极结构,然后执行二道退火工艺,以在源区、漏区及栅极结构上形成金属硅化物。在进行第一退火工艺时,金属向衬底内扩散形成金属硅化物;在进行更高温度的第二退火工艺时,衬底中的硅向金属硅化物内扩散;即在第一退火工艺时金属是主要扩散物,金属进入界面与衬底反应,但在第二退火工艺时衬底中的硅是主要扩散物,硅向金属硅化物内快速扩散。

2、图1为现有技术中半导体器件存在空洞的电镜图。请参考图1,当第二退火工艺中硅向金属硅化物内快速扩散时,容易在栅极结构的侧边缘下方的衬底中形成空洞(图中白色圆形虚框所示),此空洞会导致沟道电阻增加,所需的驱动电流变小,影响器件的电性能。

技术实现思路

1、本发明的目的在于提供一种半导体器件的制备方法,能够有效防止沟道电阻增加,从而提高器件的电性能。

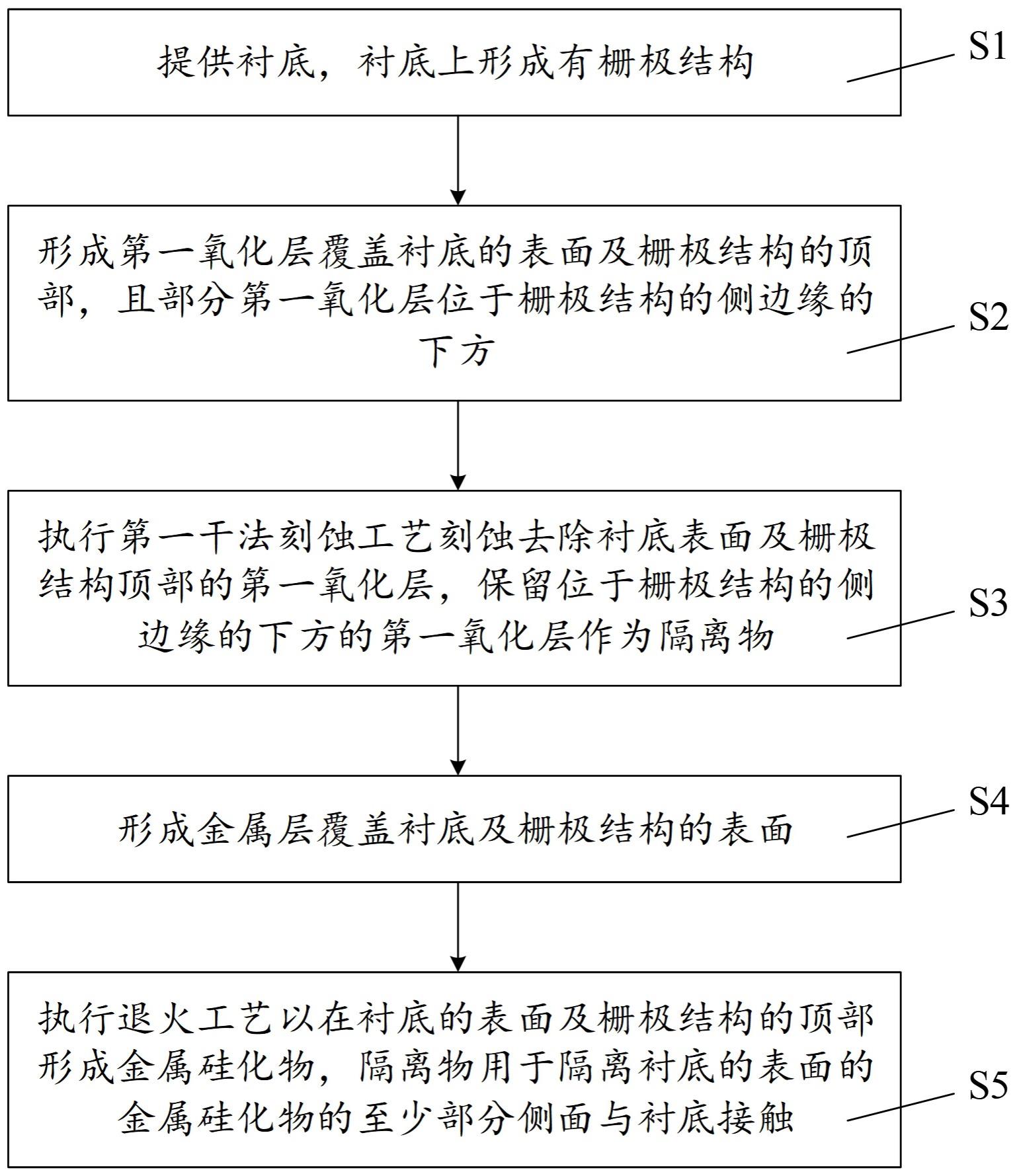

2、为了达到上述目的,本发明提供了一种半导体器件的制备方法,包括:

3、提供衬底,所述衬底上形成有栅极结构;

4、形成第一氧化层覆盖所述衬底的表面及所述栅极结构的顶部,且部分所述第一氧化层位于所述栅极结构的侧边缘的下方;

5、执行第一干法刻蚀工艺刻蚀去除所述衬底表面及所述栅极结构顶部的第一氧化层,保留位于所述栅极结构的侧边缘的下方的第一氧化层作为隔离物;

6、形成金属层覆盖所述衬底及所述栅极结构的表面;以及,

7、执行退火工艺以在所述衬底的表面及所述栅极结构的顶部形成金属硅化物,所述隔离物用于隔离所述衬底的表面的金属硅化物的至少部分侧面与所述衬底接触。

8、可选的,采用热氧化工艺形成所述第一氧化层。

9、可选的,所述第一氧化层的厚度为80埃~100埃。

10、可选的,所述第一干法刻蚀工艺的刻蚀气体包括ch4和h2,ch4和h2的气体流量比包括7:3、3:2或1:1。

11、可选的,所述第一干法刻蚀工艺的刻蚀时间为2秒~5秒。

12、可选的,所述栅极结构包括栅氧化层、栅极多晶硅层及侧墙,所述栅氧化层及所述栅极多晶硅层依次堆叠于所述衬底上,所述侧墙覆盖所述栅极多晶硅层及所述栅氧化层的侧面,部分所述第一氧化层位于所述侧墙的下方。

13、可选的,执行所述退火工艺以在所述衬底的表面及所述栅极结构的顶部形成金属硅化物的步骤包括:

14、执行第一退火工艺以在所述衬底的表面及所述栅极结构的顶部形成金属硅化物,所述隔离物用于隔离所述衬底的表面的金属硅化物的至少部分侧面与所述衬底接触;

15、执行第二退火工艺以降低所述金属硅化物的阻值。

16、可选的,所述第一退火工艺的退火温度为400摄氏度~600摄氏度,所述第二退火工艺的退火温度大于700摄氏度。

17、可选的,所述金属硅化物包括硅化钴。

18、可选的,所述衬底包括第一区域和第二区域,所述栅极结构位于所述第一区域上,在形成第一氧化层覆盖所述衬底的表面及所述栅极结构的顶部之前,还包括:

19、形成第二氧化层覆盖所述第一区域和所述第二区域;

20、执行第二干法刻蚀工艺刻蚀去除所述第一区域上部分厚度的第二氧化层;以及,

21、执行湿法刻蚀工艺刻蚀去除所述第一区域上剩余厚度的第二氧化层,保留所述第二区域上的第二氧化层。

22、在本发明提供的半导体器件的制备方法中,提供衬底,衬底上形成有栅极结构;形成第一氧化层覆盖衬底的表面及栅极结构的顶部,且部分第一氧化层位于栅极结构的侧边缘的下方;执行第一干法刻蚀工艺刻蚀去除衬底表面及栅极结构顶部的第一氧化层,保留位于栅极结构的侧边缘的下方的第一氧化层作为隔离物;形成金属层覆盖衬底及栅极结构的表面;以及,执行退火工艺以在衬底的表面及栅极结构的顶部形成金属硅化物,隔离物用于隔离衬底的表面的金属硅化物的至少部分侧面与衬底接触。本发明中保留栅极结构的侧边缘的下方的第一氧化层作为隔离物,在形成金属层执行退火工艺时,先金属向衬底内扩散形成金属硅化物,后衬底向金属硅化物内扩散,由于隔离物隔离衬底的表面的金属硅化物的至少部分侧面与衬底接触,使得衬底不易快速扩散至金属硅化物内以避免在衬底中形成空洞,因此能够有效防止沟道电阻增加,从而提高器件的电性能。

技术特征:

1.一种半导体器件的制备方法,其特征在于,包括:

2.如权利要求1所述的半导体器件的制备方法,其特征在于,采用热氧化工艺形成所述第一氧化层。

3.如权利要求2所述的半导体器件的制备方法,其特征在于,所述第一氧化层的厚度为80埃~100埃。

4.如权利要求3所述的半导体器件的制备方法,其特征在于,所述第一干法刻蚀工艺的刻蚀气体包括ch4和h2,ch4和h2的气体流量比包括7:3、3:2或1:1。

5.如权利要求4所述的半导体器件的制备方法,其特征在于,所述第一干法刻蚀工艺的刻蚀时间为2秒~5秒。

6.如权利要求1所述的半导体器件的制备方法,其特征在于,所述栅极结构包括栅氧化层、栅极多晶硅层及侧墙,所述栅氧化层及所述栅极多晶硅层依次堆叠于所述衬底上,所述侧墙覆盖所述栅极多晶硅层及所述栅氧化层的侧面,部分所述第一氧化层位于所述侧墙的下方。

7.如权利要求1所述的半导体器件的制备方法,其特征在于,执行所述退火工艺以在所述衬底的表面及所述栅极结构的顶部形成金属硅化物的步骤包括:

8.如权利要求7所述的半导体器件的制备方法,其特征在于,所述第一退火工艺的退火温度为400摄氏度~600摄氏度,所述第二退火工艺的退火温度大于700摄氏度。

9.如权利要求7所述的半导体器件的制备方法,其特征在于,所述金属硅化物包括硅化钴。

10.如权利要求1所述的半导体器件的制备方法,其特征在于,所述衬底包括第一区域和第二区域,所述栅极结构位于所述第一区域上,在形成第一氧化层覆盖所述衬底的表面及所述栅极结构的顶部之前,还包括:

技术总结

本发明提供了一种半导体器件的制备方法,包括:提供衬底,衬底上形成有栅极结构;形成第一氧化层覆盖衬底的表面及栅极结构的顶部,且部分第一氧化层位于栅极结构的侧边缘的下方;执行第一干法刻蚀工艺刻蚀去除衬底表面及栅极结构顶部的第一氧化层,保留位于栅极结构的侧边缘的下方的第一氧化层作为隔离物;形成金属层覆盖衬底及栅极结构的表面;以及,执行退火工艺以在衬底的表面及栅极结构的顶部形成金属硅化物,隔离物用于隔离衬底的表面的金属硅化物的至少部分侧面与衬底接触。本发明能够有效防止沟道电阻增加,从而提高器件的电性能。

技术研发人员:张振,陈世昌,张冬雪,鲍伟

受保护的技术使用者:合肥晶合集成电路股份有限公司

技术研发日:

技术公布日:2024/1/12

- 还没有人留言评论。精彩留言会获得点赞!