半导体器件及其制造方法与流程

本发明涉及一种半导体器件及其制造方法,并且特别涉及一种包括形成在沟槽中的栅极电极的半导体器件及其制造方法。

背景技术:

1、作为具有低导通电阻的igbt(绝缘栅双极晶体管),沟槽栅igbt得到了广泛的应用。

2、下面列出了公开的技术。

3、[专利文献1]日本未审查专利申请公开第2013-140885号

4、例如,专利文献1公开了具有ggee结构的igbt。在此类igbt中,在n型半导体衬底中形成沟槽,并且栅极电极被掩埋在沟槽中,其中栅极绝缘膜介于栅极电极和沟槽之间。另外,在半导体衬底中形成p型基极区域,并且在p型基极区域的上侧上形成n型发射极区域。在不同于栅极绝缘膜的绝缘膜形成在半导体衬底上的状态下,通过离子注入形成基极区域和发射极区域。

技术实现思路

1、在常规技术中,在沟槽中和半导体衬底上形成栅极绝缘膜,在栅极绝缘膜上沉积多晶硅膜,并且使多晶硅膜经受干蚀刻。因此,半导体衬底上的多晶硅膜被移除,并且多晶硅膜被埋在沟槽中作为栅极电极。当在半导体衬底上执行离子注入时,为了减小对半导体衬底的损坏,半导体衬底上的栅极绝缘膜被用作贯通膜。

2、然而,栅极绝缘膜的厚度相对较大,导致在形成栅极绝缘膜时和在多晶硅膜上进行干蚀刻时栅极绝缘膜的厚度变化。因此,如专利文献1,半导体衬底上的栅极绝缘膜被移除,并且在半导体衬底上执行再氧化处理。因此,在半导体衬底上重新形成另一个氧化硅膜是有效的。利用该新形成的氧化硅膜作为贯通膜,在半导体衬底上执行离子注入,使得在半导体衬底中形成基极区域和发射极区域。应注意的是,再氧化处理是使用氧气的热氧化处理,一般称为干氧化处理。

3、这里,根据本申请的发明人的研究,发现当执行再氧化处理时,界面状态增加,并且在栅极绝缘膜中形成氢离子,pbti(正偏压温度不稳定性)劣化。随着时间的流逝,pbti的劣化导致此类缺陷使得阈值电压的波动出现。特别地,半导体器件的可靠性降低。

4、同时,在半导体器件中,短路耐受时间(在电流流动直到集电极电流饱和的状态下,半导体器件尚未由于闩锁而损坏的时间段)被用作评估产品的指标中的一个。为了实现半导体器件的高性能,需要增加电流,但是短路耐受时间随着电流的增加而减小。在此情况下,相邻发射极区域之间的间隔更窄,并且沿着栅极电极的每个发射极区域的面积很大,使得pbti的劣化明显。

5、本申请的主要目的是实现防止由pbti劣化导致的阈值电压波动和提高短路耐受时间两者。这使得可以确保半导体器件的可靠性并且改善半导体器件的性能。根据本说明书和附图的描述,本申请的其他目的和新颖特征将变得显而易见。

6、以下将简要描述本申请中公开的实施例中的典型实施例的概要。

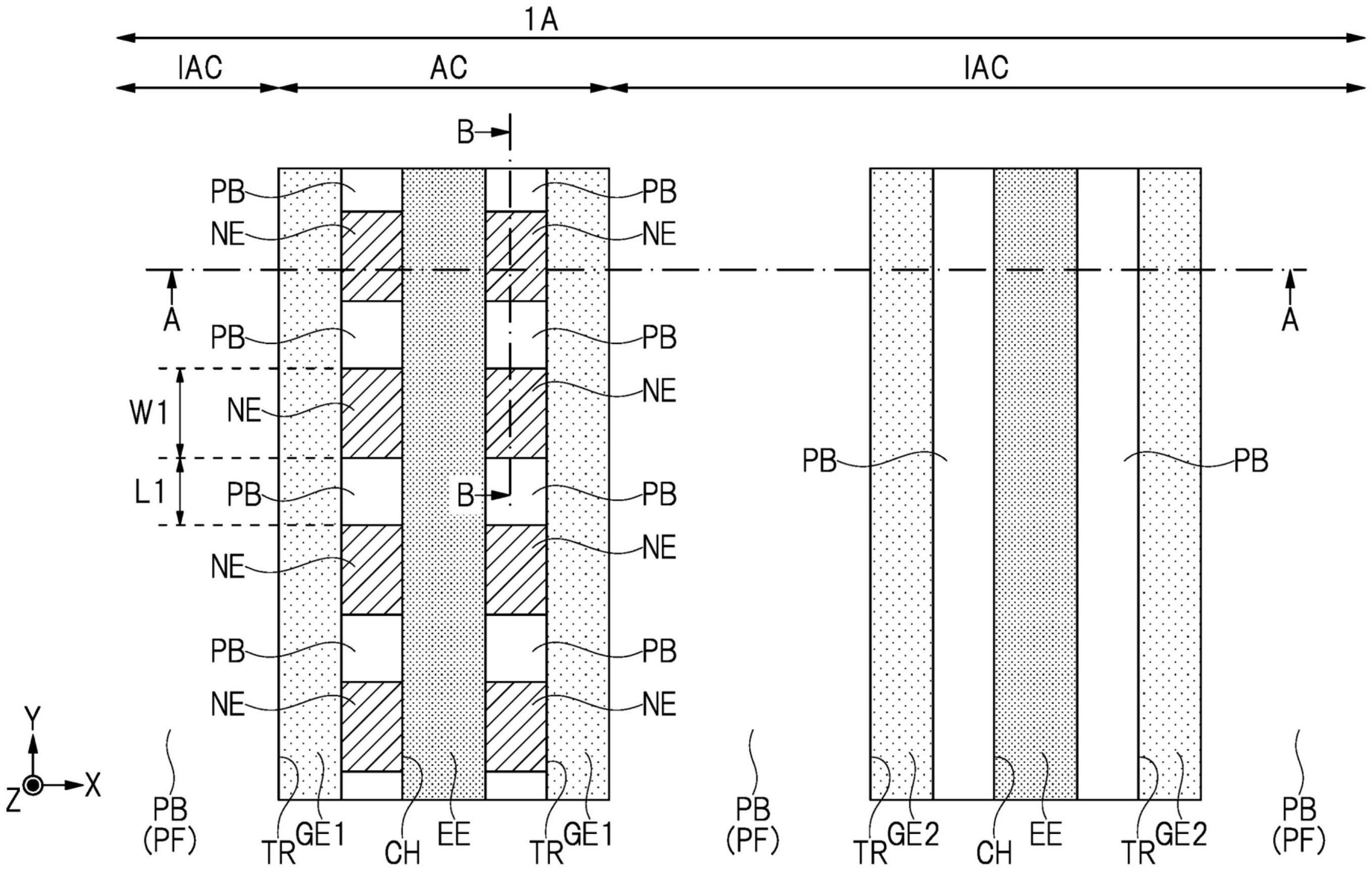

7、根据一个实施例的半导体器件包括:第一导电类型的半导体衬底;第一沟槽,形成在半导体衬底中;第一栅极绝缘膜,形成在第一沟槽中;第一栅极电极,形成在第一栅极绝缘膜上以便掩埋第一沟槽内部;第二导电类型的基极区域,该第二导电类型与第一导电类型是相反的导电类型,该基极区域形成在半导体衬底中,使得基极区域的底部部分比第一沟槽的底部部分浅;以及第一导电类型的多个发射极区域,形成在基极区域中。这里,第一沟槽在第一方向上延伸,在平面图中,多个发射极区域中的相邻发射极区域沿着第一方向彼此间隔开第一距离,多个发射极区域中的每个发射极区域在第一方向上具有第一宽度,并且第一距离比第一宽度的1/5宽并且比第一宽度窄。

8、根据一个实施例的半导体器件的制造方法包括:(a)制备第一导电类型的半导体衬底;(b)在(a)之后,在半导体衬底中形成第一沟槽;(c)在(b)之后,在第一沟槽中和半导体衬底上形成第一栅极绝缘膜;(d)在(c)之后,在第一栅极绝缘膜上形成第一导电膜以便掩埋第一沟槽的内部;(e)在(d)之后,移除形成在第一沟槽外部的第一导电膜,使得在第一沟槽中形成由第一导电膜形成的第一栅极电极;(f)在(e)之后,移除形成在半导体衬底上的第一栅极绝缘膜;(g)在(f)之后,在半导体衬底上形成第一绝缘膜;(h)在(g)之后,通过离子注入在半导体衬底中形成导电类型与第一导电类型相反的第二导电类型的基极区域,使得基极区域的底部部分比第一沟槽的底部部分浅;以及(i)在(h)之后,通过离子注入在基极区域中形成多个第一导电类型的发射极区域。这里,第一沟槽在第一方向上延伸,在平面图中,在(i)中,多个发射极区域中的相邻发射极区域被形成为在第一方向上彼此间隔开第一距离,多个发射极区域中的每个发射极区域在第一方向上具有第一宽度,并且第一距离比第一宽度的1/5宽,并且比第一宽度窄。

9、根据一个实施例,可以确保半导体器件的可靠性并且提高半导体器件的性能。

技术特征:

1.一种半导体器件,包括:

2.根据权利要求1所述的半导体器件,

3.根据权利要求1所述的半导体器件,

4.根据权利要求3所述的半导体器件,

5.根据权利要求1所述的半导体器件,包括:

6.根据权利要求1所述的半导体器件,包括:

7.根据权利要求1所述的半导体器件,包括:

8.一种半导体器件的制造方法,所述方法包括:

9.根据权利要求8所述的方法,

10.根据权利要求8所述的方法,

11.根据权利要求10所述的方法,

12.根据权利要求8所述的方法,

13.根据权利要求12所述的方法,

14.根据权利要求13所述的方法,

15.根据权利要求8所述的方法,包括:

技术总结

本公开的各实施例涉及半导体器件及其制造方法。一种半导体器件,包括n型半导体衬底、沟槽、经由栅极绝缘膜形成在该沟槽中的栅极电极、形成在该半导体衬底中的p型基极区域和形成在该基极区域中的n型发射极区域。在平面图中,该沟槽在Y方向上延伸。多个发射极区域中的相邻发射极区域被形成为沿着该Y方向彼此间隔开一段距离。该距离比该发射极区域中的每个发射极区域在Y方向上的宽度的1/5宽并且比该宽度窄。

技术研发人员:大形公士,吉田哲也,高桥幸雄

受保护的技术使用者:瑞萨电子株式会社

技术研发日:

技术公布日:2024/1/16

- 还没有人留言评论。精彩留言会获得点赞!