半导体结构的制作方法

本公开实施例涉及半导体,特别涉及一种半导体结构。

背景技术:

1、半导体集成电路可以基于数字标准单元库中的标准单元来设计。具体而言,标准单元库包含半导体集成电路设计中所需的基本逻辑单元及一些功能单元,如基本门电路、多路开关、触发器、全加器、编码器等。设计时将所需标准单元从数字标准单元库中调出,按照电路设计结果对标准单元进行排列,并对与标准单元相连接的导电层进行设计,得到所需的芯片版图,进而根据芯片版图制造所需的半导体结构。

2、在半导体集成电路的设计过程中,标准单元以及导电层设计会对半导体结构的性能产生影响。

技术实现思路

1、本公开实施例提供一种半导体结构,至少有利于提升半导体结构的电学性能。

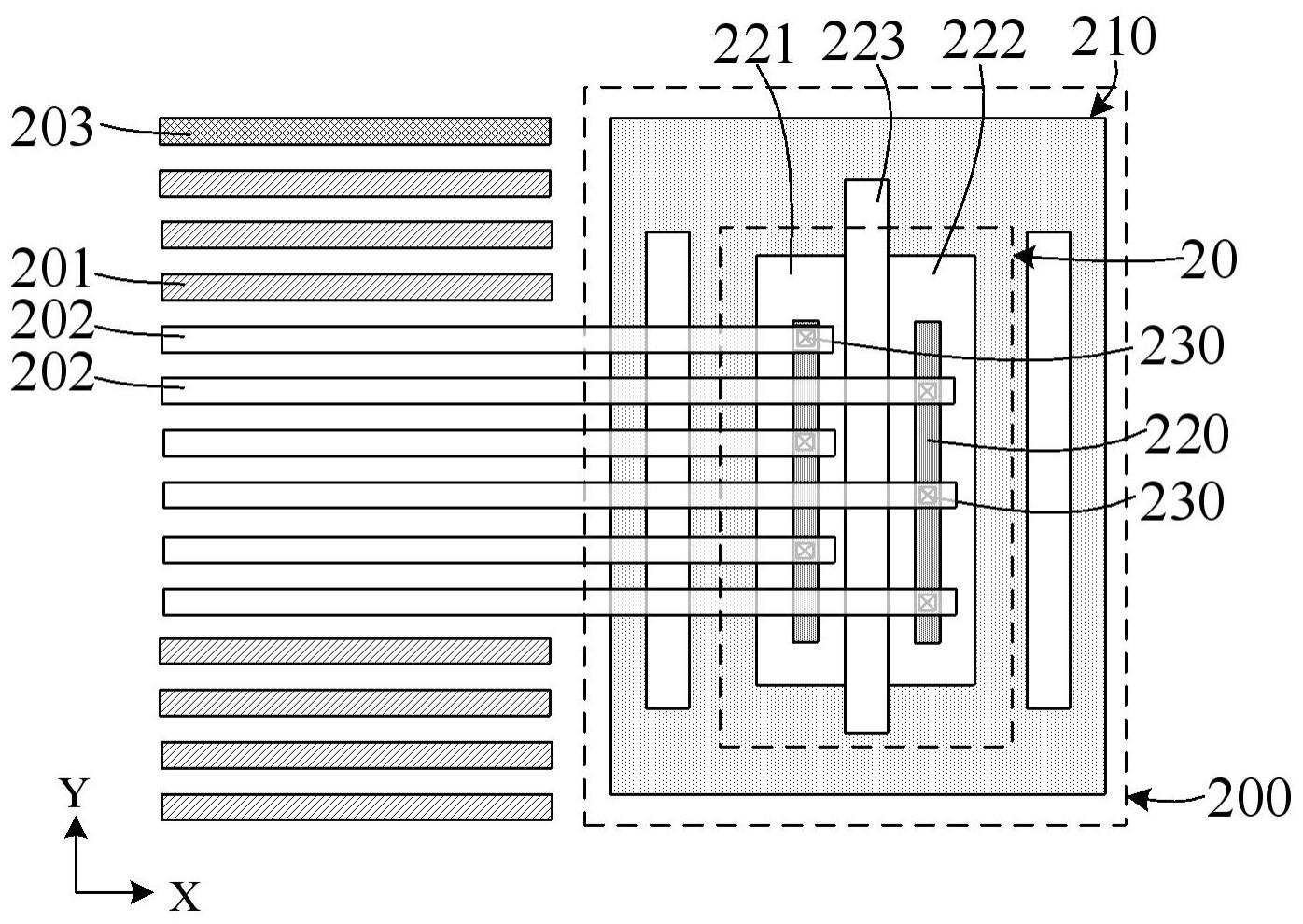

2、本公开实施例提供的半导体结构包括:标准单元,标准单元包括有源区,有源区包括沿第一方向延伸且沿第二方向排布的源区和漏区;位于标准单元上方的第一导电层,第一导电层包括沿第二方向延伸的多条电源线以及多条信号线,其中,一源区或者一漏区与多条电源线中的至少两条电源线电连接。

3、在一些实施例中,沿第一方向上,多条电源线中的每条电源线的宽度与多条信号线中的每条信号线的宽度相同。

4、在一些实施例中,还包括:沿第一方向延伸的多个导电结构,多个导电结构中的每个导电结构位于源区或者漏区上方,其中,导电结构具有对应的源区或者漏区,且不同导电结构对应的源区或者漏区不同,电源线通过导电结构与对应的源区或者漏区相连接。

5、在一些实施例中,导电结构位于中间导电层,中间导电层位于标准单元与第一导电层之间。

6、在一些实施例中,有源区包括沿第一方向排布的第一有源区和第二有源区,第一有源区用于形成第一晶体管,第二有源区用于形成第二晶体管,第一晶体管与第二晶体管的导电类型不同,沿第一方向上,与第一有源区相连接的电源线的宽度为第一宽度,与第二有源区相连接的电源线的宽度为第二宽度,第一宽度与第二宽度相同。

7、在一些实施例中,标准单元包括电源晶体管,电源晶体管的源区和漏区均连接至少两条电源线。

8、在一些实施例中,与电源晶体管的源区连接的电源线为第一电源线,与电源晶体管的漏区相连接的电源线为第二电源线,第一电源线与第二电源线沿第一方向交替排布。

9、在一些实施例中,标准单元包括逻辑晶体管,逻辑晶体管的源区或漏区连接至少两条电源线。

10、在一些实施例中,沿第一方向上,与同一源区或同一漏区相连接的至少两条电源线中,相邻的电源线之间具有至少一条信号线。

11、在一些实施例中,还包括:位于第一导电层上方的第二导电层,第二导电层包括沿第一方向延伸的多条第二走线,与同一源区或者同一漏区相连接的电源线与同一第二走线相连接。

12、在一些实施例中,标准单元包括电源晶体管,电源晶体管的源区和漏区均连接至少两条电源线,与电源晶体管的源区连接的电源线为第一电源线,与电源晶体管的漏区相连接的电源线为第二电源线,沿第二方向上,与第一电源线相连接的第二走线的宽度大于与第二电源线相连接的第二走线的宽度。

13、本公开实施例提供的技术方案至少具有以下优点:半导体结构中,通常利用走线引出标准单元中的源区或者漏区,沿第一方向上,若与同一源区或者同一漏区相连接的走线为一整条宽度较大的走线,由于宽度较大的走线会产生更大的噪声干扰,因此需要保证宽度较大的走线与相邻的其它走线之间具有较大的间隔距离。本公开实施例中,与同一源区或者同一漏区相连接的走线为相互独立的多条电源线,如此,每条电源线沿第一方向上的宽度更小,进而使得电源线与相邻的其它走线之间具有更小的间隔距离,有利于减小电源线在第一导电层中所占据的空间,提高第一导电层中的走线的数量,提高空间利用率。另外,由于电源线通过导电插塞与源区或者漏区相连接,与同一源区或者同一漏区相连接的导电插塞通常为沿第一方向间隔排布的多个导电插塞,若与同一源区或者同一漏区相连接的多个导电插塞与同一走线相连接,那么与同一源区或者同一漏区相连接的导电插塞的数量会被所连接的走线在第一方向上的宽度限制,且电源线的宽度会受到信号线的数量、信号线的位置以及其他电源线的位置的限制,因此,电源线也无法设置太宽,即导致与同一源区或者同一漏区相连接的导电插塞数量较少。本公开实施例中,由于电源线与其它走线之间具有间隔距离,不同的导电插塞与不同电源线相连接,既可利用不同走线之间的间距作为导电插塞之间的间隔,提升空间利用率,又可以缓解信号线的位置需要和数量需求造成的限制,以及缓解其他电源线位置需求造成的限制,有利于实现灵活设置并增加导电插塞的数量,进而实现利用更多数量的导电插塞将电源信号接入标准单元或其他半导体器件,从而降低导电电阻,提升半导体结构的电学性能。

技术特征:

1.一种半导体结构,其特征在于,包括:

2.根据权利要求1所述半导体结构,其特征在于,沿所述第一方向上,多条所述电源线中的每条所述电源线的宽度与多条所述信号线中的每条所述信号线的宽度相同。

3.根据权利要求1所述半导体结构,其特征在于,还包括:沿所述第一方向延伸的多个导电结构,多个所述导电结构中的每个所述导电结构位于所述源区或者所述漏区上方,其中,所述导电结构具有对应的所述源区或者所述漏区,且不同所述导电结构对应的所述源区或者所述漏区不同,所述电源线通过所述导电结构与对应的所述源区或者所述漏区相连接。

4.根据权利要求3所述半导体结构,其特征在于,所述导电结构位于中间导电层,所述中间导电层位于所述标准单元与所述第一导电层之间。

5.根据权利要求2所述半导体结构,其特征在于,所述有源区包括沿所述第一方向排布的第一有源区和第二有源区,所述第一有源区用于形成第一晶体管,所述第二有源区用于形成第二晶体管,所述第一晶体管与所述第二晶体管的导电类型不同,沿所述第一方向上,与所述第一有源区相连接的所述电源线的宽度为第一宽度,与所述第二有源区相连接的所述电源线的宽度为第二宽度,所述第一宽度与所述第二宽度相同。

6.根据权利要求1所述半导体结构,其特征在于,所述标准单元包括电源晶体管,所述电源晶体管的源区和漏区均连接至少两条所述电源线。

7.根据权利要求6所述半导体结构,其特征在于,与所述电源晶体管的源区连接的所述电源线为第一电源线,与所述电源晶体管的漏区相连接的所述电源线为第二电源线,所述第一电源线与所述第二电源线沿所述第一方向交替排布。

8.根据权利要求1所述半导体结构,其特征在于,所述标准单元包括逻辑晶体管,所述逻辑晶体管的源区或漏区连接至少两条所述电源线。

9.根据权利要求8所述半导体结构,其特征在于,沿所述第一方向上,与同一所述源区或同一所述漏区相连接的至少两条所述电源线中,相邻的电源线之间具有至少一条所述信号线。

10.根据权利要求1所述半导体结构,其特征在于,还包括:位于所述第一导电层上方的第二导电层,所述第二导电层包括沿所述第一方向延伸的多条第二走线,与同一所述源区或者同一所述漏区相连接的所述电源线与同一所述第二走线相连接。

11.根据权利要求10所述半导体结构,其特征在于,所述标准单元包括电源晶体管,所述电源晶体管的源区和漏区均连接至少两条所述电源线,与所述电源晶体管的源区连接的所述电源线为第一电源线,与所述电源晶体管的漏区相连接的所述电源线为第二电源线,沿所述第二方向上,与所述第一电源线相连接的所述第二走线的宽度大于与所述第二电源线相连接的所述第二走线的宽度。

技术总结

本公开实施例提供一种半导体结构,半导体结构包括:标准单元,标准单元包括有源区,有源区包括沿第一方向延伸且沿第二方向排布的源区和漏区;位于标准单元上方的第一导电层,第一导电层包括沿第一方向排布且沿第二方向延伸的多条电源线以及多条信号线,其中,一源区或者一漏区与多条电源线中的至少两条电源线电连接。本公开实施例至少有利于提升半导体结构的电学性能。

技术研发人员:徐静,石小庆,王晓磊,杨国琴,万利

受保护的技术使用者:长鑫存储技术有限公司

技术研发日:

技术公布日:2024/1/12

- 还没有人留言评论。精彩留言会获得点赞!