多堆叠半导体器件及其制造方法与流程

根据实施方式的装置和方法涉及三维堆叠(3d堆叠)的半导体器件或多堆叠半导体器件,其中下纳米片晶体管和上纳米片晶体管具有不同的沟道层间隔。

背景技术:

1、对具有高器件密度的集成电路的不断增长的需求已经引入了三维(3d)多堆叠半导体器件,其中垂直堆叠两个或更多个场效应晶体管,诸如纳米片晶体管。纳米片晶体管的特征在于垂直堆叠在衬底上的一个或更多个纳米片沟道层以及围绕纳米片沟道层的栅极结构。因此,纳米片晶体管被称为全环绕栅极(gaa)晶体管、多桥沟道场效应晶体管(mbcfet)。

2、在包括两个垂直堆叠的纳米片晶体管的多堆叠半导体器件中,每个纳米片晶体管的一个或更多个纳米片沟道层用作纳米片晶体管的沟道结构,并且这些沟道层被栅极结构围绕。在多堆叠半导体器件中,对于在下堆叠处的下纳米片晶体管和在上堆叠处的上纳米片晶体管中的每个,栅极结构可以包括栅极电介质层、功函数金属层和栅电极图案。

3、当需要区分下纳米片晶体管和上纳米片晶体管之间的栅极结构时,可以为两个纳米片晶体管不同地形成功函数金属层。例如,当多堆叠半导体器件要形成包括相反极性的场效应晶体管(fet)(即,p型下纳米片晶体管和n型下纳米片晶体管)的互补金属氧化物晶体管(cmos)器件时,下纳米片晶体管的栅极结构的功函数金属层(即,下栅极结构的下功函数金属层)和上纳米片晶体管的栅极结构的功函数金属层(即,上栅极结构的上功函数金属层)可以形成为包括不同的材料和/或具有不同的尺寸。因此,下栅极结构和上栅极结构可以能够具有不同的阈值电压以驱动下纳米片晶体管和上纳米片晶体管。

4、具有彼此不同的下功函数金属层和上功函数金属层的栅极结构可以通过以下来获得:形成围绕用于下纳米片晶体管和上纳米片晶体管的每个纳米片沟道层的栅极电介质层,形成围绕栅极电介质层的功函数金属层,去除在上堆叠处的纳米片沟道层上形成的功函数金属层,仅在下堆叠处的纳米片沟道层上留下功函数金属层(即,下功函数金属层),形成另一功函数金属层(即,上功函数金属层)以围绕上堆叠处的纳米片沟道层,以及形成栅电极图案以围绕这两个功函数金属层。

5、然而,形成不同功函数金属层的上述工艺暴露出各种挑战。例如,在通过湿蚀刻去除形成在上堆叠纳米片沟道层上的功函数金属层的操作期间,形成在下堆叠纳米片沟道层上的功函数金属层(即,下功函数金属层)也可能被湿蚀刻蚀刻或损坏。当下堆叠纳米片沟道层和上堆叠纳米片沟道层具有不同的沟道宽度时,这种风险可能增加。此外,由于多堆叠纳米片晶体管结构的高的高宽比以及在垂直堆叠的纳米片沟道层之间的纳米级间隔,功函数金属层及其上的栅电极图案的形成变得复杂且困难。因此,保护下功函数金属层的工艺是必要的,这常常需要额外的复杂图案化和/或沉积步骤。

6、本背景技术部分中公开的信息已为发明人在实现本申请的实施方式之前或实现过程中已知或推出,或者是在实现实施方式的过程中获得的技术信息。因此,它可能包含不构成公众已知的现有技术的信息。

技术实现思路

1、根据实施方式,本公开提供了一种多堆叠半导体器件和制造其的方法,在该多堆叠半导体器件中沟道间隔在下纳米片晶体管和上纳米片晶体管处是不同的。

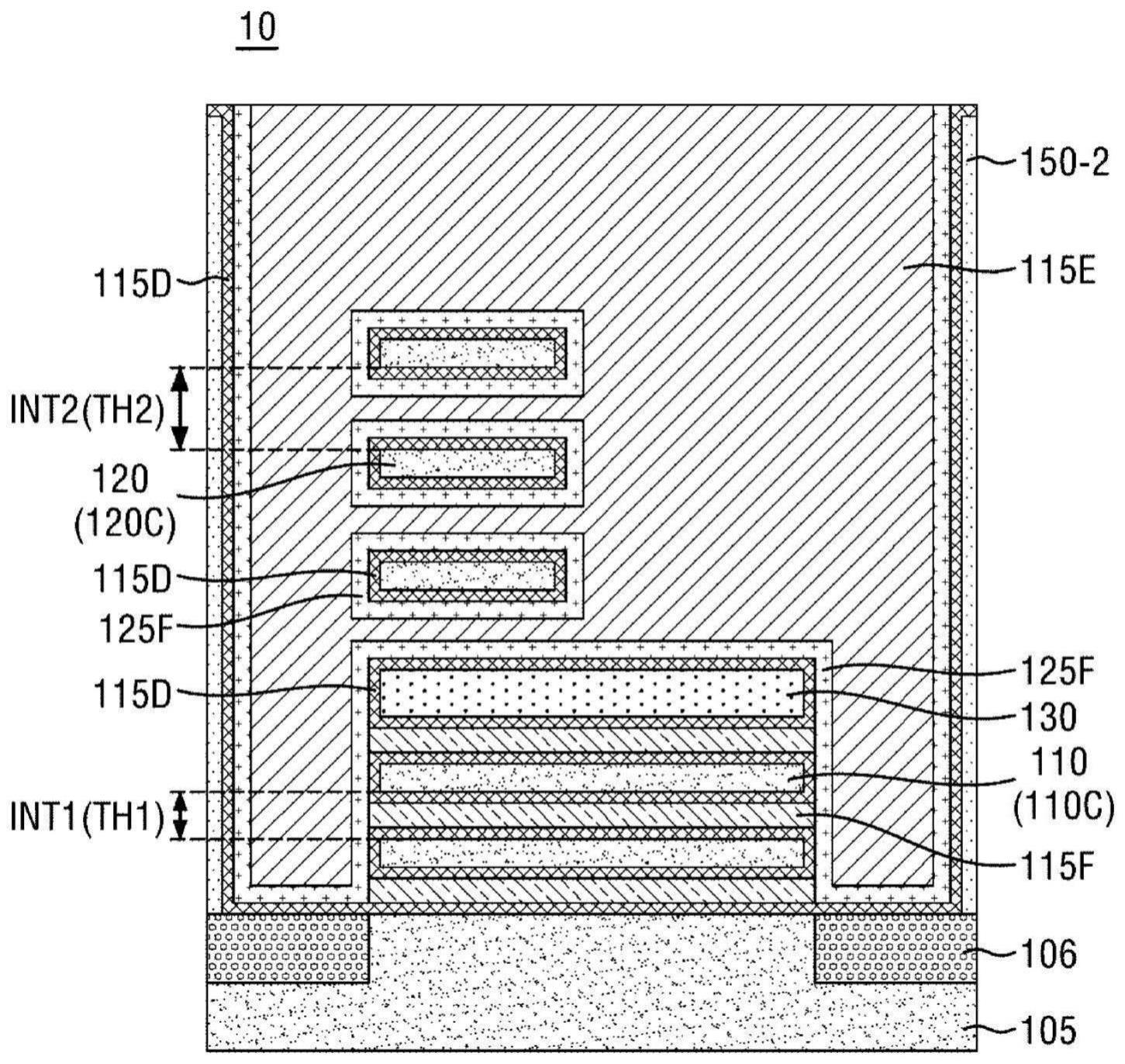

2、根据实施方式,提供了一种多堆叠半导体器件,其可以包括:下纳米片晶体管,包括被栅极结构围绕的多个下沟道层;以及上纳米片晶体管,堆叠在下纳米片晶体管上并包括被栅极结构围绕的多个上沟道层,其中下沟道层具有比上沟道层小的沟道间隔。

3、根据实施方式,提供了一种多堆叠半导体器件,其可以包括:下纳米片晶体管,包括被栅极结构围绕的多个下沟道层;以及上纳米片晶体管,堆叠在下纳米片晶体管上并包括被栅极结构围绕的多个上沟道层,其中栅极结构包括形成在下沟道层上的下功函数金属层、形成在上沟道层上的上功函数金属层、以及形成在上功函数金属层上的栅电极图案,以及其中栅电极图案形成在上沟道层之间,并且不形成在下沟道层之间。

4、根据实施方式,提供了一种多堆叠半导体器件,其可以包括:下纳米片晶体管,包括被栅极结构围绕的多个下沟道层;以及上纳米片晶体管,堆叠在下纳米片晶体管上并包括被栅极结构围绕的多个上沟道层,其中栅极结构包括形成在下沟道层上的下功函数金属层和形成在上沟道层上的上功函数金属层,上功函数金属层和下功函数金属层分别由不同的材料形成,上功函数金属层形成在下沟道层的侧表面以及下功函数金属层的形成在下沟道层之间的侧表面上。

5、根据实施方式,提供了一种多堆叠半导体器件,其可以包括:下场效应晶体管,包括被栅极结构围绕的一个或更多个下沟道层;以及上场效应晶体管,堆叠在下场效应晶体管上并包括被栅极结构围绕的一个或更多个上沟道层,其中栅极结构包括形成在下沟道层上的下功函数金属层、形成在上沟道层上的上功函数金属层、以及形成在上功函数金属层上的栅电极图案,以及其中栅电极图案形成在上沟道层之间,并且不形成在下沟道层之间。

6、根据实施方式,提供了一种制造多堆叠半导体器件的方法。该方法可以包括:提供多堆叠结构,其包括多个下沟道层和堆叠在下沟道层上的多个上沟道层,上沟道层具有比下沟道层小的沟道宽度;形成初始功函数金属层以围绕下沟道层和上沟道层;除了初始功函数金属层的在下沟道层之间的部分以外,去除初始功函数金属层,使得初始功函数金属层的所述部分形成下功函数金属层;用上功函数金属层替代被去除的初始功函数金属层,该上功函数金属层具有不包括在初始功函数金属层中的材料;以及在上功函数金属层上形成栅电极图案。

技术特征:

1.一种多堆叠半导体器件,包括:

2.根据权利要求1所述的多堆叠半导体器件,其中所述栅极结构包括:

3.根据权利要求2所述的多堆叠半导体器件,其中所述栅极结构进一步包括形成在所述上沟道层上的上功函数金属层,以及

4.根据权利要求2所述的多堆叠半导体器件,其中所述栅极结构进一步包括形成在所述上沟道层上的上功函数金属层,

5.根据权利要求4所述的多堆叠半导体器件,其中所述上功函数金属层进一步形成在所述下功函数金属层的形成在所述下沟道层之间的侧表面上。

6.根据权利要求5所述的多堆叠半导体器件,其中所述栅电极图案形成在所述上沟道层之间。

7.根据权利要求1所述的多堆叠半导体器件,其中所述上沟道层具有比所述下沟道层小的宽度。

8.根据权利要求7所述的多堆叠半导体器件,其中所述上沟道层的数量大于所述下沟道层的数量。

9.根据权利要求1所述的多堆叠半导体器件,其中所述下沟道层和所述上沟道层中的每个具有相等的厚度。

10.一种多堆叠半导体器件,包括:

11.根据权利要求10所述的多堆叠半导体器件,其中所述上功函数金属层和所述下功函数金属层分别由不同的材料形成。

12.根据权利要求10所述的多堆叠半导体器件,其中所述上功函数金属层和所述下功函数金属层分别具有不同的厚度。

13.根据权利要求10所述的多堆叠半导体器件,其中所述上功函数金属层形成在所述下沟道层的侧表面以及所述下功函数金属层的形成在所述下沟道层之间的侧表面上。

14.根据权利要求10所述的多堆叠半导体器件,其中所述下沟道层和所述上沟道层中的每个具有相等的厚度。

15.根据权利要求10所述的多堆叠半导体器件,其中所述下沟道层具有比所述上沟道层小的沟道间隔。

16.根据权利要求10所述的多堆叠半导体器件,其中所述上沟道层具有比所述下沟道层小的宽度,以及

17.一种多堆叠半导体器件,包括:

18.根据权利要求17所述的多堆叠半导体器件,其中所述上沟道层具有比所述下沟道层小的宽度。

19.根据权利要求17所述的多堆叠半导体器件,其中所述上沟道层的数量大于所述下沟道层的数量。

20.一种多堆叠半导体器件,包括:

21.根据权利要求20所述的多堆叠半导体器件,其中所述下沟道层包括垂直堆叠并水平延伸以彼此平行的多个纳米片沟道层。

22.根据权利要求21所述的多堆叠半导体器件,其中所述上功函数金属层进一步形成在所述下沟道层的侧表面以及所述下功函数金属层的形成在所述下沟道层之间的侧表面上。

23.一种制造多堆叠半导体器件的方法,所述方法包括:

24.根据权利要求23所述的方法,其中所述栅电极图案形成在所述上功函数金属层上,使得所述栅电极图案形成在所述上沟道层之间,并且所述栅电极图案不形成在所述下沟道层之间。

25.根据权利要求24所述的方法,其中被去除的所述初始功函数金属层被所述上功函数金属层替代,使得所述上功函数金属层形成在所述下沟道层的侧表面上。

26.根据权利要求23所述的方法,其中所述上沟道层具有比所述下沟道层小的宽度。

技术总结

提供了一种多堆叠半导体器件及其制造方法,该多堆叠半导体器件包括:下纳米片晶体管,包括被栅极结构围绕的多个下沟道层;以及上纳米片晶体管,堆叠在下纳米片晶体管上并包括被栅极结构围绕的多个上沟道层,其中下沟道层具有比上沟道层小的沟道间隔。

技术研发人员:曹健浩,洪炳鹤,白在职,尹承灿

受保护的技术使用者:三星电子株式会社

技术研发日:

技术公布日:2024/1/15

- 还没有人留言评论。精彩留言会获得点赞!