半导体器件的制造方法与流程

本发明涉及集成电路制造,尤其涉及一种半导体器件的制造方法。

背景技术:

1、随着半导体技术的不断发展,制造成本更低、功耗更小、速度更快的半导体器件已经成为半导体以及电子产业的普遍追求的目标之一。为了实现上述目标,需要不断缩小半导体器件的尺寸,通过提高集成度、缩小单元面积等手段在同样面积的芯片内制造更多的晶体管。

2、图1为一种mos管的剖面结构示意图。参阅图1,随着mos管(metal oxidesemiconductor field effect transistor,mosfet)的尺寸不断缩小,侧墙10的宽度也会不断缩小,源区20和漏区30与沟道之间的距离逐渐减小,从而加重了mos管的短沟道效应、dibl效应(drain induced barrier low,漏极感应势垒降低)和gidl效应(gate induceddrain leakage,栅感应漏极漏电流),导致沟道漏电增加,进而造成半导体器件的击穿电压(breakdown voltage)降低。

3、鉴于此,需要一种方法在缩短侧墙宽度的同时抑制半导体器件的短沟道效应。

技术实现思路

1、本发明的目的在于提供一种半导体器件的制造方法,在缩短侧墙宽度的同时抑制所述半导体器件的短沟道效应。

2、为了达到上述目的,本发明提供了一种半导体器件的制造方法,包括:

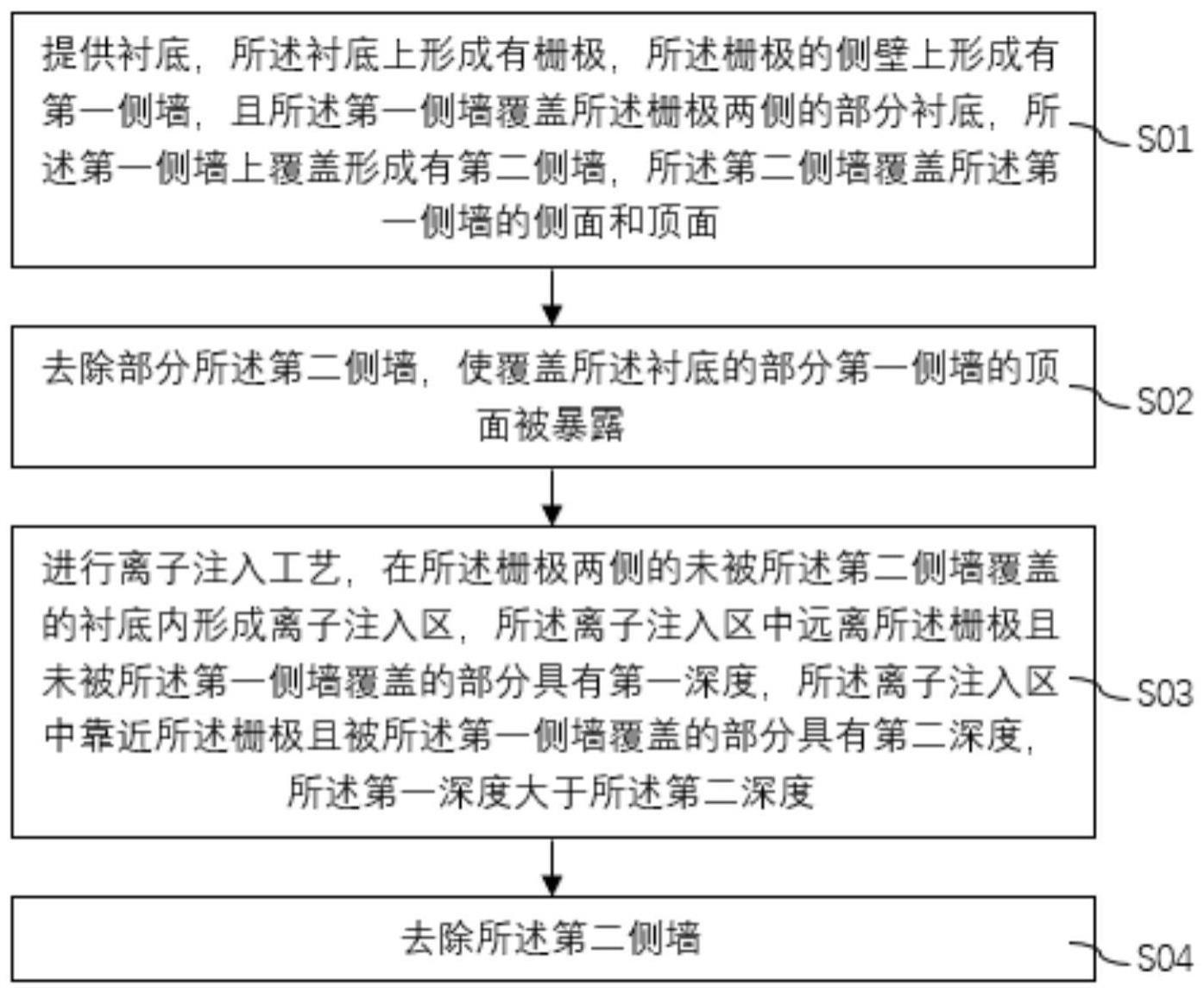

3、提供衬底,所述衬底上形成有栅极,所述栅极的侧壁上形成有第一侧墙,且所述第一侧墙覆盖所述栅极两侧的部分衬底,所述第一侧墙上形成有第二侧墙,所述第二侧墙覆盖所述第一侧墙的侧面和顶面;

4、去除部分所述第二侧墙,使覆盖所述衬底的部分第一侧墙的顶部被暴露;

5、进行离子注入工艺,在所述栅极两侧的未被所述第二侧墙覆盖的衬底内形成离子注入区,所述离子注入区中远离所述栅极且未被所述第一侧墙覆盖的部分具有第一深度,所述离子注入区中靠近所述栅极且被所述第一侧墙覆盖的部分具有第二深度,所述第一深度大于所述第二深度;以及,

6、去除所述第二侧墙。

7、可选的,在进行所述离子注入工艺之后,去除所述第二侧墙之前,还包括:

8、进行退火工艺,以修复所述离子注入工艺对所述第一侧墙和所述第二侧墙造成的损伤。

9、可选的,所述退火工艺为快速热退火工艺。

10、可选的,采用湿法刻蚀工艺去除所述第二侧墙。

11、可选的,去除所述第二侧墙的过程中,未被所述第二侧墙覆盖的部分所述第一侧墙被一同去除,使靠近所述栅极顶部的部分侧壁暴露。

12、可选的,在去除所述第二侧墙之后,还包括:

13、在所述栅极的顶部、所述栅极中暴露的部分侧壁以及未被所述第一侧墙覆盖的部分衬底上形成金属硅化物阻挡层。

14、可选的,所述第一侧墙沿垂直所述栅极的延伸方向的截面呈l型。

15、可选的,所述第一侧墙包括氧化硅层和氮化硅层,所述氧化硅层覆盖所述栅极的侧壁和部分所述衬底,所述氮化硅层形成于所述氧化硅层的表面,所述第二侧墙为氧化硅层。

16、可选的,所述离子注入的能量可穿透第一侧墙至衬底。

17、可选的,所述半导体器件的制造方法用于制造mos器件。

18、综上所述,本发明提供了一种半导体器件的制造方法,在衬底上形成栅极,所述栅极的侧壁上依次形成有第一侧墙和第二侧墙,所述第一侧墙覆盖所述栅极两侧的部分衬底,所述第二侧墙覆盖所述第一侧墙的侧面和顶面;去除部分所述第二侧墙,使覆盖所述衬底的部分第一侧墙的顶面被暴露;进行离子注入工艺,在所述栅极两侧的未被所述第二侧墙覆盖的衬底内形成离子注入区,所述离子注入区中远离所述栅极且未被所述第一侧墙覆盖的部分具有第一深度,所述离子注入区中靠近所述栅极且被所述第一侧墙覆盖的部分具有第二深度,所述第一深度大于所述第二深度;以及,去除所述第二侧墙。本发明通过控制第一侧墙和第二侧墙的形貌来改变离子注入区中不同部分的深度,使离子注入区中靠近栅极的部分的第二深度小于所述离子注入区中远离栅极的部分的第一深度,从而在缩短侧墙宽度的同时抑制所述半导体器件的短沟道效应,以便在不影响器件性能的前提下缩小半导体器件的器件尺寸。

技术特征:

1.一种半导体器件的制造方法,其特征在于,包括:

2.如权利要求1所述的半导体器件的制造方法,其特征在于,在进行所述离子注入工艺之后,去除所述第二侧墙之前,还包括:

3.如权利要求2所述的半导体器件的制造方法,其特征在于,所述退火工艺为快速热退火工艺。

4.如权利要求1所述的半导体器件的制造方法,其特征在于,采用湿法刻蚀工艺去除所述第二侧墙。

5.如权利要求1或4所述的半导体器件的制造方法,其特征在于,去除所述第二侧墙的过程中,未被所述第二侧墙覆盖的部分所述第一侧墙被一同去除,使靠近所述栅极顶部的部分侧壁暴露。

6.如权利要求5所述的半导体器件的制造方法,其特征在于,在去除所述第二侧墙之后,还包括:

7.如权利要求1所述的半导体器件的制造方法,其特征在于,所述第一侧墙沿垂直所述栅极的延伸方向的截面呈l型。

8.如权利要求1或7所述的半导体器件的制造方法,其特征在于,所述第一侧墙包括氧化硅层和氮化硅层,所述氧化硅层覆盖所述栅极的侧壁和部分所述衬底,所述氮化硅层形成于所述氧化硅层的表面,所述第二侧墙为氧化硅层。

9.如权利要求1所述的半导体器件的制造方法,其特征在于,所述离子注入的能量可穿透第一侧墙至衬底。

10.如权利要求1所述的半导体器件的制造方法,其特征在于,所述半导体器件的制造方法用于制造mos器件。

技术总结

本发明提供了一种半导体器件的制造方法,在衬底上形成栅极,栅极侧壁上依次形成有第一侧墙和第二侧墙,第一侧墙覆盖栅极两侧的部分衬底,第二侧墙覆盖第一侧墙的侧面和顶面;去除部分第二侧墙,使覆盖衬底的部分第一侧墙的顶面被暴露;在栅极两侧未被第二侧墙覆盖的衬底内形成离子注入区,离子注入区中远离栅极且未被第一侧墙覆盖的部分具有第一深度,靠近栅极且被第一侧墙覆盖的部分具有第二深度,第一深度大于第二深度;去除第二侧墙。本发明使离子注入区中靠近栅极部分的第二深度小于离子注入区中远离栅极的部分的第一深度,缩短了侧墙宽度,抑制了半导体器件的短沟道效应,在不影响器件性能的前提下缩小了半导体器件的器件尺寸。

技术研发人员:于涛,岑贵

受保护的技术使用者:上海华虹宏力半导体制造有限公司

技术研发日:

技术公布日:2024/1/13

- 还没有人留言评论。精彩留言会获得点赞!