半导体结构及其形成方法与流程

本申请涉及半导体,尤其涉及一种半导体结构及其形成方法。

背景技术:

1、具有沟槽栅极结构的碳化硅器件(sic mosfet with trench gate)有望从硅igbt(insulated gate bipolar transistor)转换而来。然而,目前的沟槽栅极结构由于沟槽栅极结构绝缘体的底部拐角(bottom corner)电场强度更高,是栅极泄漏和击穿的薄弱点,沟槽栅极结构底部的四个拐角非常脆弱。

2、因此,有必要提供更有效、更可靠的技术方案,保护沟槽栅极结构底部的四个拐角,提高器件可靠性。

技术实现思路

1、本申请提供一种半导体结构及其形成方法,可以保护沟槽栅极结构底部的四个拐角,提高器件可靠性。

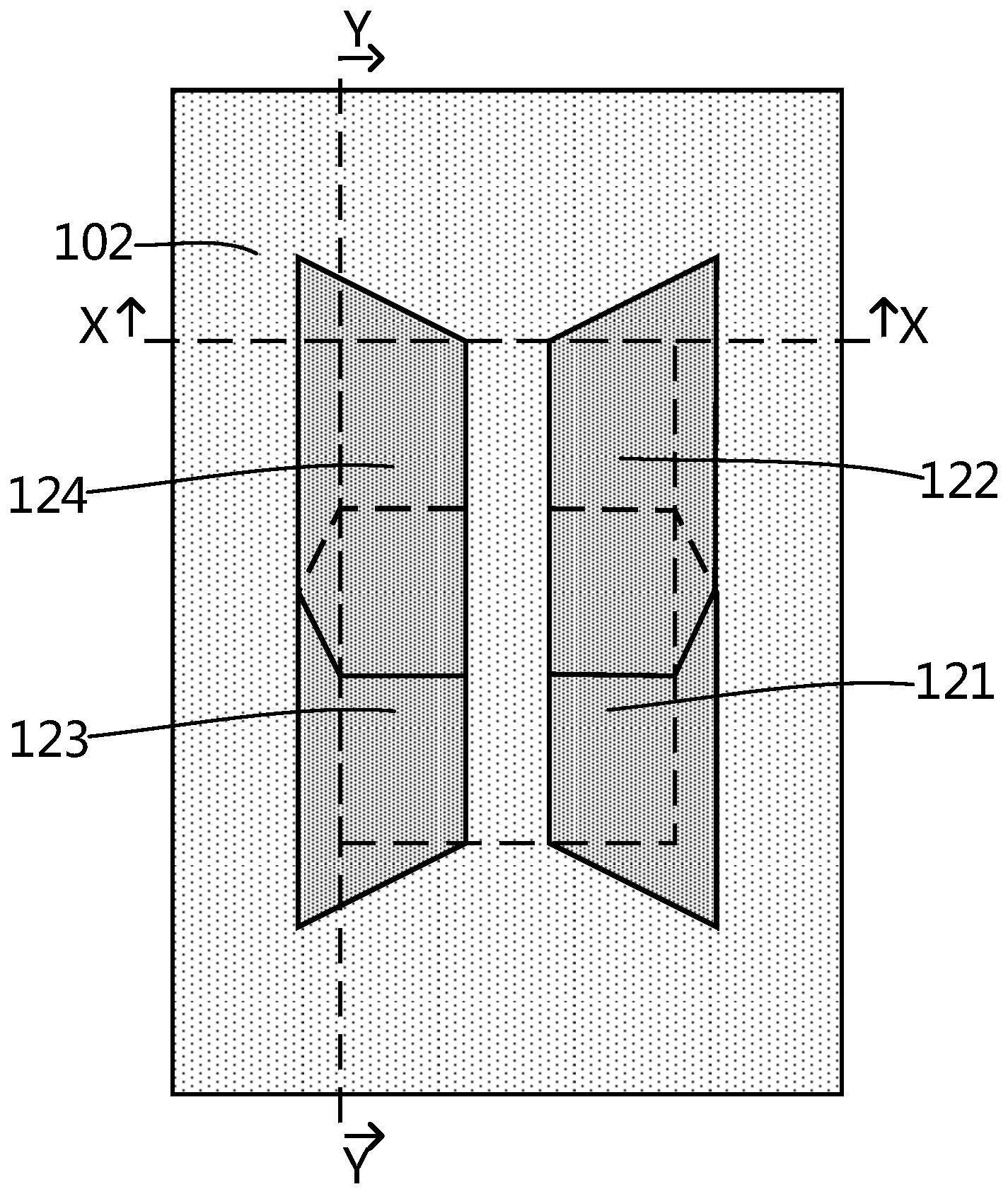

2、本申请的一个方面提供一种半导体结构的形成方法,包括:提供基底,所述基底包括半导体衬底以及位于所述半导体衬底表面的外延层,所述外延层中包括用于形成沟槽栅极结构的栅极区域,所述栅极区域包括相对的第一面和第三面以及相对的第二面和第四面;执行第一离子注入工艺,形成从邻接所述第一面和第二面的部分栅极区域向所述第一面和第二面倾斜并包覆所述第一面和第二面底部相交处的第一拐角的第一离子注入区;执行第二离子注入工艺,形成从邻接所述第一面和第四面的部分栅极区域向所述第一面和第四面倾斜并包覆所述第一面和第四面底部相交处的第二拐角的第二离子注入区;执行第三离子注入工艺,形成从邻接所述第三面和第二面的部分栅极区域向所述第三面和第二面倾斜并包覆所述第三面和第二面底部相交处的第三拐角的第三离子注入区;执行第四离子注入工艺,形成从邻接所述第三面和第四面的部分栅极区域向所述第三面和第四面倾斜并包覆所述第三面和第四面底部相交处的第四拐角的第四离子注入区。

3、在本申请的一些实施例中,所述第一离子注入工艺包括:向第一面倾斜10至30度;向第二面倾斜10至60度;离子注入浓度为1e13atom/cm3至3e13atom/cm3。

4、在本申请的一些实施例中,所述第二离子注入工艺包括:向第一面倾斜10至30度;向第四面倾斜10至60度;离子注入浓度为1e13atom/cm3至3e13atom/cm3。

5、在本申请的一些实施例中,所述第三离子注入工艺包括:向第三面倾斜10至30度;向第二面倾斜10至60度;离子注入浓度为1e13atom/cm3至3e13atom/cm3。

6、在本申请的一些实施例中,所述第四离子注入工艺包括:向第三面倾斜10至30度;向第四面倾斜10至60度;离子注入浓度为1e13atom/cm3至3e13atom/cm3。

7、在本申请的一些实施例中,所述第一离子注入区和第二离子注入区部分重合使得所述第一离子注入区和第二离子注入区穿过整个第一面;所述第三离子注入区和第四离子注入区部分重合使得所述第三离子注入区和第四离子注入区穿过整个第三面。

8、在本申请的一些实施例中,所述半导体结构的形成方法还包括:对所述第一离子注入区、第二离子注入区、第三离子注入区和第四离子注入区执行退火工艺,使所述第一离子注入区和第二离子注入区的注入离子浓度分布均匀以及使所述第三离子注入区和第四离子注入区的注入离子浓度分布均匀。

9、本申请的另一个方面还提供一种半导体结构,包括:基底,所述基底包括半导体衬底以及位于所述半导体衬底表面的外延层,所述外延层中包括用于形成沟槽栅极结构的栅极区域,所述栅极区域包括相对的第一面和第三面以及相对的第二面和第四面;第一离子注入区,从邻接所述第一面和第二面的部分栅极区域向所述第一面和第二面倾斜并包覆所述第一面和第二面底部相交处的第一拐角;第二离子注入区,从邻接所述第一面和第四面的部分栅极区域向所述第一面和第四面倾斜并包覆所述第一面和第四面底部相交处的第二拐角;第三离子注入区,从邻接所述第三面和第二面的部分栅极区域向所述第三面和第二面倾斜并包覆所述第三面和第二面底部相交处的第三拐角;第四离子注入区,从邻接所述第三面和第四面的部分栅极区域向所述第三面和第四面倾斜并包覆所述第三面和第四面底部相交处的第四拐角。

10、在本申请的一些实施例中,所述第一离子注入区向第一面倾斜10至30度;所述第一离子注入区向第二面倾斜10至60度;所述第一离子注入区的离子注入浓度为1e13atom/cm3至3e13atom/cm3。

11、在本申请的一些实施例中,所述第二离子注入区向第一面倾斜10至30度;所述第二离子注入区向第四面倾斜10至60度;所述第二离子注入区的离子注入浓度为1e13atom/cm3至3e13atom/cm3。

12、在本申请的一些实施例中,所述第三离子注入区向第三面倾斜10至30度;所述第三离子注入区向第二面倾斜10至60度;所述第三离子注入区的离子注入浓度为1e13atom/cm3至3e13atom/cm3。

13、在本申请的一些实施例中,所述第四离子注入区向第三面倾斜10至30度;所述第四离子注入区向第四面倾斜10至60度;所述第四离子注入区的离子注入浓度为1e13atom/cm3至3e13atom/cm3。

14、在本申请的一些实施例中,所述第一离子注入区和第二离子注入区部分重合使得所述第一离子注入区和第二离子注入区穿过整个第一面;所述第三离子注入区和第四离子注入区部分重合使得所述第三离子注入区和第四离子注入区穿过整个第三面。

15、在本申请的一些实施例中,所述第一离子注入区和第二离子注入区的注入离子浓度分布均匀;所述第三离子注入区和第四离子注入区的注入离子浓度分布均匀。

16、本申请提供一种半导体结构及其形成方法,利用第一离子注入区、第二离子注入区、第三离子注入区和第四离子注入区分别包住沟槽栅极结构底部的四个拐角,可以保护沟槽栅极结构底部的四个拐角,避免发生泄漏和击穿,从而提高器件可靠性。

技术特征:

1.一种半导体结构的形成方法,其特征在于,包括:

2.如权利要求1所述的半导体结构的形成方法,其特征在于,所述第一离子注入工艺包括:向第一面倾斜10至30度;向第二面倾斜10至60度;离子注入浓度为1e13atom/cm3至3e13atom/cm3。

3.如权利要求1所述的半导体结构的形成方法,其特征在于,所述第二离子注入工艺包括:向第一面倾斜10至30度;向第四面倾斜10至60度;离子注入浓度为1e13atom/cm3至3e13atom/cm3。

4.如权利要求1所述的半导体结构的形成方法,其特征在于,所述第三离子注入工艺包括:向第三面倾斜10至30度;向第二面倾斜10至60度;离子注入浓度为1e13atom/cm3至3e13atom/cm3。

5.如权利要求1所述的半导体结构的形成方法,其特征在于,所述第四离子注入工艺包括:向第三面倾斜10至30度;向第四面倾斜10至60度;离子注入浓度为1e13atom/cm3至3e13atom/cm3。

6.如权利要求1所述的半导体结构的形成方法,其特征在于,所述第一离子注入区和第二离子注入区部分重合使得所述第一离子注入区和第二离子注入区穿过整个第一面;所述第三离子注入区和第四离子注入区部分重合使得所述第三离子注入区和第四离子注入区穿过整个第三面。

7.如权利要求6所述的半导体结构的形成方法,其特征在于,还包括:对所述第一离子注入区、第二离子注入区、第三离子注入区和第四离子注入区执行退火工艺,使所述第一离子注入区和第二离子注入区的注入离子浓度分布均匀以及使所述第三离子注入区和第四离子注入区的注入离子浓度分布均匀。

8.一种半导体结构,其特征在于,包括:

9.如权利要求8所述的半导体结构,其特征在于,所述第一离子注入区向第一面倾斜10至30度;所述第一离子注入区向第二面倾斜10至60度;所述第一离子注入区的离子注入浓度为1e13atom/cm3至3e13atom/cm3。

10.如权利要求8所述的半导体结构,其特征在于,所述第二离子注入区向第一面倾斜10至30度;所述第二离子注入区向第四面倾斜10至60度;所述第二离子注入区的离子注入浓度为1e13atom/cm3至3e13atom/cm3。

11.如权利要求8所述的半导体结构,其特征在于,所述第三离子注入区向第三面倾斜10至30度;所述第三离子注入区向第二面倾斜10至60度;所述第三离子注入区的离子注入浓度为1e13atom/cm3至3e13atom/cm3。

12.如权利要求8所述的半导体结构,其特征在于,所述第四离子注入区向第三面倾斜10至30度;所述第四离子注入区向第四面倾斜10至60度;所述第四离子注入区的离子注入浓度为1e13atom/cm3至3e13atom/cm3。

13.如权利要求1所述的半导体结构,其特征在于,所述第一离子注入区和第二离子注入区部分重合使得所述第一离子注入区和第二离子注入区穿过整个第一面;所述第三离子注入区和第四离子注入区部分重合使得所述第三离子注入区和第四离子注入区穿过整个第三面。

14.如权利要求13所述的半导体结构,其特征在于,所述第一离子注入区和第二离子注入区的注入离子浓度分布均匀;所述第三离子注入区和第四离子注入区的注入离子浓度分布均匀。

技术总结

本申请提供半导体结构及其形成方法,所述半导体结构包括:基底,所述基底包括用于形成沟槽栅极结构的栅极区域;第一离子注入区,包覆所述栅极区域的第一拐角;第二离子注入区,包覆所述栅极区域的第二拐角;第三离子注入区,包覆所述栅极区域的第三拐角;第四离子注入区,包覆所述栅极区域的第四拐角。本申请提供一种半导体结构及其形成方法,利用第一离子注入区、第二离子注入区、第三离子注入区和第四离子注入区分别包住沟槽栅极结构底部的四个拐角,可以保护沟槽栅极结构底部的四个拐角,避免发生泄漏和击穿,从而提高器件可靠性。

技术研发人员:三重野文健,周永昌

受保护的技术使用者:飞锃半导体(上海)有限公司

技术研发日:

技术公布日:2024/1/15

- 还没有人留言评论。精彩留言会获得点赞!