一种带保护结构的氮化镓JFET的制备方法

本发明属于半导体材料,尤其涉及一种带保护结构的氮化镓jfet的制备方法。

背景技术:

1、第三代半导体材料的氮化镓是制备功率器件的重要半导体材料,它具有更大的禁带宽度和更高的击穿电场,可制造出高耐压、大电流和高稳定性的器件。

2、gan材料制成的jfet,因其优异的性能,引起了人们高度重视和广泛应用,但由于其本身容易因为外加电压过大而导致栅极损坏或者在高速开关状态下栅极被击穿等原因,器件的可靠性研究有待加强。

技术实现思路

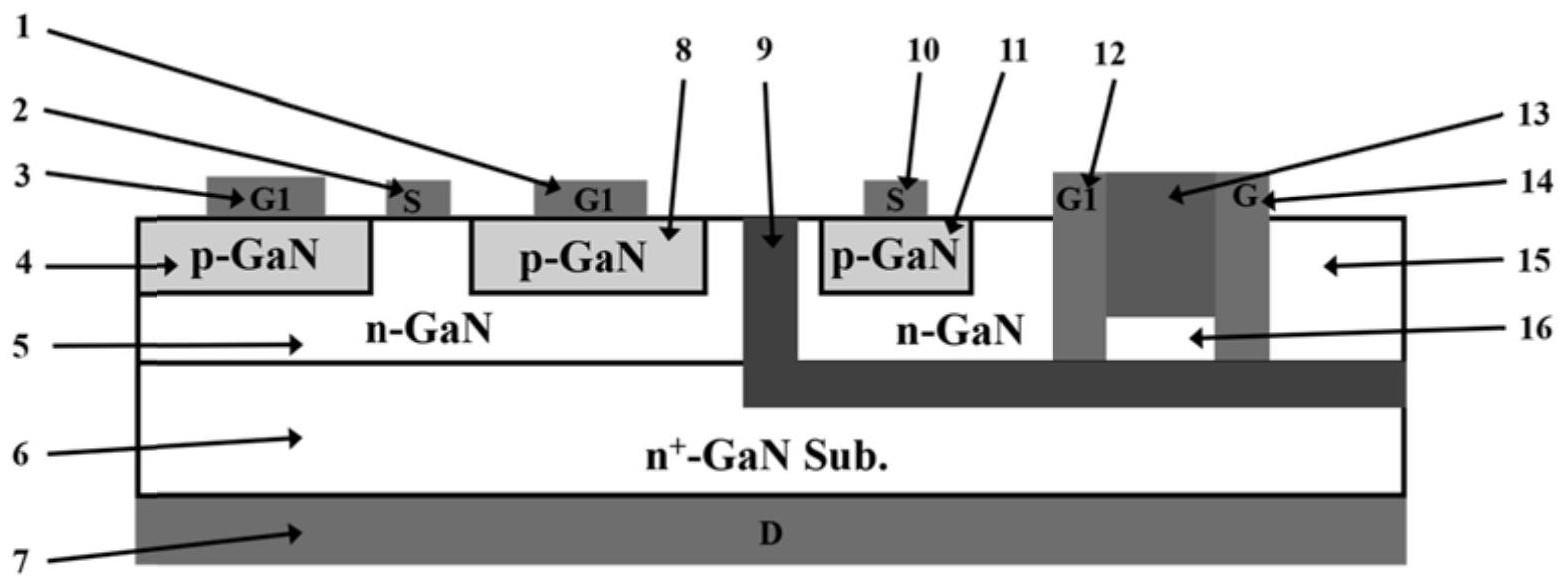

1、本发明实施例提供一种带保护结构的氮化镓jfet的制备方法,包括:

2、在n型氮化镓单晶衬底表面制作阻挡层,在器件一侧的区域利用he离子注入的方式形成第一高阻区,并在器件表面生长n型氮化镓外延层;

3、制作阻挡层,通过镁离子注入的方式在n型氮化镓外延层的另一侧区域制备jfet的第一p阱区和第二p阱区,在第一高阻区的一侧区域制备保护结构中二极管的p型区,快速热退火;

4、制作阻挡层,并利用he离子注入方式在第二p阱区和保护结构中二极管的p型区之间制备第二高阻区以使第二高阻区和第一高阻区联通形成jfet和保护结构的隔离带;

5、制作阻挡层在保护结构中二极管的p型区的一侧利用he离子注入方式在器件表面形成第三高阻区作为保护结构中电容极板之间的介质层,制作阻挡层,对第三高阻区的两边刻蚀形成两个凹槽,其中,第三高阻区与第一高阻区之间形成保护结构中并联的电阻;

6、光刻后,在第三高阻区的两个凹槽内沉积铜得到欧姆接触栅极,光刻后在第一p阱区和第二p阱区表面蒸镀金属膜制备栅极,在保护结构中二极管的p型区的表面蒸镀金属膜制备源极,在第一p阱区和第二p阱区的中间区域制备源极,在器件底部n型氮化镓单晶衬底的背面蒸镀金属膜制备漏极。

7、进一步地,第一高阻区的厚度为1-3μm。

8、进一步地,通过金属有机化学气相沉积在器件表面生长n型氮化镓外延层的掺杂浓度为1x1016 cm-3-5x1016 cm-3。

9、进一步地,第二高阻区的宽度为300nm-800nm。

10、进一步地,第三高阻区的宽度为1-3μm,厚度为5-15μm。

11、进一步地,凹槽的宽度为160nm-300nm,深度为15-25μm。

12、进一步地,氮化镓单晶衬底,厚度为200-400μm。

13、进一步地,通过镁离子注入时,镁离子的掺杂浓度为镁的掺杂浓度约为1x1018 cm-3-4x1018 cm-3。

14、进一步地,栅极铜的厚度为8-12μm。

15、进一步地,源极和漏极为ti/al/ni/au。

16、本发明实施例的有益效果是:本发明提出了一种带有保护结构的氮化镓jfet,在原有氮化镓jfet的基础上再集成了保护电路,其优势是:(1)无需在芯片外部连接保护电路,可以显著减小pcb板的大小。(2)芯片内部的保护电路能提高器件可靠性,更好地应用在高频、高压等工作模式下。

技术特征:

1.一种带保护结构的氮化镓jfet的制备方法,其特征在于,包括:

2.根据权利要求1所述的制备方法,其特征在于,第一高阻区的厚度为1-3μm。

3.根据权利要求1所述的制备方法,其特征在于,通过金属有机化学气相沉积在器件表面生长n型氮化镓外延层的掺杂浓度为1x1016 cm-3-5x1016 cm-3。

4.根据权利要求1所述的制备方法,其特征在于,第二高阻区的宽度为300nm-800nm。

5.根据权利要求1所述的制备方法,其特征在于,第三高阻区的宽度为1-3μm,厚度为5-15μm。

6.根据权利要求1所述的制备方法,其特征在于,凹槽的宽度为160nm-300nm,深度为15-25μm。

7.根据权利要求1所述的制备方法,其特征在于,氮化镓单晶衬底,厚度为200-400μm。

8.根据权利要求1所述的制备方法,其特征在于,通过镁离子注入时,镁离子的掺杂浓度为镁的掺杂浓度约为1x1018 cm-3-4x1018 cm-3。

9.根据权利要求1所述的制备方法,其特征在于,栅极铜的厚度为8-12μm。

10.根据权利要求1所述的制备方法,其特征在于,源极和漏极为ti/al/ni/au。

技术总结

本发明公开一种带保护结构的氮化镓JFET的制备方法,包括:在氮化镓一侧区域注入He离子形成第一高阻区,生长外延层;在氮化镓的另一侧区域注入镁离子制备JFET的第一P阱区和第二P阱区,在第一高阻区的区域制备保护结构中二极管的P型区;用He离子注入方式在第二P阱区和保护结构中二极管的P型区之间制备第二高阻区;在保护结构中二极管的P型区的一侧的器件表面注入He离子形成第三高阻区作为保护结构中电容极板之间的介质层,对第三高阻区的两边刻蚀形成两个凹槽;在第三高阻区的两个凹槽内沉积铜得到栅极,在第一P阱区和第二P阱区表面蒸镀金属膜制备栅极,在保护结构中二极管的P型区的表面蒸镀金属膜制备源极,在第一P阱区和第二P阱区的中间区域制备源极,在氮化镓背面蒸镀金属膜制备漏极。

技术研发人员:刘新科,月文,陈增发,黎晓华,黄双武,贺威

受保护的技术使用者:深圳大学

技术研发日:

技术公布日:2024/1/13

- 还没有人留言评论。精彩留言会获得点赞!