一种半导体器件及其制造方法

本发明涉及半导体,尤其涉及一种半导体器件及其制造方法。

背景技术:

1、三维叠层互补晶体管包括垂直堆叠的n型晶体管和p型晶体管,消除了n型晶体管和p型晶体管的横向间距,其允许进一步增大有效沟道宽度,从而利于提升半导体器件的工作性能和集成度。

2、但是,当三维叠层互补晶体管中位于上部的晶体管为p型环栅晶体管、且p型环栅晶体管包括的半导体基底和沟道区内均含有锗时,采用现有的制造方法所制造的该三维叠层互补晶体管的工作性能不佳。

技术实现思路

1、本发明的目的在于提供一种半导体器件及其制造方法,用于在三维叠层互补晶体管中位于上部的晶体管为p型环栅晶体管、且p型环栅晶体管包括的半导体基底和沟道区内均含有锗的情况下,提高该三维叠层互补晶体管的工作性能。

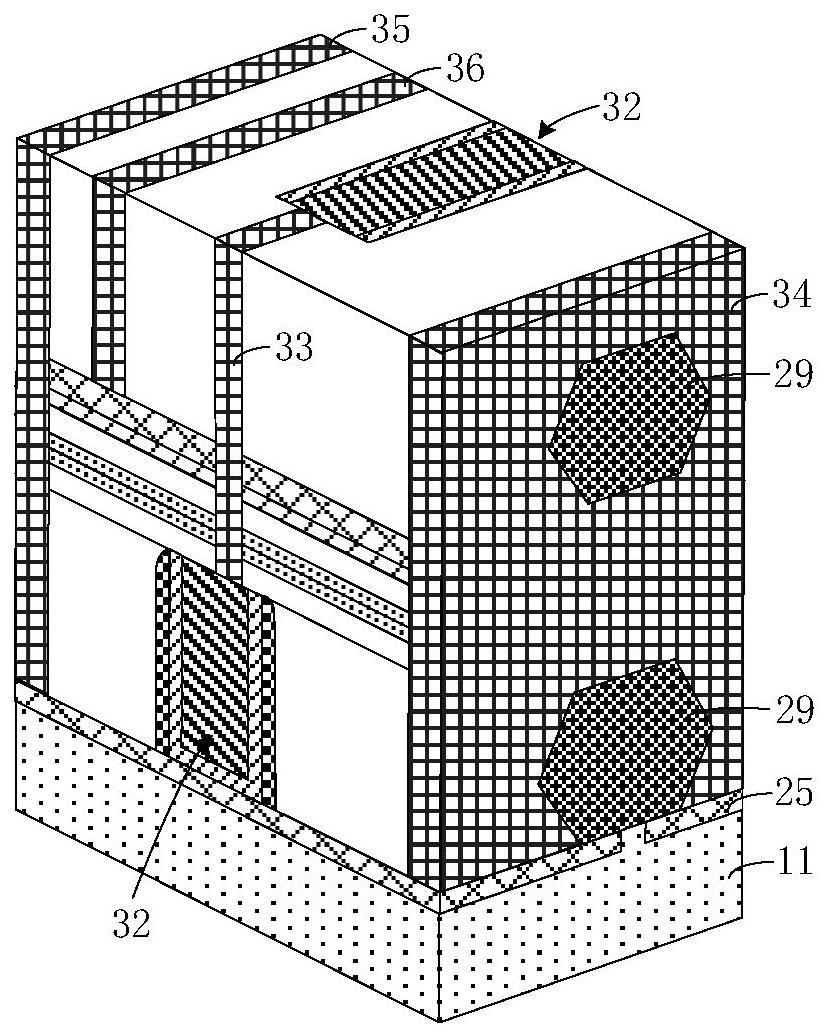

2、为了实现上述目的,第一方面,本发明提供了一种半导体器件,该半导体器件包括:第一半导体基底、n型环栅晶体管、第二半导体基底、键合互连层和p型环栅晶体管。

3、上述n型环栅晶体管形成在第一半导体基底上。第二半导体基底形成在n型环栅晶体管的上方。键合互连层位于n型环栅晶体管和第二半导体基底之间。键合互连层的材料包括三氧化二钇,第二半导体基底和n型环栅晶体管通过键合互连层键合。p型环栅晶体管形成在第二半导体基底上。第二半导体基底和p型环栅晶体管包括的沟道区内均含有锗。

4、采用上述技术方案的情况下,沿第一半导体基底的厚度方向,键合互连层和第二半导体基底依次形成n型环栅晶体管上。并且,p型环栅晶体管位于第二半导体基底上,因此p型环栅晶体管位于n型环栅晶体管上。同时,因p型环栅晶体管和n型环栅晶体挂的导电类型相反,故n型环栅晶体管和p型环栅晶体管构成三维叠层互补晶体管。在此情况下,与硅材料相比,锗硅或锗等含锗半导体材料具有更高的载流子迁移率,因此在p型环栅晶体管包括的沟道区内含有锗的情况下,可以提高p型环栅晶体管包括的沟道区内的载流子迁移率,提升p型环栅晶体管的驱动性能。并且,p型环栅晶体管形成在第二半导体基底上,该第二半导体基底内也含有锗,此时第二半导体基底的材料和p型环栅晶体管包括的沟道区的材料相同或相近,可以降低二者之间的失配度,提高p型环栅晶体管包括的沟道区的形成质量,进一步提高p型环栅晶体管的工作性能。

5、其次,位于n型环栅晶体管和第二半导体基底之间的键合互连层,其材料包括三氧化二钇,以通过三氧化二钇实现n型环栅晶体管和第二半导体基底低温键合在一起,防止键合温度较高而影响第二半导体基底的晶体质量(例如:在第二半导体基底的材料为锗的情况下,第二半导体基底在较高的键合环境中容易被氧化等),进而提高形成在第二半导体基底上的p型环栅晶体管的晶体质量。另外,本发明提供的半导体器件是通过键合的方式在已形成的n型环栅晶体管上形成第二半导体基底,并在第二半导体基底上形成p型环栅晶体管。其中,单独形成n型环栅晶体管和p型环栅晶体管时的结构纵横与制造常规环栅晶体管的纵横比相同,无须像现有单片(monolithic)集成方式需要对制造n型环栅晶体管和p型环栅晶体管的相应膜层同时进行处理而导致操作的垂直纵横比较大,进而降低三维叠层互补晶体管的制造难度。

6、第二方面,本发明还提供了一种半导体器件的制造方法,该半导体器件的制造方法包括:首先,提供第一半导体基底和第二半导体基底。接下来,在第一半导体基底上依次形成n型环栅晶体管和第一键合互连子层。第一键合互连子层的材料包括三氧化二钇。接下来,在第二半导体基底的一侧形成第二键合互连子层。第二键合互连子层的材料包括三氧化二钇。接下来,采用低温键合工艺,通过第一键合互连子层和第二键合互连子层将n型环栅晶体管和第二半导体基底键合在一起,并形成键合互连层。键合互连层包括第一键合互连子层和第二键合互连子层。接下来,在第二半导体基底上形成p型环栅晶体管。第二半导体基底和p型环栅晶体管包括的沟道区内均含有锗。

7、本发明中第二方面及其各种实现方式的有益效果,可以参考第一方面及其各种实现方式中的有益效果分析,此处不赘述。

技术特征:

1.一种半导体器件,其特征在于,包括:第一半导体基底,

2.根据权利要求1所述的半导体器件,其特征在于,沿所述第二半导体基底的厚度方向,所述键合互连层包括三氧化二钇层、以及位于所述三氧化二钇层两侧的二氧化硅层。

3.根据权利要求2所述的半导体器件,其特征在于,所述键合互连层的厚度大于等于20nm、且小于等于100nm;和/或,

4.根据权利要求1所述的半导体器件,其特征在于,所述n型环栅晶体管和所述p型环栅晶体管包括的沟道区的材料均为单晶半导体材料。

5.根据权利要求1所述的半导体器件,其特征在于,所述n型环栅晶体管包括的沟道区的晶向为[100]晶向;所述p型环栅晶体管包括的沟道区的晶向为[110]晶向。

6.根据权利要求1~5任一项所述的半导体器件,其特征在于,所述第二半导体基底和所述p型环栅晶体管包括的沟道区内锗的含量均大于等于50%、且小于等于100%;和/或,

7.一种半导体器件的制造方法,其特征在于,包括:

8.根据权利要求7所述的半导体器件的制造方法,其特征在于,所述低温键合工艺的键合温度大于等于50℃、且小于等于150℃。

9.根据权利要求7所述的半导体器件的制造方法,其特征在于,所述提供第一半导体基底和第二半导体基底前,所述半导体器件的制造方法还包括:在硅基半导体衬底上依次形成缓冲层和所述第二半导体基底;

10.根据权利要求9所述的半导体器件的制造方法,其特征在于,在硅基半导体衬底上形成缓冲层后,并在形成所述第二半导体基底前,所述半导体器件的制造方法还包括:在所述缓冲层上形成刻蚀停止层;所述刻蚀停止层的材料不同于所述第二半导体基底的材料;

11.根据权利要求9或10所述的半导体器件的制造方法,其特征在于,采用外延工艺,并依次在高温环境和低温环境下形成所述缓冲层;其中,所述高温环境下的温度大于等于600℃,所述低温环境下的温度大于等于400℃、且小于等于500℃。

12.根据权利要求7~11任一项所述的半导体器件的制造方法,其特征在于,提供第二半导体基底后,所述在所述第二半导体基底的一侧形成第二键合互连子层前,所述半导体器件的制造方法还包括:对所述第二半导体基底对应所述第二键合互连子层的一侧进行平坦化处理。

技术总结

本发明公开一种半导体器件及其制造方法,涉及半导体技术领域,以在三维叠层互补晶体管中位于上部的晶体管为P型环栅晶体管、且P型环栅晶体管包括的半导体基底和沟道区内含有锗时,提高三维叠层互补晶体管的工作性能。所述半导体器件包括:第一半导体基底、N型环栅晶体管、第二半导体基底、键合互连层和P型环栅晶体管。N型环栅晶体管形成在第一半导体基底上。第二半导体基底形成在N型环栅晶体管上方。键合互连层位于N型环栅晶体管和第二半导体基底之间。键合互连层的材料包括三氧化二钇,第二半导体基底和N型环栅晶体管通过键合互连层键合。P型环栅晶体管形成在第二半导体基底上。第二半导体基底和P型环栅晶体管包括的沟道区内均含有锗。

技术研发人员:李永亮,刘昊炎,罗军,王文武

受保护的技术使用者:中国科学院微电子研究所

技术研发日:

技术公布日:2024/1/14

- 还没有人留言评论。精彩留言会获得点赞!