具有可堆叠的基于金属的加热器和传感器的热测试芯片的制作方法

背景技术:

1、电子系统的开发包括各种任务和阶段,比如开发具有部件和规格列表的物料清单(bom)、集成电路芯片设计、设计系统封装形式和材料以及一个或多个印刷电路板(pcb)的布局和设计。系统设计与开发中的重要考虑因素是热性能,特别是对于需要在宽温度范围内工作的工业或汽车应用的系统设计。热性能会影响包括电路芯片、电路板、模塑料和封装结构在内的各种系统部件的设计和物料选择。系统开发中的重大障碍是评估各种部件和设计选择的热性能,这会导致开发时间延长和成本扩大。用于评估集成电路或其他封装电子器件在工作时的热性能(比如瞬态结温(例如,θja))的常规技术通常不可扩展且不是技术不可知的。

技术实现思路

1、在一个方面,一种电子器件包括封装结构、部分地暴露在封装结构外的导电引线、以及具有半导体层和多层级金属化结构的半导体管芯,其中半导体管芯被封装结构围封,并且多层级金属化结构包括加热电阻器、感测电阻器、以及电耦合到加热电阻器和感测电阻器的相应端子的导电金属特征,其中导电金属特征电耦合到导电引线中的相应导电引线。

2、在另一个方面,一种制造电子器件的方法包括:在半导体层上方形成多层级金属化结构的第一金属化层级,第一金属化层级包括第一加热电阻器;在第一层金属化层级上方形成多层级金属化结构的第二金属化层级,第二金属化层级包括第二加热电阻器,并且第一金属化层级和第二金属化层级中的一个包括感测电阻器;将第一加热电阻器和第二加热电阻器电耦合到导电引线;以及将第一金属化层级和第二金属化层级、半导体层、以及导电引线的部分围封在封装结构中。

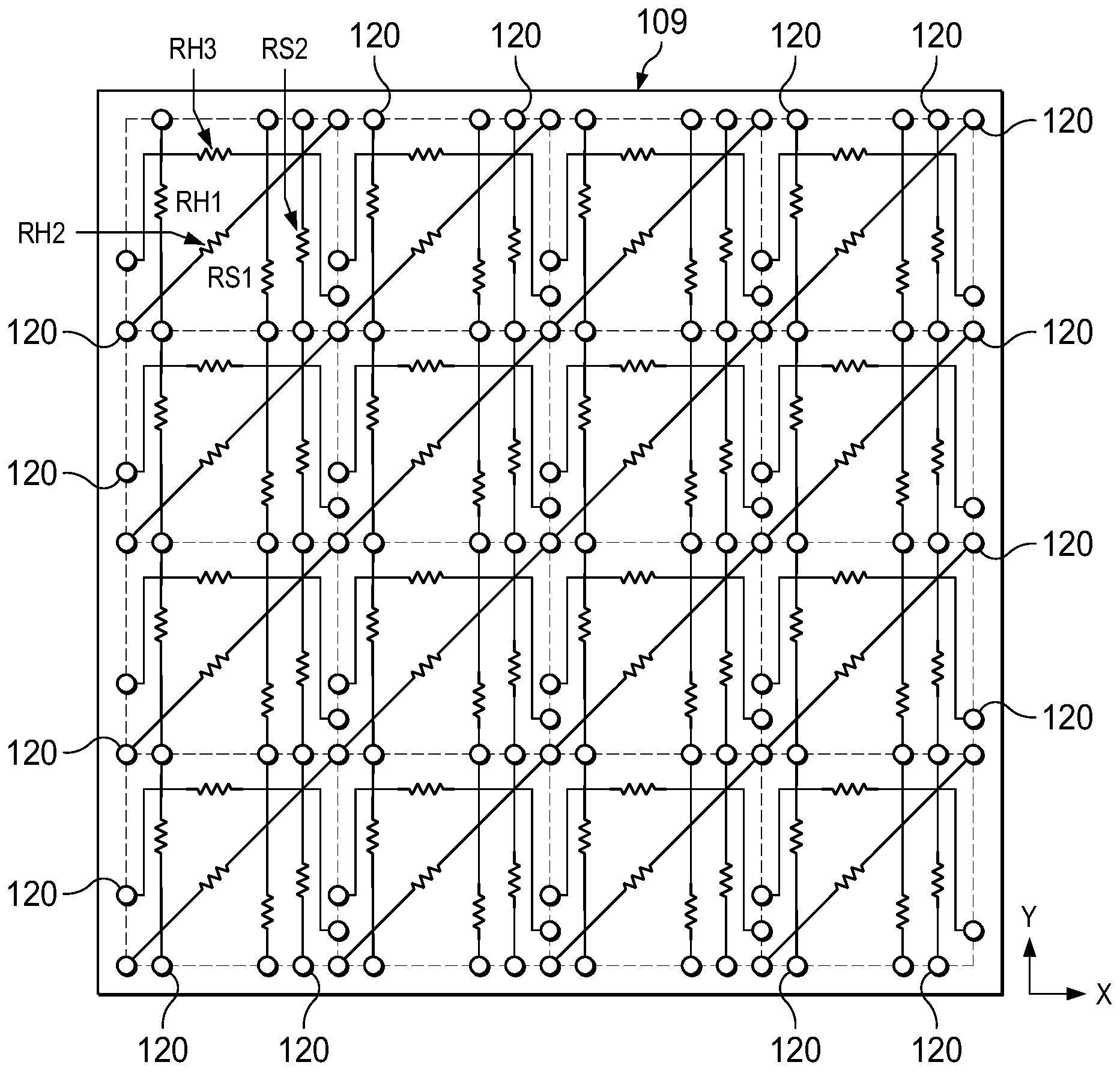

3、在另外的方面,一种系统包括电路板、电子器件、电源电路、感测电路和开关电路。电子器件包括部分地暴露在封装结构外并连接到电路板的导电特征的导电引线、以及具有半导体层和多层级金属化结构的半导体管芯。多层级金属化结构包括加热电阻器、感测电阻器、成行和成列布置的单元区域的阵列,每个单元区域包括第一加热电阻器的实例、第二加热电阻器的实例、以及感测电阻器的实例、以及电耦合到加热电阻器和感测电阻器的相应端子的导电金属特征,其中导电金属特征电耦合到导电引线中的相应导电引线。电源电路被配置为提供电流以激活加热电阻器中的选定加热电阻器,并且感测电路被配置为感测感测电阻器中的选定感测电阻器的信号。开关电路耦合在电路板、电源电路与感测电路之间,并且开关电路被配置为选择性地将电源电路耦合到加热电阻器中的选定加热电阻器以及选择性地将感测电路耦合到感测电阻器中的选定感测电阻器,以测试电路板的热性能。

技术特征:

1.一种电子器件,包括:

2.如权利要求1所述的电子器件,其中,所述多层级金属化结构包括沿第一方向成行布置且沿正交的第二方向成列布置的单元区域的阵列,每个单元区域包括所述加热电阻器的实例和所述感测电阻器的实例。

3.如权利要求2所述的电子器件,其中:

4.如权利要求3所述的电子器件,其中,所述多层级金属化结构的每个单元区域包括所述感测电阻器的实例和第二感测电阻器的实例。

5.如权利要求3所述的电子器件,其中,所述多层级金属化结构包括一组串联电路,所述一组串联电路包括沿所述阵列的列或行的相应单元区域中的所述加热电阻器的所述实例,每个相应串联电路包括电耦合到所述相应串联电路的所述加热电阻器的所述实例的端部端子的一对所述导电金属特征。

6.如权利要求5所述的电子器件,其中,所述多层级金属化结构包括一组第二串联电路,所述一组第二串联电路包括沿所述阵列的对角线方向的相应单元区域中的所述第二加热电阻器的所述实例中的至少一个,每个相应第二串联电路包括电耦合到所述相应第二串联电路的所述第二加热电阻器的所述实例的端部端子的第二对所述导电金属特征。

7.如权利要求3所述的电子器件,其中,所述多层级金属化结构包括一组串联电路,所述一组串联电路包括沿所述阵列的对角线方向的相应单元区域中的所述第二加热电阻器的所述实例中的至少一个,所述串联电路中的每个串联电路包括电耦合到相应串联电路的所述第二加热电阻器的所述实例的端部端子的一对所述导电金属特征。

8.如权利要求1所述的电子器件,其中:

9.如权利要求1所述的电子器件,其中,所述多层级金属化结构包括第二感测电阻器。

10.一种制造电子器件的方法,所述方法包括:

11.如权利要求10所述的方法,其中,将所述第一加热电阻器和所述第二加热电阻器电耦合到导电引线包括在所述多层级金属化结构的导电金属特征与所述导电引线中的相应导电引线之间形成键合线。

12.如权利要求10所述的方法,其中,将所述第一加热电阻器和所述第二加热电阻器电耦合到导电引线包括将所述多层级金属化结构的导电金属特征焊接到封装衬底。

13.如权利要求10所述的方法,其中,形成所述第一金属化层级和所述第二金属化层级包括形成沿第一方向成行布置且沿正交的第二方向成列布置的单元区域的阵列,每个单元区域包括所述第一加热电阻器的实例、所述第二加热电阻器的实例、以及所述感测电阻器的实例。

14.如权利要求13所述的方法,其中,形成所述第一金属化层级和所述第二金属化层级包括形成一组串联电路,所述一组串联电路包括沿所述阵列的列或行的相应单元区域中的所述加热电阻器的所述实例,每个相应串联电路包括电耦合到所述相应串联电路的所述加热电阻器的所述实例的端部端子的一对所述导电金属特征。

15.如权利要求14所述的方法,其中,形成所述第一金属化层级和所述第二金属化层级包括形成一组第二串联电路,所述一组第二串联电路包括沿所述阵列的对角线方向的相应单元区域中的所述第二加热电阻器的所述实例中的至少一个,每个相应第二串联电路包括电耦合到所述相应第二串联电路的所述第二加热电阻器的所述实例中的至少一个的端部端子的第二对所述导电金属特征。

16.一种系统,包括:

17.如权利要求16所述的系统,其中:

18.如权利要求17所述的系统,其中:

19.如权利要求16所述的系统,其中:

20.一种方法,包括:

21.如权利要求20所述的方法,其中:

技术总结

本申请题为“具有可堆叠的基于金属的加热器和传感器的热测试芯片”。一种电子器件,所述电子器件包括封装结构、部分地暴露在封装结构外的导电引线、以及具有半导体层和多层级金属化结构的半导体,其中半导体被封装结构围封,并且多层级金属化结构包括加热电阻器、感测电阻器、以及电耦合到加热电阻器和感测电阻器的相应端子的导电金属特征,其中导电金属特征电耦合到导电引线中的相应导电引线。

技术研发人员:V·拉伊,A·维诺戈帕,B·特拉维斯

受保护的技术使用者:德克萨斯仪器股份有限公司

技术研发日:

技术公布日:2024/1/16

- 还没有人留言评论。精彩留言会获得点赞!