屏蔽栅沟槽SGT-MOSFET半导体器件的制备方法与流程

本发明涉及于半导体功率器件,具体为屏蔽栅沟槽sgt-mosfet半导体器件的制备方法。

背景技术:

1、具有屏蔽栅沟槽(shield gate trench,sgt)结构的功率mosfet器件是目前最先进的功率mosfet器件技术,能够同时实现低导通电阻和低反向恢复电容,从而同时降低了系统的导通损耗和开关损耗,提高了系统使用效率。

2、传统屏蔽栅沟槽结构为在栅极多晶硅下方设置源极多晶硅,这种结构造成沟槽内源极多晶硅中部的电场值相比于两端较低,这种不均匀随着沟槽深度加大而愈发严重,使屏蔽栅沟槽mosfet的应用范围受到限制。

技术实现思路

1、针对现有技术的不足,本发明提供了屏蔽栅沟槽sgt-mosfet半导体器件的制备方法,解决了传统屏蔽栅沟槽在栅极多晶硅下方设置源极多晶硅的结构,造成的沟槽内源极多晶硅中部的电场值相比于两端较低,不均匀随着沟槽深度加大而愈发严重,使屏蔽栅沟槽mosfet的应用范围受到限制的问题。

2、为实现以上目的,本发明通过以下技术方案予以实现:

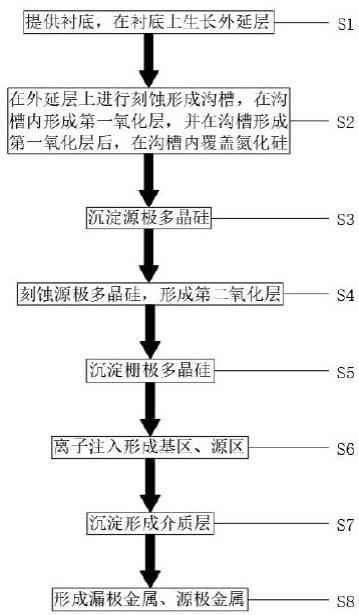

3、屏蔽栅沟槽sgt-mosfet半导体器件的制备方法,包括以下步骤:

4、s1:提供衬底,在衬底上生长外延层;

5、s2:在外延层上进行刻蚀形成沟槽,在沟槽内形成第一氧化层,并在沟槽形成第一氧化层后,在沟槽内覆盖氮化硅;

6、s3:沉淀源极多晶硅;

7、s4:刻蚀源极多晶硅,形成第二氧化层;

8、s5:沉淀栅极多晶硅;

9、s6:离子注入形成基区、源区;

10、s7:沉淀形成介质层;

11、s8:形成漏极金属、源极金属。

12、优选的,在步骤s2中,在外延层上通过光刻刻蚀工艺进行刻蚀形成沟槽;

13、在步骤s2中,通过化学机械抛光装置对氮化硅进行抛光,使第一氧化层露出。

14、优选的,在步骤s3中,通过多晶硅沉积工艺沉淀源极多晶硅。

15、优选的,在步骤s4中,采用干法刻蚀工艺对源极多晶硅进行刻蚀。

16、优选的,在步骤s5中,采用高密度等离子体化学气相淀积工艺沉淀栅极多晶硅。

17、优选的,化学机械抛光装置包括抛光平面,抛光平面用于固定氮化硅所在的晶圆;

18、抛光平面边侧固定连接有支撑架,支撑架顶端固定连接有顶板,顶板下表面通过高低调节件连接有固定板。

19、优选的,固定板下表面转动连接有第二齿轮,第二齿轮的内圈与外圈均设置有齿;

20、固定板侧壁固定连接有电机,电机输出端固定连接有第一齿轮,第一齿轮与第二齿轮外圈的齿啮合;

21、第二齿轮内转动连接有往复丝杠、滑杆,往复丝杠、滑杆上连接有固定盒,固定盒内转动连接有滑块,滑块与往复丝杠的凹槽滑动连接,固定盒与滑杆滑动连接;

22、固定板下表面固定连接有内齿轮,往复丝杠上固定连接有第一齿板,第一齿板与内齿轮啮合。

23、优选的,固定板下表面转动连接有第一转轴,第一转轴上固定连接有第三齿轮、第一带轮,第三齿轮与第二齿轮内圈的齿啮合,第一带轮通过皮带与第二带轮、调节带轮连接;

24、调节带轮转动连接于调节杆一端,调节杆另一端滑动连接于调节套筒内,且调节杆与调节套筒之间设置有第一弹簧,第一弹簧固定连接于调节杆、调节套筒;

25、第二带轮固定连接于第二转轴,第二转轴贯穿固定盒插接于驱动管,第二转轴与驱动管的插接截面为非圆形,驱动管转动连接于固定盒。

26、优选的,驱动管外侧固定连接有开合套筒,开合套筒与化学药剂仓连通,开合套筒与驱动管的连接处设置有开孔,开合套筒内滑动连接有开合密封件,且开合密封件抵接于开合套筒与驱动管连接处的开孔,开合密封件与开合套筒之间设置有第二弹簧,第二弹簧与开合密封件、开合套筒固定连接。

27、优选的,驱动管下侧设置有抛光头,抛光头与驱动管之间设置有伸缩套筒,伸缩套筒转动连接于驱动管、抛光头,伸缩套筒外套接有第三弹簧,第三弹簧两端抵接于驱动管、抛光头,抛光头上通过固定件连接有抛光垫。

28、相比现有技术,本发明至少包括以下有益效果:

29、在传统屏蔽栅沟槽的栅极多晶硅下方设置源极多晶硅结构的基础上,对源极多晶硅与沟槽之间加设氮化硅,高介电常数的氮化硅的增加使得沟槽内各部分之间的电场强度更为均匀,解决了传统屏蔽栅沟槽在栅极多晶硅下方设置源极多晶硅的结构,造成的沟槽内源极多晶硅中部的电场值相比于两端较低,不均匀随着沟槽深度加大而愈发严重,使屏蔽栅沟槽mosfet的应用范围受到限制的问题。

技术特征:

1.屏蔽栅沟槽sgt-mosfet半导体器件的制备方法,其特征在于:包括以下步骤:

2.根据权利要求1所述的屏蔽栅沟槽sgt-mosfet半导体器件的制备方法,其特征在于:

3.根据权利要求1所述的屏蔽栅沟槽sgt-mosfet半导体器件的制备方法,其特征在于:

4.根据权利要求1所述的屏蔽栅沟槽sgt-mosfet半导体器件的制备方法,其特征在于:

5.根据权利要求1所述的屏蔽栅沟槽sgt-mosfet半导体器件的制备方法,其特征在于:

6.根据权利要求2所述的屏蔽栅沟槽sgt-mosfet半导体器件的制备方法,其特征在于:

7.根据权利要求6所述的屏蔽栅沟槽sgt-mosfet半导体器件的制备方法,其特征在于:

8.根据权利要求7所述的屏蔽栅沟槽sgt-mosfet半导体器件的制备方法,其特征在于:

9.根据权利要求8所述的屏蔽栅沟槽sgt-mosfet半导体器件的制备方法,其特征在于:

10.根据权利要求9所述的屏蔽栅沟槽sgt-mosfet半导体器件的制备方法,其特征在于:

技术总结

本发明公开了屏蔽栅沟槽SGT‑MOSFET半导体器件的制备方法,包括以下步骤:提供衬底,在衬底上生长外延层;在外延层上进行刻蚀形成沟槽,在沟槽内形成第一氧化层,并在沟槽形成第一氧化层后,在沟槽内覆盖氮化硅;沉淀源极多晶硅;刻蚀源极多晶硅,形成第二氧化层;沉淀栅极多晶硅;离子注入形成基区、源区;沉淀形成介质层;形成漏极金属、源极金属。在源极多晶硅与沟槽之间加设氮化硅,高介电常数的氮化硅的增加使得沟槽内各部分之间的电场强度更为均匀,解决了传统屏蔽栅沟槽MOSFET的应用范围受到限制的问题。

技术研发人员:马奕俊,张小龙,马奕鸿

受保护的技术使用者:深圳辰达行电子有限公司

技术研发日:

技术公布日:2024/1/13

- 还没有人留言评论。精彩留言会获得点赞!