绝缘体上硅类型的半导体器件和相应的制造方法与流程

实施例和实现方式涉及绝缘体上硅类型的半导体器件和相应的方法。

背景技术:

1、soi衬底允许特别受益于“反向偏置(back bias)”,即由载体衬底的偏置引起的穿过掩埋介电层的半导体膜中的场效应。实际上,它是位于载体衬底中的局部偏置的掺杂阱。在soi技术中产生的mos晶体管(“金属氧化物半导体”的首字母缩写)的沟道区位于半导体膜中,使得反向偏置允许改变mos晶体管的行为。

2、通常,pmos晶体管的负号和nmos晶体管的正号的反向偏置,称为前向(forward)反向偏置,允许降低晶体管的阈值电压并因此改善它们的性能,但增加电流泄漏;虽然pmos晶体管的正号和nmos晶体管的负号的反向偏置(称为逆向(reverse)反向偏置)允许增加晶体管的阈值电压并因此减少电流泄漏,但使其性能劣化(deteriorates)。

3、此外,pmos和nmos晶体管通常在具有各自掺杂类型的载体衬底的阱中产生,或者在“正常阱(regular well)”的配置中产生,其中pmos晶体管在n型阱中产生并且nmos晶体管在p型阱中产生(也就是说,以在单片衬底“体”中产生mos晶体管的方式);在“倒装阱(flipwell)”的配置中,pmos晶体管在p型阱中制造,nmos晶体管在n型阱中制造(由于soi衬底的掩埋介电层,这是可能的)。

4、因此,在反向偏置的情况下,p型阱和n型阱之间的电位差受阱之间形成的pn结的阈值电压限制,使得正常阱的配置不允许(或太少而不可用)前向反向偏置,且翻转阱配置不允许(或太少而不可用)逆向反向偏置。

5、正常阱与翻转阱的共同集成不是有利的,特别是在表面占用方面,因为在这种情况下,相同类型的晶体管(nmos或pmos)必须在分开的阱中制造并电隔离。

6、使用额外横向隔离沟槽且比典型横向隔离沟槽深的用于电隔离n型和p型外壳的技术允许前向和逆向反向偏置,但产生额外制造步骤,所述额外制造步骤在制造半导体器件方面昂贵且复杂,且还在电路设计方面产生额外复杂性。

7、实施例和实现方式允许前向和逆向反向偏置,对于nmos晶体管和pmos晶体管,前向和逆向反向偏置可以在大于阱之间的pn结的阈值电压的值处被使用,相同类型的晶体管(nmos或pmos)都能够共同集成在载体衬底的相同阱中,而不会在电路的制造和设计中产生复杂性。

技术实现思路

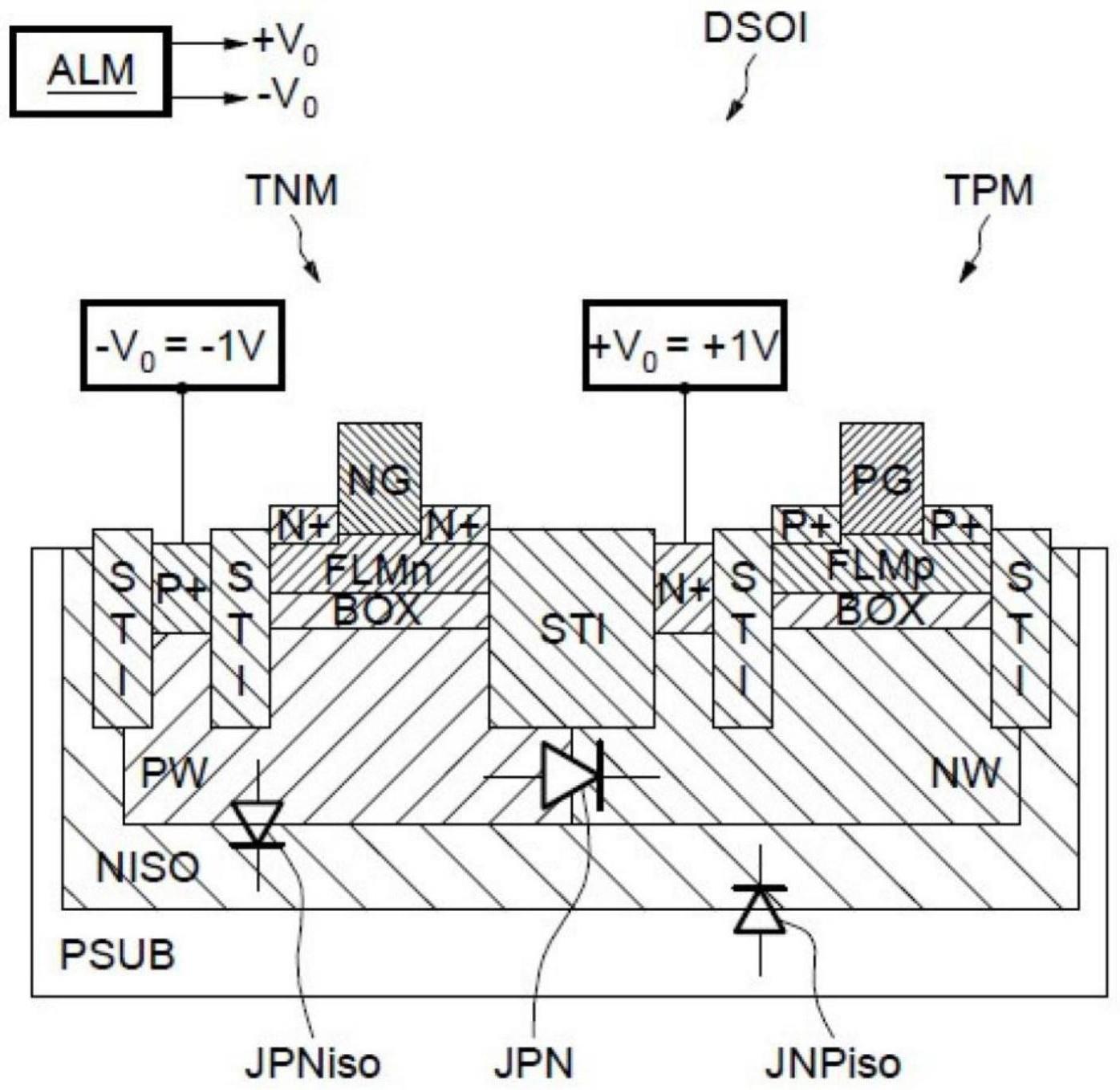

1、根据一个方面,在这方面提出了绝缘体上硅类型的半导体器件,包括在半导体膜中和半导体膜上的至少一个nmos晶体管,该半导体膜通过掩埋介电层与设置在载体衬底中的p型掺杂阱分离;在半导体膜中和半导体膜上的至少一个pmos晶体管,该半导体膜通过掩埋介电层与设置在载体衬底中的n型掺杂阱分离;以及电源电路,该电源电路被配置为在p型阱和n型阱中产生电压,从而选择性地向nmos晶体管和pmos晶体管提供中性、前向和逆向反向偏置条件,其中电源电路被配置为在中性反向偏置条件下产生p型阱中的第一非零负电压和n型阱中的第一非零正电压,nmos晶体管和pmos晶体管分别被配置为在中性反向偏置条件下具有标称阈值电压。

2、换句话说,提出了在中性反向偏置的特定情况下,其中晶体管的阱分别被负偏置和正偏置,产生被特别配置为具有标称阈值电压(即,为电路的正常操作提供的阈值电压)的nmos晶体管和pmos晶体管。

3、因此,从包括p型阱的负偏置和n型阱的正偏置的中性反向偏置条件,有可能增加偏置p型阱的电压并同时降低偏置n型阱的电压,以便为nmos晶体管和pmos晶体管两者产生可用的前向反向偏置,而不超过两个阱之间的pn结的阈值电压。

4、实施例和实现方式涉及绝缘体上硅类型的半导体器件,通常由首字母缩略词“soi”表示,也就是说,由soi类型的衬底制成的半导体器件包括载体衬底,掩埋介电层和通常由硅制成的半导体膜,该半导体膜可以处于少数载流子的完全耗尽状态(“完全耗尽soi”的“fdsoi”)。

5、根据一个实施例,在这点上,电源电路被配置为在前向反向偏置条件下产生高于p型阱中的第一非零负电压的电压和低于n型阱中的第一非零正电压的电压。

6、根据一个实施例,电源电路被配置为在逆向反向偏置条件下产生低于p型阱中的第一非零负电压的电压和高于n型阱中的第一非零正电压的电压。

7、实际上,从包括p型阱的负偏置和n型阱的正偏置的相同中性反向偏置条件,还可以降低偏置p型阱的电压并同时增加偏置n型阱的电压,以便为nmos晶体管和pmos晶体管产生可用的逆向反向偏置,而不超过两个阱之间的pn结的阈值电压。

8、根据一个实施例,至少一个nmos晶体管在相应的半导体膜中包括拉伸应变沟道区,并且至少一个pmos晶体管在相应的半导体膜中包括压缩应变沟道区。

9、在硅晶体的一个方向上的机械拉伸应变通常在材料的垂直方向上产生压缩应变,反之亦然。术语“拉伸/压缩应变沟道区”是指在沟道区的方向上,即在晶体管的源极和漏极之间的方向上考虑给定的应变(拉伸或压缩)。

10、nmos晶体管的沟道中的拉伸应变和pmos晶体管的沟道中的压缩应变允许改善晶体管的性能,特别是在载流子迁移率方面。然而,传统上在晶体管的沟道中使用机械应变具有困难,因为它们产生晶体管的阈值电压的降低,并因此产生电流泄漏的增加。然而,p型阱的负偏置和n型阱的正偏置产生相应晶体管的阈值电压的增加,因此允许受益于晶体管的沟道中的机械应变的优点而不经历其缺点。

11、根据一个实施例,所述至少一个pmos晶体管包括由硅-锗合金制成的沟道区,其在相应的半导体膜中具有大于25%原子百分比的锗浓度。

12、类似地,使用由具有高剂量锗的硅-锗化合物制成的沟道区允许改进pmos晶体管的性能,但反过来产生晶体管的阈值电压的降低。同样,n型阱的正偏压产生pmos晶体管的阈值电压的增加,因此允许受益于沟道中的硅-锗组合物的优点而不经历其缺点。

13、根据一个实施例,nmos晶体管和pmos晶体管包括分别位于栅极导电区和半导体膜之间的栅极介电层,栅极介电层包括氮以便形成氮氧化硅“sion”层。

14、氧化硅中氮的存在允许增加栅极介电层的电容而不减小栅极介电层的物理厚度,这在性能方面是有利的,同时维持穿过栅极介电层的隧穿泄漏常数。然而,在栅极介电层中氮的存在反过来产生nmos晶体管的阈值电压的降低和pmos晶体管的阈值电压的增加。然而,给定nmos晶体管和pmos晶体管的特定配置以在其中晶体管的阱分别被负偏置和正偏置的特定中性反向偏置条件下具有标称阈值电压,在此再次可能受益于栅极介电层中的氮氧化硅的优点而不经历其缺点。

15、根据一个实施例,nmos晶体管和pmos晶体管包括栅极导电区,该栅极导电区包括氮化钛和选自镧和铝的氮化钛添加剂,以便调制栅极的功函数(work function),从而在中性反向偏置条件下获得标称阈值电压。

16、镧和铝允许增加或降低pmos和nmos晶体管的阈值电压,并且因此有利地允许将阈值电压调节到适合于在上述中性反向偏置条件下电路的正常使用的标称值。

17、根据一个实施例,nmos晶体管和pmos晶体管包括相应沟道区,该沟道区包括适于调制沟道区的功函数的掺杂物质的浓度,以便在中性反向偏置条件下获得标称阈值电压。

18、沟道区的掺杂仍然可以保持本征,也就是说包括零浓度的掺杂物质,在此再次允许将pmos和nmos晶体管的阈值电压调节到适合于在上述中性反向偏置条件下电路的正常使用的标称值。

19、根据一个实施例,所述器件包括至少一个cmos电路,所述cmos电路配备有所述nmos晶体管和所述pmos晶体管,所述nmos晶体管和pmos晶体管被配置为在中性反向偏压条件下具有在以下间隔中的至少一者中的标称阈值电压:

20、被称为超低阈值电压的阈值电压间隔,其绝对值在0.15v和0.25v之间;

21、被称为低阈值电压的阈值电压间隔,其绝对值在0.2v和0.3v之间;

22、被称为下中间阈值电压的阈值电压间隔,其绝对值在0.25v与0.35v之间;

23、被称为上中间阈值电压的阈值电压间隔,其绝对值在0.3v与0.4v之间;或

24、被称为高阈值电压的阈值电压间隔,其绝对值在在0.35v与0.45v之间。

25、特别地,该器件可以包括分别在上面列出的两个间隔中的至少一个cmos电路,或者分别在上面列出的三个间隔中的至少一个cmos电路,或者分别在上面列出的四个间隔中的至少一个cmos电路,或者在上面列出的每个间隔中的至少一个cmos电路。

26、根据另一方面,提出了一种用于制造绝缘体上硅类型的半导体器件的方法,包括:

27、在通过掩埋介电层与设置在载体衬底中的p型掺杂阱分离的半导体膜中和半导体膜上形成至少一个nmos晶体管,

28、在通过掩埋介电层与设置在载体衬底中的n型掺杂阱分离的半导体膜中和半导体膜上形成至少一个pmos晶体管,以及

29、形成能够在p型和n型阱中产生电压的电源电路,以便选择性地向nmos晶体管和pmos晶体管提供中性、前向和逆向反向偏置条件,中性反向偏置条件包括施加在p型阱中的第一非零负电压和施加在n型阱中的第一非零正电压,

30、nmos晶体管和pmos晶体管的结构被配置为在中性反向偏置条件下向nmos晶体管和pmos晶体管提供相应的标称阈值电压。

31、根据一个实施方案,前向反向偏置条件包括高于施加于p型阱中的第一非零负电压的电压和低于施加于n型阱中的第一非零正电压的电压。

32、根据一个实施方案,逆向反向偏置条件包括低于施加于p型阱中的第一非零负电压的电压和高于施加于n型阱中的第一非零正电压的电压。

33、根据一种实现方式,所述至少一个nmos晶体管的形成包括在相应的半导体膜中形成拉伸应变沟道区,并且所述至少一个pmos晶体管的形成包括在相应的半导体膜中形成压缩应变沟道区。

34、根据一个实施方式,所述至少一个pmos晶体管的形成包括在各个半导体膜中形成由硅-锗合金制成的沟道区,其中锗浓度大于25%原子百分比。

35、根据一个实施方式,nmos晶体管和pmos晶体管的形成包括分别位于栅极导电区域和半导体膜之间的栅极介电层的形成,栅极介电层包括氮以便形成氮氧化硅层。

36、根据一种实现方式,nmos晶体管和pmos晶体管的形成包括栅极导电区的形成,该栅极导电区包括氮化钛和选自镧和铝的氮化钛添加剂,以便调节栅极的功函数,从而在中性反向偏置条件下获得标称阈值电压。

37、根据一种实现方式,nmos晶体管和pmos晶体管的形成包括形成相应沟道区,该沟道区包括适当地调制沟道区的功函数以在中性反向偏置条件下获得标称阈值电压的掺杂物质的浓度。

38、根据一个实施方案,所述方法包括形成配备有nmos晶体管和pmos晶体管的至少一个cmos电路,所述至少一个cmos电路被配置为在以下间隔中的至少一者中在中性反向偏压条件下向nmos晶体管和pmos晶体管提供标称阈值电压:

39、被称为超低阈值电压的阈值电压间隔,其绝对值在0.15v和0.25v之间;

40、被称为低阈值电压的阈值电压间隔,其绝对值在0.2v和0.3v之间;

41、被称为下中间阈值电压的阈值电压间隔,其绝对值在0.25v与0.35v之间;

42、被称为上中间阈值电压的阈值电压间隔,其绝对值在0.3v与0.4v之间;或

43、被称为高阈值电压的阈值电压间隔,其绝对值在0.35v与0.45v之间。

- 还没有人留言评论。精彩留言会获得点赞!