栅间氧化层的制备方法及屏蔽栅MOS器件的制备方法与流程

本发明涉及半导体器件及半导体制造,尤其涉及一种栅间氧化层的制备方法及屏蔽栅mos器件的制备方法。

背景技术:

1、屏蔽栅mosfet(shield gate mosfet,sgt-mosfet)功率器件是一种基于传统沟槽式mosfet(u-mosfet)的一种改进型的沟槽式功率器件。屏蔽栅mosfet采用的是电荷耦合结构,即屏蔽栅mosfet的深沟槽具有两层多晶硅,上层多晶硅为栅极,下层多晶硅作为场板和器件源极相连辅助耗尽漂移区,相比于传统沟槽式mosfet功率器件,其开关速度更快,导通损耗更低,具有更好的器件性能。

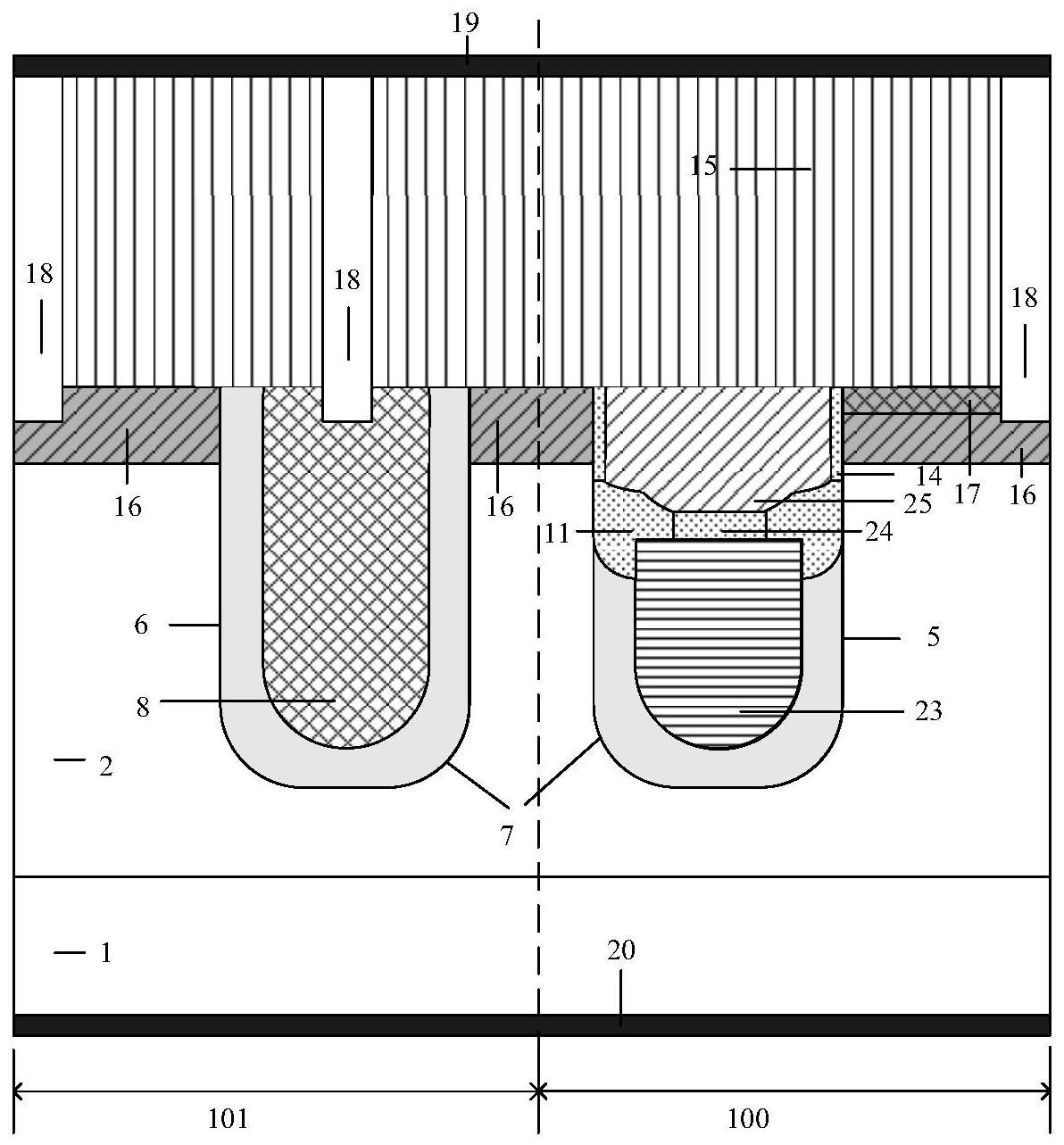

2、传统的屏蔽栅mos器件,如图1所示,其栅极多晶硅底部平坦,栅极和源极相对面积较小,但在器件反向耐压时,由于电荷补偿原理,处于零电位的栅极多晶硅也会参与外延层漂移区的耗尽。相较器件场氧化层,栅间氧化层的厚度很薄,尤其当器件反向耐压时,外延和栅极多晶硅存在电势差,因此栅极多晶硅下方拐角处的栅间氧化层会存在峰值电场;且当栅极多晶硅层越深,器件外延和控制栅极电势差越大,栅极多晶硅层下方拐角处的栅间氧化层的电场强度就越大,栅氧越容易被击穿,从而对器件可靠性带来更大的挑战。

3、由于屏蔽栅mos器件的栅氧采用热生长方式形成,通过直接延长热生长时间增加栅氧厚度以提高此处耐压,就会额外增加器件设计过程中的热预算、增加设计复杂程度;且对于小pitch(焊盘的间距)器件,其沟槽开口更小,对填充工艺带来的挑战更高。通过高密度等离子体化学气相沉积(high density plasma chemical vapor deposition,hdp cvd)直接生成隔离氧化层时容易产生空洞,后续氧化硅刻蚀时由于空洞的存在会使得栅源多晶硅之间隔离较差,进而导致栅源漏电异常。

技术实现思路

1、为了解决以上技术问题,本发明提供了一种栅间氧化层的制备方法及屏蔽栅mos器件的制备方法。

2、本发明所解决的技术问题可以采用以下技术方案实现:

3、一种栅间氧化层的制备方法,包括:

4、步骤s1,提供一半导体基板,于所述半导体基板中形成至少一有源区沟槽,所述有源区沟槽中形成有底部侧壁的场氧化层以及填充的未掺杂的第一源极多晶硅层,所述场氧化层的厚度低于所述第一源极多晶硅层的厚度;

5、步骤s2,于所述半导体基板的第一主面淀积形成第一隔离氧化层,且所述有源区沟槽内的所述第一隔离氧化层具有一空洞;

6、步骤s3,将所述第一隔离氧化层刻蚀至与所述第一主面平齐,然后刻蚀所述有源区沟槽内的所述第一隔离氧化层,暴露出所述第一源极多晶硅层;

7、步骤s4,对所述第一源极多晶硅层进行第一导电类型杂质的注入,形成第二源极多晶硅层,随后通过热氧化法在所述第二源极多晶硅层表面生成第二隔离氧化层,以在所述有源区沟槽中形成中间薄两边厚的栅间氧化层。

8、优选地,所述步骤s1包括:

9、步骤s11,在所述半导体基板的第一主面淀积一硬掩模层,选择性刻蚀所述硬掩模层,得到图形化的第一硬掩模窗口;

10、步骤s12,在所述第一硬掩模窗口的掩蔽下,于所述半导体基板中刻蚀出所述有源区沟槽;

11、步骤s13,通过热氧化法在所述有源区沟槽的底部和侧壁生长所述场氧化层,然后在所述场氧化层内淀积未掺杂的所述第一源极多晶硅层;

12、步骤s14,在所述半导体基板的第一主面淀积光刻胶,选择性刻蚀所述光刻胶,得到图形化的第二掩模窗口;

13、步骤s15,在所述第二硬掩模窗口的掩蔽下,对所述有源区沟槽内的所述场氧化层和所述第一源极多晶硅层进行刻蚀,所述场氧化层的刻蚀深度大于所述第一源极多晶硅层的刻蚀深度。

14、优选地,所述步骤s12中,所述有源区沟槽的开口范围为0.2μm-1.8μm;

15、所述有源区沟槽的刻蚀深度为1μm-10μm。

16、优选地,所述步骤s15中,所述第一源极多晶硅层的刻蚀深度为0.5μm-2μm。

17、所述场氧化层的刻蚀后的厚度为

18、优选地,所述步骤s2中的所述第一隔离氧化层采用高密度等离子体化学气相沉积法淀积形成,并产生所述空洞。

19、优选地,所述步骤s3包括:

20、步骤s31,在所述半导体基板的第一主面淀积光刻胶,选择性刻蚀所述光刻胶,得到图形化的第三掩模窗口;

21、步骤s32,在所述第三硬掩模窗口的掩蔽下刻蚀所述第一隔离氧化层,同时进行刻蚀废气检测,在开始检测到所述第一源极多晶硅层产生的刻蚀废气时停止刻蚀,以暴露出所述第一源极多晶硅层。

22、优选地,所述步骤s4包括:

23、步骤s41,在所述半导体基板的第一主面注入所述第一导电类型杂质,所述第一源极多晶硅层在所述第一隔离氧化层的刻蚀窗口的掩蔽下被注入第一导电类型杂质,以形成所述第二源极多晶硅层;

24、步骤s42,通过热氧化法在所述第二源极多晶硅层的表面生成所述第二隔离氧化层,中间的所述第二隔离氧化层的厚度小于与两侧的所述第一隔离氧化层的厚度,以在所述有源区沟槽中形成中间薄两边厚的所述栅间氧化层。

25、本发明还提供一种屏蔽栅mos器件的制备方法,包括:

26、采用上述的栅间氧化层的制备方法,在一半导体基板中的有源区沟槽中形成中间薄两边厚的栅间氧化层;

27、在所述栅间氧化层的上方形成栅极多晶硅层。

28、优选地,所述形成至少一所述有源区沟槽的同时还包括:

29、于所述半导体基板中形成有至少一终端区沟槽,于所述终端区沟槽中形成有底部侧壁的场氧化层以及填充的未掺杂的第一源极多晶硅层。

30、优选地,所述形成栅极多晶硅层之后还包括:

31、于所述半导体基板中除所述有源区沟槽和所述终端区沟槽的区域形成第二导电类型的阱区;

32、于有源区的所述阱区内形成第一导电类型的源区;

33、于所述半导体基板的第一主面上方形成一介质层,并于所述介质层中形成对应所述阱区、终端区的所述第一源极多晶硅层的接触孔;

34、于所述介质层的上方形成一源极金属层,于所述半导体基板的第二主面形成一漏极金属层。

35、本发明技术方案的优点或有益效果在于:

36、本发明通过利用hdp cvd法生成隔离氧化层时产生的空洞,刻蚀后结合热氧化工艺注入再热生长的方法重新生长第二隔离氧化层,避免直接刻蚀hdp氧化层生成中间薄两边厚的栅间氧化层时因厚度过薄导致器件栅源隔离不足而导致漏电异常问题。

技术特征:

1.一种栅间氧化层的制备方法,其特征在于,包括:

2.根据权利要求1所述的栅间氧化层的制备方法,其特征在于,所述步骤s1包括:

3.根据权利要求2所述的栅间氧化层的制备方法,其特征在于,所述步骤s12中,所述有源区沟槽的开口范围为0.2μm-1.8μm;

4.根据权利要求2所述的栅间氧化层的制备方法,其特征在于,所述步骤s15中,所述第一源极多晶硅层的刻蚀深度为0.5μm-2μm。

5.根据权利要求1所述的栅间氧化层的制备方法,其特征在于,所述步骤s2中的所述第一隔离氧化层采用高密度等离子体化学气相沉积法淀积形成,并产生所述空洞。

6.根据权利要求1所述的栅间氧化层的制备方法,其特征在于,所述步骤s3包括:

7.根据权利要求1所述的栅间氧化层的制备方法,其特征在于,所述步骤s4包括:

8.一种屏蔽栅mos器件的制备方法,其特征在于,包括:

9.根据权利要求8所述的屏蔽栅mos器件的制备方法,其特征在于,所述形成至少一所述有源区沟槽的同时还包括:

10.根据权利要求9所述的屏蔽栅mos器件的制备方法,其特征在于,所述形成栅极多晶硅层之后还包括:

技术总结

本发明提供一种栅间氧化层的制备方法及屏蔽栅MOS器件的制备方法,包括:步骤S1,于半导体基板中形成有源区沟槽,有源区沟槽中形成有场氧化层以及第一源极多晶硅层,场氧化层的厚度低于第一源极多晶硅层的厚度;步骤S2,形成第一隔离氧化层,且第一隔离氧化层具有空洞;步骤S3,刻蚀第一隔离氧化层,暴露出第一源极多晶硅层;步骤S4,进行杂质注入,形成第二源极多晶硅层,随后通过热氧化法在第二源极多晶硅层表面生成第二隔离氧化层,以形成中间薄两边厚的栅间氧化层。有益效果:利用生成隔离氧化层时产生的空洞,刻蚀后结合热氧化法重新生长第二隔离氧化层,避免直接刻蚀生成栅间氧化层时因厚度过薄导致器件栅源隔离不足而导致漏电异常问题。

技术研发人员:张雨,俱帅,刘厚超,马一洁,苏亚兵,杜琪,苏海伟

受保护的技术使用者:上海维安半导体有限公司

技术研发日:

技术公布日:2024/1/15

- 还没有人留言评论。精彩留言会获得点赞!