一种半导体结构及其制备方法与流程

本公开涉及半导体制造领域,尤其涉及一种半导体结构及其制备方法。

背景技术:

1、动态随机存取半导体结构(dynamic random access memory,dram)作为一种重要的半导体器件,其可用来作为电子装置运算时的数据存储或储存程序,以进行数据处理。然而,随着动态随机存取半导体结构(dynamic random access memory,dram)不断朝着小型化、高集成度的方向发展,在动态随机存取半导体结构(dynamic random access memory,dram)的制备过程中,仍存在许多降低半导体器件的性能的因素。

技术实现思路

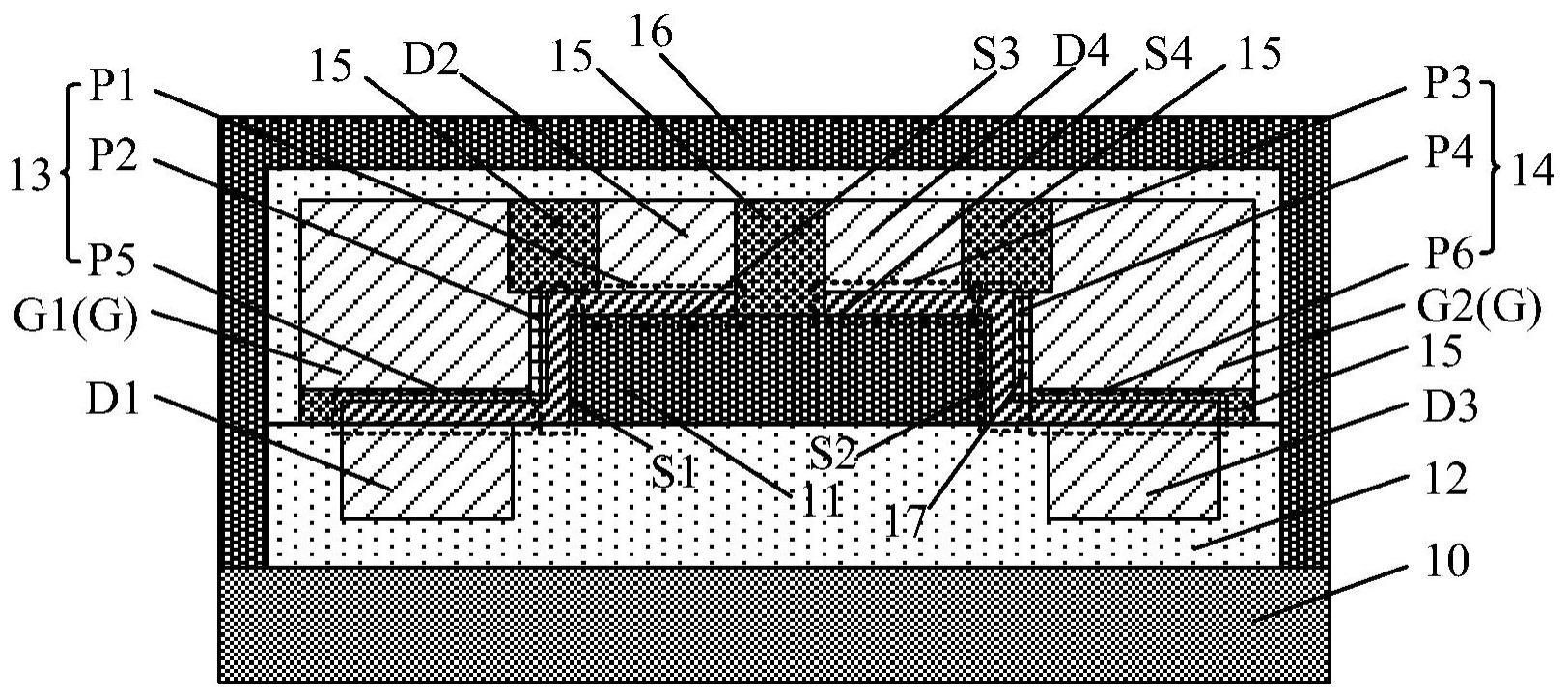

1、本公开实施例提供了一种半导体结构,所述半导体结构包括:

2、衬底;

3、位于所述衬底上的第一介质层,所述第一介质层包括相对设置且沿突出于所述衬底平面的方向向上延伸的第一侧壁和第二侧壁,以及邻近所述第一侧壁的第一表面及邻近所述第二侧壁的第二表面;

4、第一沟道层,所述第一沟道层至少包括覆盖所述第一表面的第一子部及覆盖所述第一侧壁的第二子部;

5、第二沟道层,所述第二沟道层至少包括覆盖所述第二表面的第三子部及覆盖所述第二侧壁的第四子部;

6、栅极层,所述栅极层覆盖部分所述第一沟道层及部分所述第二沟道层。

7、在一些实施例中,所述第一沟道层还包括邻近所述第一侧壁且覆盖所述衬底表面的第五子部;所述第二沟道层还包括邻近所述第二侧壁且覆盖所述衬底表面的第六子部。

8、在一些实施例中,所述第一沟道层的第一子部与所述第二子部之间存在第一夹角α1,0°<α1<180°,所述第二子部与所述第五子部之间存在第二夹角α2,0°<α2<180°;所述第二沟道层的第三子部与所述第四子部之间存在第三夹角α3,0°<α3<180°;所述第四子部与所述第六子部之间存在第四夹角α4,0°<α4<180°。

9、在一些实施例中,所述第一夹角α1与所述第三夹角α3相同,所述第二夹角α2与所述第四夹角α4相同;或者,

10、所述第一夹角α1、所述第二夹角α2、所述第三夹角α3及所述第四夹角α4均为90°。

11、在一些实施例中,所述半导体结构还包括:

12、位于所述第一沟道层一侧且位于衬底上的第一极,以及位于所述第一介质层上的第二极;

13、位于所述第二沟道层一侧且位于衬底上的第三极,以及位于所述第一介质层上的第四极。

14、在一些实施例中,所述栅极层包括第一栅极层和第二栅极层,所述第一栅极层覆盖所述第一极和第二极之间的所述第一沟道层;所述第二栅极层覆盖所述第三极和所述第四极之间的所述第二沟道层。

15、在一些实施例中,所述半导体结构还包括:

16、间隔层,所述间隔层位于所述第一极和所述第一栅极层之间、所述第二极和所述第一栅极层之间、所述第一沟道层和所述第二沟道层之间、所述第二栅极层和所述第四极之间以及所述第三极和所述第二栅极层之间;和/或,

17、保护层,所述保护层至少覆盖所述栅极层、所述第一沟道层、所述第二沟道层、所述第二极及所述第四极的表面。

18、本公开实施例还提供了一种半导体结构的制备方法,所述制备方法包括:

19、提供衬底,在所述衬底上形成第一介质层,所述第一介质层包括相对设置且沿突出于所述衬底平面的方向向上延伸的第一侧壁和第二侧壁,以及邻近所述第一侧壁的第一表面及邻近所述第二侧壁的第二表面;

20、形成覆盖所述衬底、所述第一侧壁、所述第二侧壁及所述第一介质层表面的沟道材料层,及形成覆盖所述沟道材料层表面的导电材料层;

21、对所述导电材料层及所述沟道材料层执行刻蚀工艺,保留下来的所述导电材料层构成栅极层;保留下来的所述沟道材料层分别构成第一沟道层和第二沟道层;其中,所述第一沟道层至少包括覆盖所述第一表面的第一子部及覆盖所述第一侧壁的第二子部,所述第二沟道层至少包括覆盖所述第二表面的第三子部及覆盖所述第二侧壁的第四子部。

22、在一些实施例中,对所述沟道材料层及所述导电材料层执行刻蚀工艺,包括:

23、去除位于所述第一侧壁上方、所述第二侧壁上方的部分所述导电材料层以形成所述栅极层;

24、去除位于所述第一表面和第二表面之间的部分所述沟道材料层以在同一工艺步骤中分别形成第一沟道层和第二沟道层;其中,所述第一沟道层包括覆盖所述第一表面的第一子部、覆盖所述第一侧壁的第二子部及邻近所述第一侧壁且覆盖所述衬底表面的第五子部,所述第二沟道层包括覆盖所述第二表面的第三子部、覆盖所述第二侧壁的第四子部及邻近所述第二侧壁且覆盖所述衬底表面的第六子部。

25、在一些实施例中,所述第一沟道层的第一子部与所述第二子部之间存在第一夹角α1,0°<α1<180°,所述第二子部与所述第五子部之间存在第二夹角α2,0°<α2<180°;所述第二沟道层的第三子部与所述第四子部之间存在第三夹角α3,0°<α3<180°;所述第四子部与所述第六子部之间存在第四夹角α4,0°<α4<180°。

26、本公开实施例所提供的半导体结构及其制备方法,其中,所述半导体结构包括:衬底;位于所述衬底上的第一介质层,所述第一介质层包括相对设置且沿突出于所述衬底平面的方向向上延伸的第一侧壁和第二侧壁,以及邻近所述第一侧壁的第一表面及邻近所述第二侧壁的第二表面;第一沟道层,所述第一沟道层至少包括覆盖所述第一表面的第一子部及覆盖所述第一侧壁的第二子部;第二沟道层,所述第二沟道层至少包括覆盖所述第二表面的第三子部及覆盖所述第二侧壁的第四子部;栅极层,所述栅极层覆盖部分所述第一沟道层及部分所述第二沟道层。如此,在本公开实施例中,在第一介质层的两侧上分别设置了第一沟道层和第二沟道层,且第一沟道层覆盖了第一介质层的一个侧壁和部分表面,第二沟道层覆盖了第一介质层的另一个侧壁及部分表面,这便使得两个沟道层的长度可跟随第一介质层的高度变化而产生变化,有利于实现两个沟道层长度的灵活调节。可以理解的,以两个沟道层为基础通过设置其他结构的方式可分别获得两个晶体管。由于在本公开实施例中所提供的半导体结构中,两个沟道层的延伸方向可以包含沿突出于衬底平面的方向向上延伸的部分,使得任一沟道层中的至少部分区段与衬底的平面之间可以存在一定的夹角,从而可有效减小该区段对衬底平面尺寸的占用(与平面晶体管相比),使得本公开实施例提供的半导体结构可以具有较高的晶体管密度,从而可显著降低阵列区的面积。

27、本公开的一个或多个实施例的细节在下面的附图和描述中提出。本公开的其它特征和优点将从说明书、附图变得明显。

技术特征:

1.一种半导体结构,其特征在于,所述半导体结构包括:

2.根据权利要求1所述的半导体结构,其特征在于,所述第一沟道层还包括邻近所述第一侧壁且覆盖所述衬底表面的第五子部;所述第二沟道层还包括邻近所述第二侧壁且覆盖所述衬底表面的第六子部。

3.根据权利要求2所述的半导体结构,其特征在于,所述第一沟道层的第一子部与所述第二子部之间存在第一夹角α1,0°<α1<180°,所述第二子部与所述第五子部之间存在第二夹角α2,0°<α2<180°;所述第二沟道层的第三子部与所述第四子部之间存在第三夹角α3,0°<α3<180°;所述第四子部与所述第六子部之间存在第四夹角α4,0°<α4<180°。

4.根据权利要求3所述的半导体结构,其特征在于,所述第一夹角α1与所述第三夹角α3相同,所述第二夹角α2与所述第四夹角α4相同;或者,

5.根据权利要求1-4中任一项所述的半导体结构,其特征在于,所述半导体结构还包括:

6.根据权利要求5所述的半导体结构,其特征在于,所述栅极层包括第一栅极层和第二栅极层,所述第一栅极层覆盖所述第一极和第二极之间的所述第一沟道层;所述第二栅极层覆盖所述第三极和所述第四极之间的所述第二沟道层。

7.根据权利要求6所述的半导体结构,其特征在于,所述半导体结构还包括:

8.一种半导体结构的制备方法,其特征在于,所述制备方法包括:

9.根据权利要求8所述的制备方法,其特征在于,对所述沟道材料层及所述导电材料层执行刻蚀工艺,包括:

10.根据权利要求9所述的制备方法,其特征在于,所述第一沟道层的第一子部与所述第二子部之间存在第一夹角α1,0°<α1<180°,所述第二子部与所述第五子部之间存在第二夹角α2,0°<α2<180°;所述第二沟道层的第三子部与所述第四子部之间存在第三夹角α3,0°<α3<180°;所述第四子部与所述第六子部之间存在第四夹角α4,0°<α4<180°。

技术总结

本公开实施例提供了一种半导体结构及其制备方法,其中,所述半导体结构包括:衬底;位于衬底上的第一介质层,第一介质层包括相对设置且沿突出于衬底平面的方向向上延伸的第一侧壁和第二侧壁,以及邻近第一侧壁的第一表面及邻近第二侧壁的第二表面。第一沟道层,第一沟道层至少包括覆盖第一表面的第一子部及覆盖第一侧壁的第二子部,第二沟道层,第二沟道层至少包括覆盖第二表面的第三子部及覆盖第二侧壁的第四子部;栅极层,栅极层覆盖部分第一沟道层及部分第二沟道层。

技术研发人员:薛兴坤,脱穷,李泽伦,徐汉东,黄国铭,顾婷婷,董海洋

受保护的技术使用者:长鑫存储技术有限公司

技术研发日:

技术公布日:2024/1/14

- 还没有人留言评论。精彩留言会获得点赞!