在SOI衬底上形成高压器件的方法与流程

本申请涉及半导体制造领域,具体涉及一种在soi衬底上形成高压器件的方法。

背景技术:

1、soi全名为silicon on insulator,即绝缘衬底上的硅,该技术是在顶层硅和背衬底之间引入了一层埋氧化层,可使两者之间的寄生电容比原来的少上一倍。

2、soi衬底片由于其特殊性,埋氧层上方的硅衬底的厚度不足以支撑形成ldmos等高压器件所需要的结深,为了满足高压器件的形成要求,传统方案会加厚埋氧层上方的硅衬底,然而,这会牺牲低压cmos的性能。

技术实现思路

1、为了解决相关技术中的问题,本申请提供了一种在soi衬底上形成高压器件的方法。该技术方案如下:

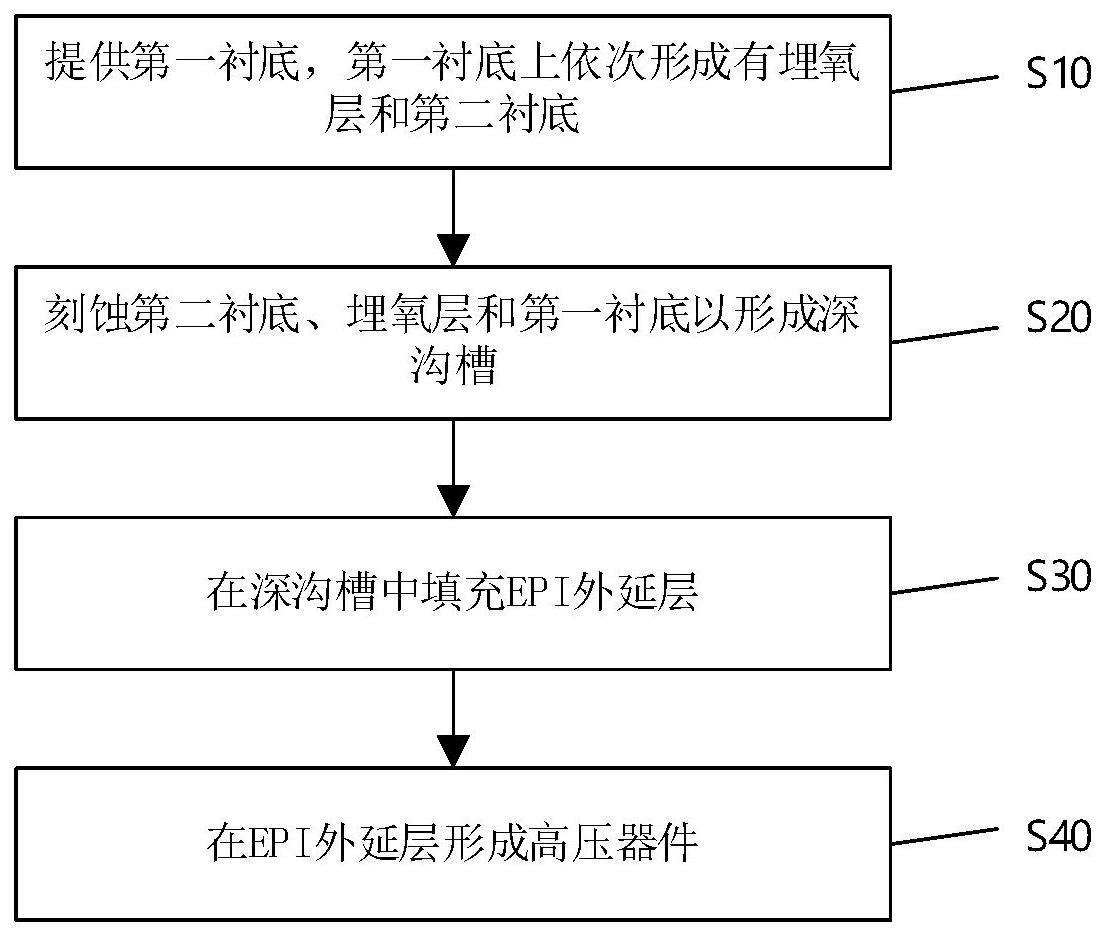

2、一方面,本申请实施例提供了一种在soi衬底上形成高压器件的方法,该方法包括:

3、提供第一衬底,所述第一衬底上依次形成有埋氧层和第二衬底;

4、刻蚀所述第二衬底、埋氧层和所述第一衬底以形成深沟槽;

5、在所述深沟槽中填充epi外延层;

6、在所述epi外延层形成高压器件。

7、可选的,所述第一衬底和第二衬底为硅衬底。

8、可选的,所述第二衬底的厚度小于1000a。

9、可选的,所述埋氧层的厚度为1900a-2100a。

10、可选的,所述深沟槽是通过光刻工艺和干法刻蚀工艺形成的。

11、可选的,所述epi外延层为硅外延层。

12、可选的,在所述刻蚀所述第二衬底、埋氧层和所述第一衬底以形成深沟槽的步骤中,对所述第一衬底的刻蚀深度大于4um。

13、本申请技术方案,至少包括如下优点:

14、1.通过在soi衬底中刻蚀形成深沟槽,并进一步在深沟槽中填充epi外延层,使得epi外延层能够用于形成高压器件,从而可以突破第二衬底的厚度,即上层硅衬底的厚度对高压器件结深的限制,实现了在不牺牲低压cmos性能的前提下,在soi衬底上集成高压器件的效果。

技术特征:

1.一种在soi衬底上形成高压器件的方法,其特征在于,所述方法包括:

2.根据权利要求1所述的方法,其特征在于,所述第一衬底和第二衬底为硅衬底。

3.根据权利要求1所述的方法,其特征在于,所述第二衬底的厚度小于1000a。

4.根据权利要求1所述的方法,其特征在于,所述埋氧层的厚度为1900a-2100a。

5.根据权利要求1所述的方法,其特征在于,所述深沟槽是通过光刻工艺和干法刻蚀工艺形成的。

6.根据权利要求1所述的方法,其特征在于,所述epi外延层为硅外延层。

7.根据权利要求1所述方法,其特征在于,在所述刻蚀所述第二衬底、埋氧层和所述第一衬底以形成深沟槽的步骤中,对所述第一衬底的刻蚀深度大于4um。

技术总结

本申请公开了一种在SOI衬底上形成高压器件的方法,涉及半导体制造领域。该方法包括:提供第一衬底,所述第一衬底上依次形成有埋氧层和第二衬底;刻蚀所述第二衬底、埋氧层和所述第一衬底以形成深沟槽;在所述深沟槽中填充EPI外延层;在所述EPI外延层形成高压器件;通过在SOI衬底中刻蚀形成深沟槽,并进一步在深沟槽中填充EPI外延层,使得EPI外延层能够用于形成高压器件,实现了在不牺牲低压CMOS性能的前提下,在SOI衬底上集成高压器件的效果。

技术研发人员:王晓日,陈广龙

受保护的技术使用者:华虹半导体(无锡)有限公司

技术研发日:

技术公布日:2024/1/15

- 还没有人留言评论。精彩留言会获得点赞!