一种氮化镓功率器件及其制造方法与流程

本技术涉及半导体,特别涉及一种氮化镓功率器件及其制造方法。

背景技术:

1、氮化镓基异质场效应晶体管(heterojunction field effect transistors,hfets)在高速、大功率和高热稳定性应用中受到了广泛关注,然而氮化镓器件具有“电流坍塌”效应。电流崩塌是当漏极和栅极/源极之间承受了大电压应力后,沟道内的热电子隧穿到势垒层表面,被栅漏区之间的表面态俘获,这些负电荷好比在栅漏电极之间存在另一个栅极,也就是形成虚栅,从而使栅耗尽区横向扩展,减小沟道二维电子气(2deg)的浓度。在测试漏源极电流的时候就会出现电流能力下降的现象,这相当于通态电阻(动态电阻)增大。

2、针对“电流坍塌”效应,通常在漏极电极外增加一个p型半导体层来抑制了电子俘获,可以极大地改善电流坍塌,提高器件的可靠性。

3、然而,由于在漏极电极处引入p型半导体层,对栅极控制器件带来了新问题。为实现器件的正常关断以及对栅极电压范围的控制,通常有两种方法:第一,直接在栅极区域刻蚀出栅极凹槽,但栅极凹槽下方的势垒层厚度难以实现纳米级控制,晶圆片内刻蚀速率的分布差异,导致晶圆的加工工艺难度大;第二,二次外延生长势垒层,但是二次外延前的刻蚀,会对栅极结构下方的沟道层带来刻蚀损伤,导致界面缺陷严重,影响器件的可靠性。

技术实现思路

1、鉴于上述问题,本技术的目的在于提供一种氮化镓功率器件及其制造方法,改善漏极电极下方的第二p型半导体层带来的栅极问题,使得栅极结构工艺简单,避免了刻蚀损伤,提高了栅极可靠性;还使得器件具有多沟道,降低了器件的导通电阻。

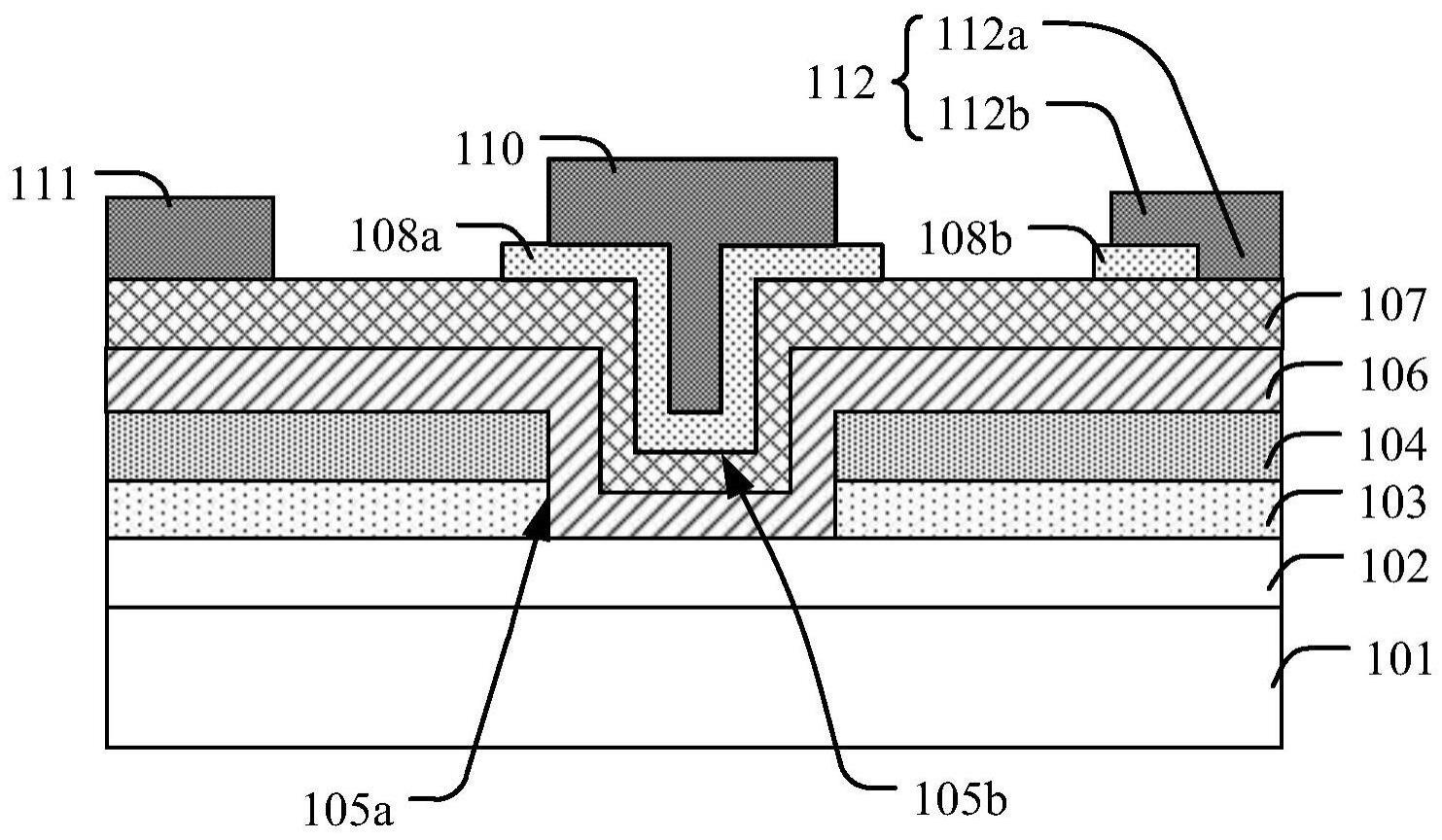

2、根据本发明的一方面,提供一种氮化镓功率器件,包括:衬底;至少一组第一外延结构,位于所述衬底上,所述第一外延结构内具有凹槽,所述凹槽从所述第一外延结构远离所述衬底的表面向其内部延伸;第二外延结构,位于所述第一外延结构上,所述第二外延结构共形地覆盖所述第一外延结构远离所述衬底的表面以及所述凹槽的底面和侧壁,所述第二外延结构共形地覆盖所述凹槽的底面和侧壁形成栅极凹槽;第一p型半导体层,位于所述第二外延结构上并覆盖所述栅极凹槽的底面和侧壁;第二p型半导体层,位于所述第一p型半导体层一侧的第二外延结构的表面,并且与第一p型半导体层相互分离;栅极电极,位于所述第一p型半导体层上,填充所述栅极凹槽并覆盖所述第一p型半导体层的至少部分表面;漏极电极和源极电极,所述漏极电极和所述源极电极分别位于所述栅极电极的两侧,且分别与所述栅极电极相互分离,所述源极电极覆盖部分所述第二外延结构的表面,所述漏极电极覆盖部分所述第二外延结构的表面和至少部分所述第二p型半导体层的表面。

3、上述的氮化镓功率器件,其中,包括一组所述第一外延结构,所述第一外延结构包括:第二沟道层,位于所述衬底上;第二势垒层,位于所述第二沟道层上,所述第二势垒层与所述第二沟道层形成异质结;所述凹槽从所述第二势垒层远离所述第二沟道层的表面向着所述第二沟道层的方向延伸,至少延伸至所述第二沟道层内部。

4、可选地,包括:多层第二沟道层和多层第二势垒层,多层第二沟道层和多层第二势垒层在垂直于所述衬底表面的方向上交替层叠设置,构成多组第一外延结构;其中,多层第二沟道层和多层第二势垒层中,最下层为一层第二沟道层,最上层为一层第二势垒层,相邻层的第二沟道层和第二势垒层形成异质结;所述凹槽从最上层的第二势垒层的表面向着所述衬底的方向延伸,至少延伸至最下层的第二沟道层内部。

5、可选地,还包括缓冲层,所述缓冲层位于所述衬底上,至少一组所述第一外延结构位于所述缓冲层上。

6、可选地,所述第二外延结构包括:第一沟道层,共形地覆盖第一外延结构远离所述衬底的表面以及所述凹槽的底面和侧壁;以及第一势垒层,共形地覆盖所述第一沟道层的表面。

7、可选地,所述第二沟道层和所述第二势垒层的界面靠近所述第二沟道层一侧形成有二维电子气;所述第一沟道层和所述第一势垒层的界面靠近所述第一沟道层一侧形成有二维电子气。

8、根据本发明的另一方面,提供一种氮化镓功率器件的制造方法,包括:在衬底上形成至少一组第一外延结构,在所述第一外延结构内形成凹槽,所述凹槽从所述第一外延结构远离所述衬底的表面向其内部延伸;在所述第一外延结构上形成第二外延结构,所述第二外延结构共形地覆盖所述第一外延结构远离所述衬底的表面以及所述凹槽的底面和侧壁,所述第二外延结构共形地覆盖所述凹槽的底面和侧壁形成栅极凹槽;在所述第二外延结构上形成第一p型半导体层和第二p型半导体层,所述第一p型半导体层覆盖所述栅极凹槽的底面和侧壁,所述第二p型半导体层位于所述第一p型半导体层一侧的第二外延结构的表面,并且与第一p型半导体层相互分离;在所述第一p型半导体层上形成栅极电极,所述栅极电极填充所述栅极凹槽并覆盖所述第一p型半导体层的至少部分表面;形成漏极电极和源极电极,所述漏极电极和所述源极电极分别位于所述栅极电极的两侧,且分别与所述栅极电极相互分离,所述源极电极覆盖部分所述第二外延结构的表面,所述漏极电极覆盖部分所述第二外延结构的表面和至少部分所述第二p型半导体层的表面。

9、可选地,形成所述第一外延结构的方法包括:在所述衬底上外延形成第二沟道层;在所述第二沟道层上外延形成第二势垒层,所述第二势垒层与所述第二沟道层形成异质结;刻蚀所述第一外延结构形成凹槽,其中,所述凹槽从所述第二势垒层远离所述第二沟道层的表面向着所述第二沟道层的方向延伸,至少延伸至所述第二沟道层内部。

10、可选地,形成所述第一外延结构的方法包括:在所述衬底上依次外延形成多层第二沟道层和多层第二势垒层,多层第二沟道层和多层第二势垒层在垂直于所述衬底表面的方向上交替层叠设置,构成多组第一外延结构;其中,多层第二沟道层和多层第二势垒层中,最下层为一层第二沟道层,最上层为一层第二势垒层,相邻层的第二沟道层和第二势垒层形成异质结;刻蚀所述第一外延结构形成凹槽,所述凹槽从最上层的第二势垒层的表面向着所述衬底的方向延伸,至少延伸至最下层的第二沟道层内部。

11、可选地,还包括在所述衬底上形成缓冲层,至少一组所述第一外延结构位于所述缓冲层上。

12、可选地,形成所述第二外延结构的方法包括:在所述第一外延结构上外延形成第一沟道层,所述第一沟道层共形地覆盖第一外延结构远离所述衬底的表面以及所述凹槽的底面和侧壁;以及在所述第一沟道层上外延形成第一势垒层,所述第一势垒层共形地覆盖所述第一沟道层的表面。

13、可选地,所述第二沟道层和所述第二势垒层的界面靠近所述第二沟道层一侧形成有二维电子气;所述第一沟道层和所述第一势垒层的界面靠近所述第一沟道层一侧形成有二维电子气。

14、本实施例中,第一外延结构内具有凹槽,第二外延结构共形地覆盖凹槽,以形成栅极凹槽,第二外延结构中的第一沟道层和第一势垒层经由一次外延生长形成,使得第一沟道层和第一势垒层的界面不会存在刻蚀损伤,避免了常规凹槽刻蚀引起的沟道层刻蚀损伤,保证了的器件的可靠性,且外延生长的第二外延结构的厚度更加容易得到控制。

15、进一步地,在栅极电极下方设置第一p型半导体层,栅极电极下方的第一p型半导体层可以耗尽第一沟道层与第一势垒层形成的异质结处的二维电子气,从而使器件处于常闭型状态,有利于驱动电路的设计。且外延生长的p型半导体层,其厚度更加容易得到控制,从而更好地实现阈值电压(vth)设计值。

16、进一步地,在漏极电极与第一势垒层之间增加了第二p型半导体层,漏极电极下方的第二p型半导体层在漏极电极一侧产生空穴注入,抑制了电子俘获,极大地改善了电流坍塌,提高了器件的可靠性。

17、进一步地,在第一外延结构内形成凹槽,然后在凹槽内共形生长第二外延结构以形成栅极凹槽,使得器件的栅极下方只有一层导电沟道,栅极区域以外的地方则具有多个导电沟道,使第一p型半导体层能够耗尽栅极下方导电沟道,而第二p型半导体层下方仍然具有导通的导电沟道,实现了器件的正常栅极控制器件开关的功能。

18、在优选的实施例中,通过设置多组第一外延结构,使得器件具有多沟道,降低了器件的导通电阻。

- 还没有人留言评论。精彩留言会获得点赞!