一种多次外延平面型碳化硅场效应管结构及其制造工艺的制作方法

本发明涉及碳化硅器件领域,尤其涉及了一种多次外延平面型碳化硅场效应管结构及其制造工艺。

背景技术:

1、碳化硅由于化学性能稳定、导热系数高、热膨胀系数小、耐磨性能好,除作磨料用外,还有很多其他用途,例如:以特殊工艺把碳化硅粉末涂布于水轮机叶轮或汽缸体的内壁,可提高其耐磨性而延长使用寿命1~2倍;用以制成的高级耐火材料,耐热震、体积小、重量轻而强度高,节能效果好。低品级碳化硅(含sic约85%)是极好的脱氧剂,用它可加快炼钢速度,并便于控制化学成分,提高钢的质量。此外,碳化硅还大量用于制作电热元件硅碳棒。

2、碳化硅的硬度很大,莫氏硬度为9.5级,仅次于世界上最硬的金刚石(10级),具有优良的导热性能,是一种半导体,高温时能抗氧化。

3、在si材料已经接近理论性能极限的今天,sic功率器件因其高耐压、低损耗、高效率等特性,一直被视为“理想器件”而备受期待。然而,相对于以往的si材质器件,sic功率器件在性能与成本间的平衡以及其对高工艺的需求,将成为sic功率器件能否真正普及的关键。

4、碳化硅本身为一种极性晶体,不同极性面皆可能对电性能(热电性能、铁电性能)、生长性能等特性有所影响。而对于采用碳化硅(sic)材料做成的平面式功率金属氧化物半导体场效晶体管(mosfet)而言,未来器件的方向包括:一、做沟槽栅,沟槽型碳化硅mosfet器件作为公认的下一代碳化硅功率半导体器件,相比于平面型器件具有更低的比导通电阻和导通压降,但是沟槽刻蚀工艺、沟槽氧化工艺、沟槽栅氧保护设计方法等技术难度较大;二、为平面栅缩小器件尺寸,特别是减少沟道电阻占比,又可以降低栅极电容,工艺技术上更加容易实现。但现有的平面式sic mosfet的器件,因碳化硅晶体材料的特性,沟道区经过工艺之后,迁移率受到影响,所以目前平面式sic mosfet器件沟道电阻大。本发明能在现有平面栅的工艺上减少沟道电阻的占比,提高沟道电子迁移率,能够集成更高的器件密度,有更好的器件性能的提升。

5、目前,专利号为202080055783.7的发明专利,还存在工艺复杂,性能不佳的缺陷。

技术实现思路

1、本发明针对现有技术中的缺点,提供了一种多次外延平面型碳化硅场效应管结构及其制造工艺。

2、为了解决上述技术问题,本发明通过下述技术方案得以解决:

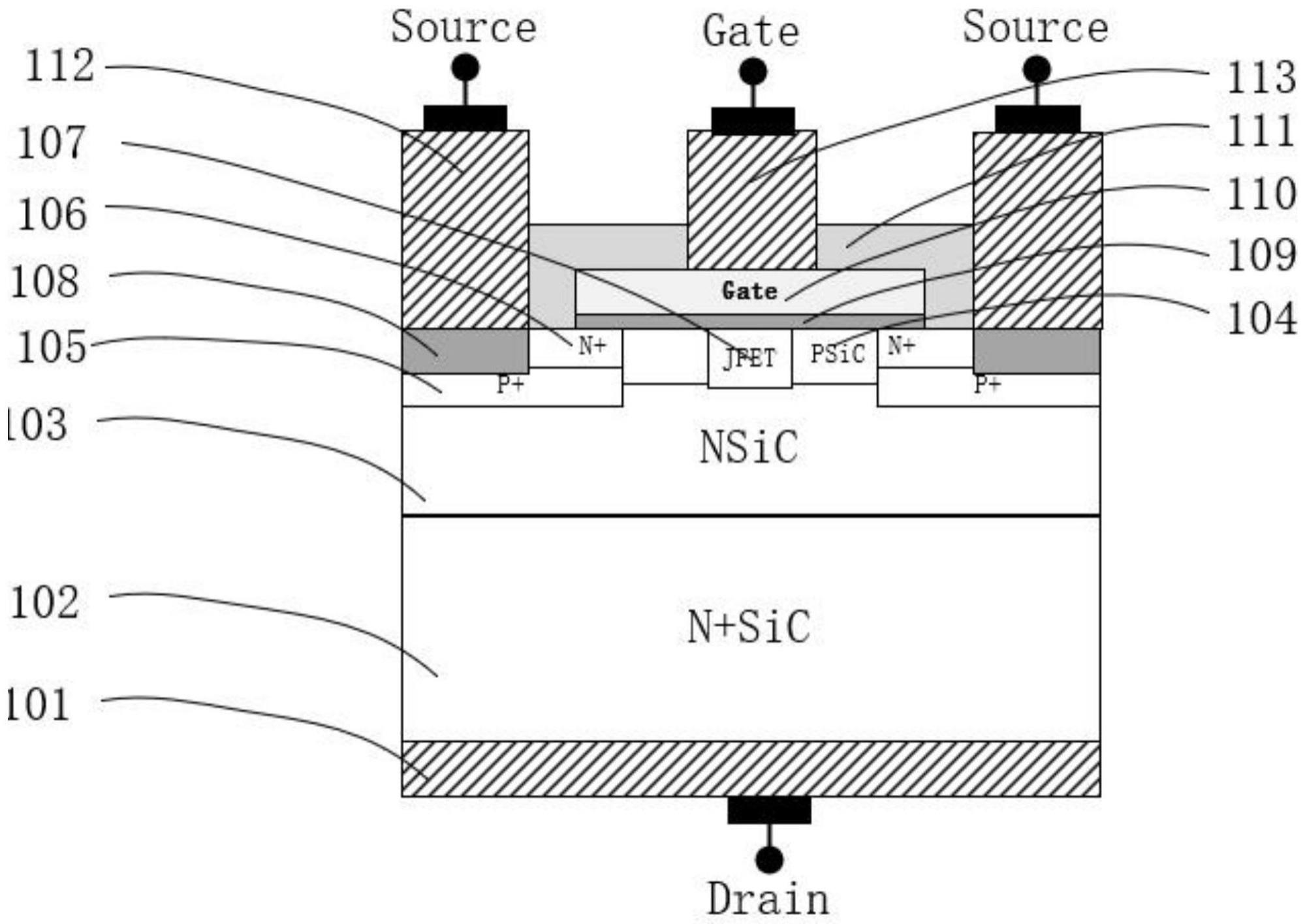

3、一种多次外延平面型碳化硅场效应管结构,包括n型碳化硅衬底,n型碳化硅衬底的下表面设有漏极电极,n型碳化硅衬底的上表面设有外延层,外延层上还设有依次向上排布的栅极结构和源极结构,外延层包括由下至上设置的n型碳化硅外延层和p型碳化硅外延层,n型碳化硅外延层上设有p+注入区、n+注入区和jfet注入区,p+注入区、n+注入区相互接触,位于jfet注入区与p+注入区和n+注入区之间间隔处的p型碳化硅外延层为沟道区,还包括金属硅化物层,金属硅化物层与p+注入区、n+注入区欧姆接触。

4、作为优选,金属硅化物层的下表面与p+注入区接触,金属硅化物层的侧面与n+注入区接触。

5、作为优选,栅极结构包括由下至上依次层叠的栅极氧化层和栅极材料层,栅极氧化层的下表面与jfet注入区、p型碳化硅外延层和部分n+注入区接触。

6、作为优选,还包括源极导电材料层,源极导电材料层设在金属硅化物层上。

7、作为优选,还包括栅极导电材料层,栅极导电材料层设在栅极材料层上。

8、作为优选,还包括绝缘介质层,绝缘介质层包覆在栅极氧化层、栅极材料层和n+注入区外并隔离源极导电材料层和栅极导电材料层。

9、作为优选,n型碳化硅衬底的下表面设有漏极导电材料层,漏极电极设置在漏极导电材料层上。

10、作为优选,n型碳化硅外延层的左右两侧均设有p+注入区和n+注入区,jfet注入区设在n型碳化硅外延层的中部。

11、一种多次外延平面型碳化硅场效应管的制造工艺,包括以下步骤:

12、1)在n型碳化硅衬底上形成n型碳化硅外延层;

13、2)在n型碳化硅外延层上形成p型碳化硅外延层;

14、3)在p型碳化硅外延层上形成第一阻挡层,在未形成第一阻挡层的p型碳化硅外延层上表面上依次注入形成p+注入区和n+注入区,p+注入区与n型碳化硅外延层接触,后去除第一阻挡层;

15、4)在p型碳化硅外延层上形成第二阻挡层,在未形成第二阻挡层的p型碳化硅外延层上表面上使用jfet掩模版注入形成jfet注入区,jfet注入区下表面与n型碳化硅外延层接触,后去除第二阻挡层;

16、5)在p型碳化硅外延层、jfet注入区和部分n+注入区上形成栅极氧化层,在栅极氧化层上沉积形成栅极材料层;

17、6)在n+注入区上形成金属硅化物,金属硅化物与其下方的p+注入区和侧面的n+注入区形成有效的空穴的欧姆接触;

18、7)在金属硅化物上沉积源极导电材料层,在n型碳化硅衬底下表面上沉积漏极导电材料层,在栅极材料层上沉积栅极导电材料层;

19、8)源极导电材料层、漏极导电材料层和栅极导电材料层分别引出源极电极、漏极电极和栅极电极。

20、一种多次外延平面型碳化硅场效应管的制造工艺,包括以下步骤:

21、1)在n型碳化硅衬底上形成n型碳化硅外延层;

22、2)在n型碳化硅外延层上形成p型碳化硅外延层;

23、3)在p型碳化硅外延层上形成第一阻挡层,在未形成第一阻挡层的p型碳化硅外延层上表面上依次注入形成p+注入区和n+注入区,p+注入区与n型碳化硅外延层接触;

24、4)利用步骤3)中形成的第一阻挡层进行高能量斜注入形成jfet注入区,jfet注入区下表面与n型碳化硅外延层接触,后去除第一阻挡层;

25、5)在p型碳化硅外延层、jfet注入区和部分n+注入区上形成栅极氧化层,在栅极氧化层上沉积形成栅极材料层;

26、6)在n+注入区上形成金属硅化物,金属硅化物与其下方的p+注入区和侧面的n+注入区形成有效的空穴的欧姆接触;

27、7)在金属硅化物上沉积源极导电材料层,在n型碳化硅衬底下表面上沉积漏极导电材料层,在栅极材料层上沉积栅极导电材料层;

28、8)源极导电材料层、漏极导电材料层和栅极导电材料层分别引出源极电极、漏极电极和栅极电极。

29、本发明由于采用了以上技术方案,具有显著的技术效果:本技术通过p型碳化硅外延层作为沟道区,减少了工艺造成的缺陷,提高了沟道区的电子迁移率,减少了沟道区的电阻,提高了器件的功率密度;p型碳化硅外延层表面低缺陷率与其上形成的栅极氧化层,可以有效的减少界面态缺陷密度,可以优化栅极可靠性;在有源区采用了金属硅化物工艺,形成欧姆接触的硅化物(silicide),在形成过程中消耗一定厚度的sic材料,使得硅化物的下表面与p+注入区形成空穴的欧姆接触,在侧面形成n+注入区的欧姆接触;有源区金属硅化物工艺,能够让器件不受到传统n+/p+注入层掩模版的工艺窗口限制,有效的缩小了器件的尺寸,此外,本发明还有另一种实施方案可以有效的减少jfet的掩模版,即简化了工艺步骤,又减少制造成本。

- 还没有人留言评论。精彩留言会获得点赞!