一种级联氮化镓功率电路模块封装结构

本发明属于氮化镓功率器件,具体涉及一种级联氮化镓功率电路模块封装结构。

背景技术:

1、近年来,氮化镓(gan)功率器件以其宽带隙、高电子迁移率和高电子速度的优势特性,在新能源发电和电动汽车等高频、高效和高功率密度应用领域受到广泛的关注。然而,现有氮化镓高电子迁移率晶体管(hemt)电流等级比较低,限制了氮化镓hemt器件在高功率应用中的使用。通过gan cascode器件模块并联连接可以提高电流处理能力,满足高功率密度、高频率、集成化的发展需求。

2、传统氮化镓级联(gan cascode)器件封装存在两个问题。第一,传统封装通过引线键合将si mosfet的漏极、源极分别与耗尽型gan hemt的源极、栅极连接。引线键合会带来较大的寄生参数,尤其并联gan器件之间寄生参数不对称问题可能导致器件之间电流不平衡和环路电流,在功率器件关断时,寄生电感会造成关断电压尖峰和振荡,并增加器件损耗,甚至可能导致低压si mosfet雪崩击穿失效。第二,传统封装的散热方式为单面散热,通过将gan芯片焊接在覆铜基板上,通过覆铜基板进行散热,而器件顶部受塑封材料约束,热阻较大,导致器件散热能力差。。

技术实现思路

1、为了解决现有技术中存在的上述问题,本发明提供了一种级联氮化镓功率电路模块封装结构。本发明要解决的技术问题通过以下技术方案实现:

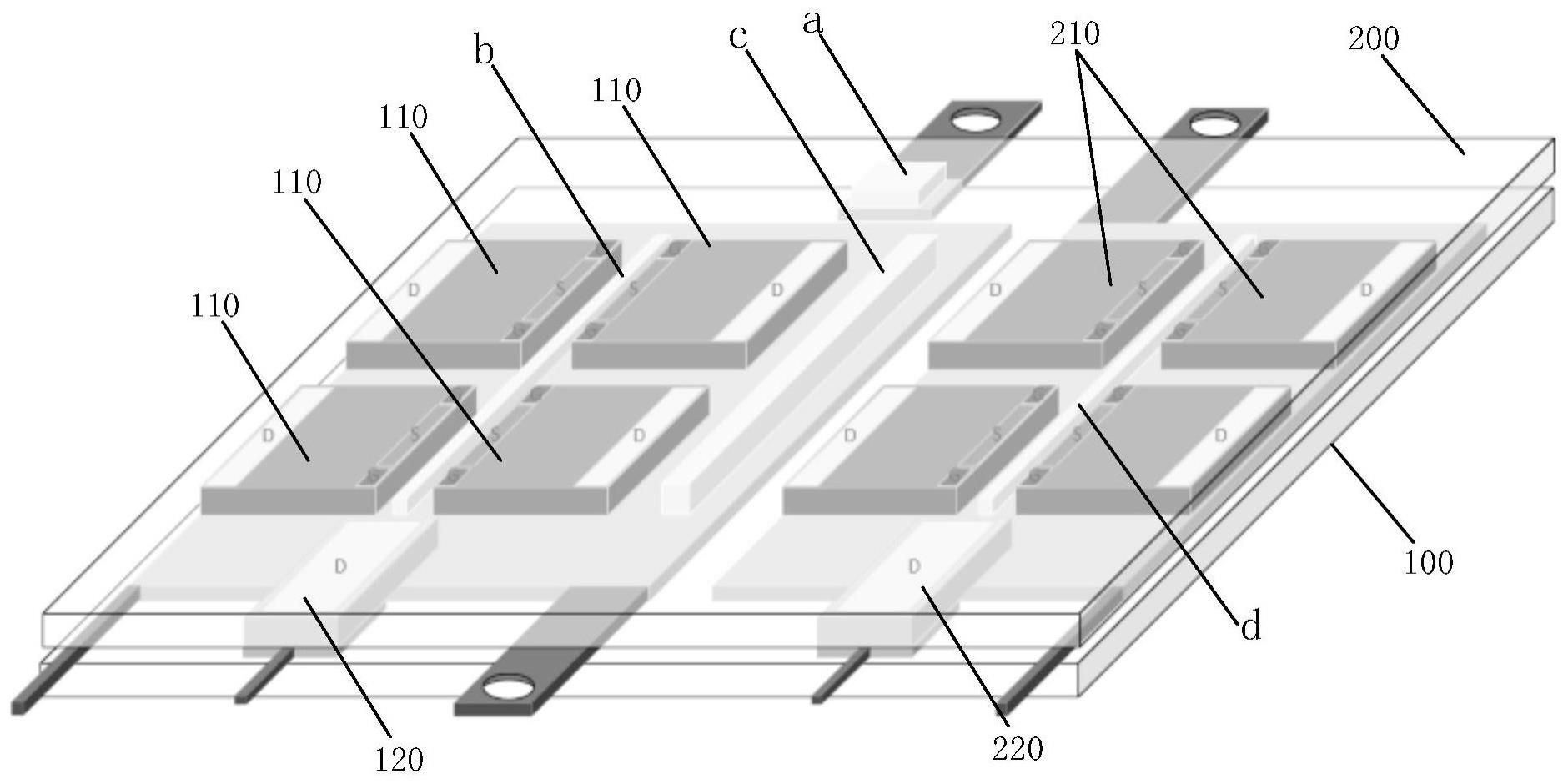

2、一种级联氮化镓功率电路模块封装结构,包括:形成封装体的两个双面覆铜陶瓷基板、至少一个第一级联氮化镓功率电路和至少一个第二级联氮化镓功率电路;

3、所述两个双面覆铜陶瓷基板的板面相对;

4、所述第一级联氮化镓功率电路,包括:四个耗尽型第一氮化镓芯片和一个增强型第一mosfet芯片;

5、所述第一级联氮化镓功率电路与两个双面覆铜陶瓷基板的焊盘和铜柱采用银烧结连接;

6、所述第二级联氮化镓功率电路,包括四个耗尽型第二氮化镓芯片和一个增强型第二mosfet芯片;

7、所述第二级联氮化镓功率电路与两个双面覆铜陶瓷基板的焊盘和铜柱采用银烧结连接;

8、所述两个双面覆铜陶瓷基板的焊盘通过所述铜柱连接。

9、在本发明的一个实施例中,所述四个第一氮化镓芯片并联且与所述第一mosfet芯片互连;

10、所述第一氮化镓芯片与两个双面覆铜陶瓷基板的焊盘和铜柱采用银烧结连接;

11、所述第一mosfet芯片与两个双面覆铜陶瓷基板的焊盘和铜柱采用银烧结连接;

12、所述四个第二氮化镓芯片并联且与所述第二mosfet芯片互连;

13、所述第二氮化镓芯片与两个双面覆铜陶瓷基板的焊盘和铜柱采用银烧结连接;

14、所述第二mosfet芯片与两个双面覆铜陶瓷基板的焊盘和铜柱采用银烧结连接;

15、在本发明的一个实施例中,所述两个双面覆铜陶瓷基板为第一双面覆铜陶瓷基板和第二双面覆铜陶瓷基板;所述铜柱包括:第一子铜柱和第二子铜柱;

16、所述第一氮化镓芯片的衬底和所述第一mosfet芯片的源极及栅极均与所述第一双面覆铜陶瓷基板的焊盘连接;

17、所述第一氮化镓芯片的源极、栅极和漏极以及所述第一mosfet芯片的漏极均与所述第二双面覆铜陶瓷基板的焊盘连接;

18、所述第一子铜柱与所述第一双面覆铜陶瓷基板的焊盘和所述第二双面覆铜陶瓷基板的焊盘连接;

19、所述第二子铜柱与所述第一双面覆铜陶瓷基板的焊盘和所述第二双面覆铜陶瓷基板的焊盘连接。

20、在本发明的一个实施例中,所述第一双面覆铜陶瓷基板的焊盘,包括:第一焊盘、第三焊盘和第四焊盘;

21、所述第一氮化镓芯片的衬底与所述第一焊盘连接;

22、所述第一mosfet芯片的源极与所述第一焊盘连接,所述第一mosfet芯片的栅极与所述第四焊盘连接;

23、所述第三焊盘与所述第一子铜柱连接,所述第一焊盘与所述第二子铜柱连接。

24、在本发明的一个实施例中,所述第二双面覆铜陶瓷基板的焊盘,包括:第六焊盘、第八焊盘、第十焊盘、第十一焊盘和第十二焊盘;

25、所述四个第一氮化镓芯片的栅极依次相连且与所述第十焊盘、所述第十一焊盘和所述第十二焊盘连接;

26、所述第一氮化镓芯片的源极和所述第一mosfet芯片的漏极均与所述第六焊盘连接;

27、所述第一氮化镓芯片的漏极与所述第八焊盘连接;

28、所述第十焊盘、所述第十一焊盘和所述第十二焊盘与所述第二子铜柱连接,所述第八焊盘与所述第一子铜柱连接。

29、在本发明的一个实施例中,所述铜柱还包括第三子铜柱和第四子铜柱;

30、所述第二氮化镓芯片的衬底和所述第二mosfet芯片的源极及栅极均与所述第二双面覆铜陶瓷基板的焊盘连接;

31、所述第二氮化镓芯片的源极、栅极和漏极以及所述第二mosfet芯片的漏极均与所述第二双面覆铜陶瓷基板的焊盘连接;

32、所述第三子铜柱与所述第一双面覆铜陶瓷基板的焊盘和所述第二双面覆铜陶瓷基板的焊盘连接;

33、所述第四子铜柱与所述第一双面覆铜陶瓷基板的焊盘和所述第二双面覆铜陶瓷基板的焊盘连接。

34、在本发明的一个实施例中,所述第一双面覆铜陶瓷基板的焊盘还包括:第二焊盘和第五焊盘;

35、所述第二氮化镓芯片的衬底与所述第二焊盘连接;

36、所述第二mosfet芯片的源极与所述第二焊盘连接,所述第二mosfet芯片的栅极与所述第五焊盘连接;

37、所述第三子铜柱与所述第一焊盘连接,所述第二焊盘与所述第四子铜柱连接。

38、在本发明的一个实施例中,所述第二双面覆铜陶瓷基板的焊盘还包括:第七焊盘、第九焊盘、第十三焊盘、第十四焊盘和第十五焊盘;

39、所述四个第二氮化镓芯片的栅极依次相连且与所述第十三焊盘、所述第十四焊盘和所述第十五焊盘连接;

40、所述第二氮化镓芯片的源极和所述第二mosfet芯片的漏极均与所述第七焊盘连接;

41、所述第二氮化镓芯片的漏极与所述第九焊盘连接;

42、所述第十三焊盘、所述第十四焊盘和所述第十五焊盘与所述第四子铜柱连接,所述第九焊盘与所述第三子铜柱连接。

43、在本发明的一个实施例中,所述第一级联氮化镓功率电路的数量为一个,所述第二级联氮化镓功率电路的数量为一个。

44、在本发明的一个实施例中,所述第一氮化镓芯片的衬底与所述第一mosfet芯片源极为同一电位;

45、所述第二氮化镓芯片的衬底与所述第二mosfet芯片源极为同一电位。

46、本发明的有益效果:

47、1、本发明分别在底部、顶部采用双面覆铜陶瓷基板,并与功率电路直接连接,氮化镓芯片、mosfet芯片通过顶部、底部的双面覆铜陶瓷基板进行散热,能够实现模块顶部、底部双面散热,减少因为器件高温运行带来的效率降低、器件退化问题,可以提升模块的性能与寿命。

48、2、本发明采用了通过焊盘、铜柱将mosfet芯片与氮化镓芯片互连,采用焊盘、铜柱直接互连,减小了因为铝键合线互连而带来的一系列寄生参数,降低了器件的功耗,提升器件的可靠性,在高频应用中进一步提升系统的功率密度。

49、3、本发明将mosfet芯片的源极与氮化镓芯片的衬底采用银烧结连接于同一块焊盘,避免了gan芯片衬底电位浮空带来的影响,将mosfet芯片的源极与氮化镓芯片的衬底端接至同一电位后,在关断状态下,可有效减少衬底中陷阱俘获电子,在导通状态下,也可减小衬底中陷阱电子的释放,器件具有更稳定的动态导通电阻。

50、以下将结合附图及实施例对本发明做进一步详细说明。

- 还没有人留言评论。精彩留言会获得点赞!