一种提高阈值电压一致性的碳化硅半导体器件制造方法与流程

本发明涉及半导体,具体涉及一种碳化硅半导体器件制造方法。

背景技术:

1、mosfet(metal-oxide-semiconductor field-effect transistor),金氧半场效晶体管是一种可以广泛使用在模拟电路与数字电路的场效晶体管(field-effecttransistor)。mosfet依照其“通道”(工作载流子)的极性不同,可分为“n型”与“p型”的两种类型。因其驱动电路简单,开关速度快,在工业领域应用广泛,属于单载流子工作的器件。以碳化硅(sic)材料制作而成的mosfet为例,由于mosfet引起良好的高温特性,开关特性,在汽车和工业电源上得到越来越广泛的应用。

2、sic mosfet用作新能源汽车主驱逆变功率器件,能有效提高电动汽车续航里程。且因其有高工作温度,高功率密度等特点,其在新能源汽车上的应用越来越广泛。但是sicmosfet因为其晶体本身缺陷密度高,表面态密度高,栅氧质量不高等原因,与成熟的硅器件相比,存在一些使用痛点。其中阈值电压的离散性是其中最典型的使用痛点之一,因为它给器件的并联使用带来很高的风险。

3、目前商用的sic mosfet的阈值电压,一般分布在2.5v~3.3v之间,而在车上应用的时候,因为单个芯片的电流能力有限,一般都采用并联的方式,封装成模块使用。如果其中某一芯片阈值电压明显低于其他管子,那么它会早开晚关,承受较大的负载,会提前失效,继而引发整个系统的失效。采用传统侧墙工艺制作的sic mosfet,阈值电压比较离散,在器件的并联使用过程中,会有引发失效的风险。

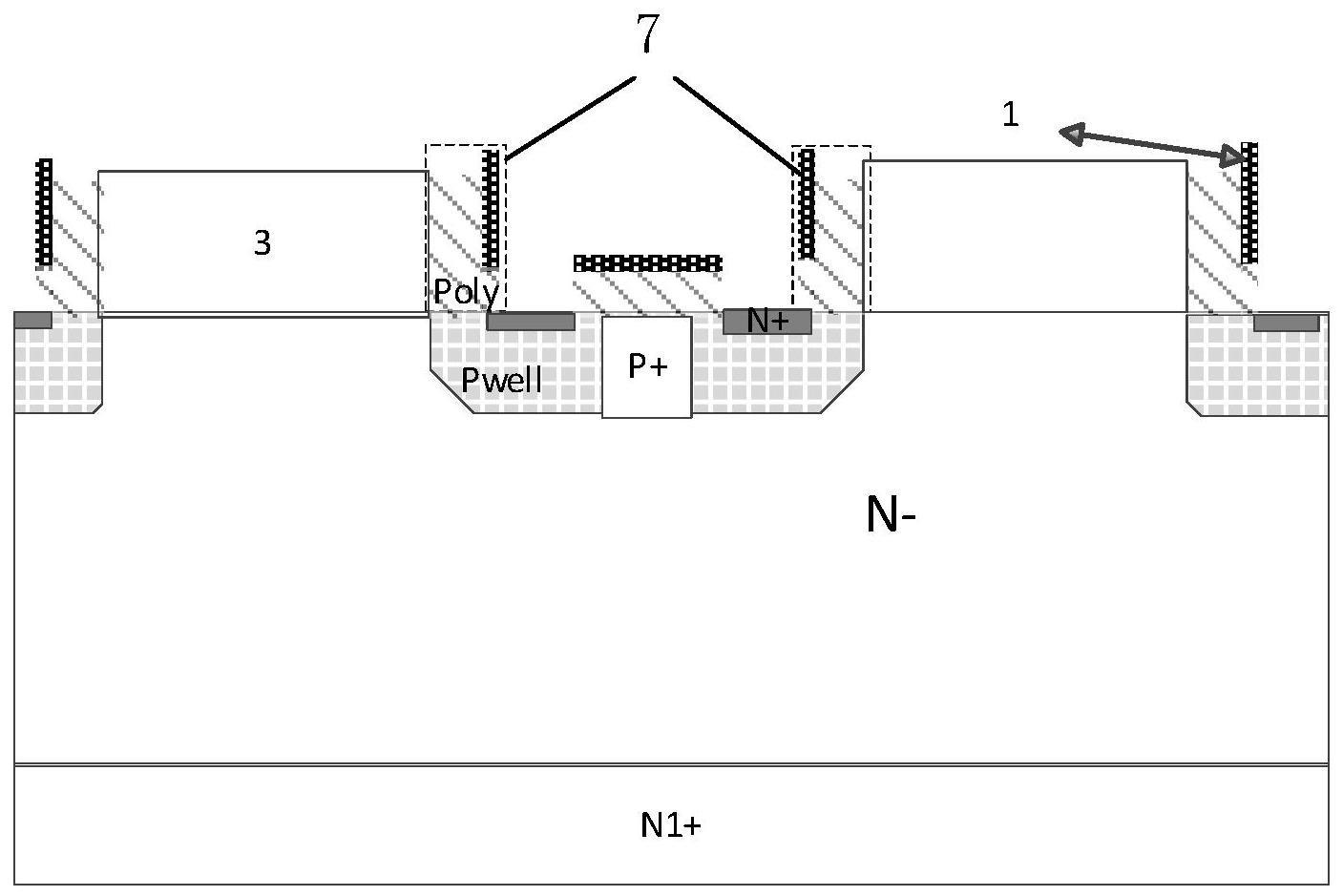

4、常规应用中,如图1,图2所示,为了保证sic mosfet沟道长度一致,通常在第一阱区pwell注入完成后,通过形成侧墙,作为第二掺杂层n+的掩蔽层,进行第二掺杂层n+的离子注入。形成的侧墙形貌如图2所示。但因为在形成侧墙过程中,晶圆边缘和内部干法刻蚀的不均匀性,形成的侧墙会不一致。其一、注入区宽度不一致,主要引起沟道长度差异,在晶圆内部,如果沟道长度差异比较大,必然会引发导通电阻,阈值电压和短路能力的不一致性。其二、侧墙斜边角度不一致,主要会引起第二掺杂层n+杂质的分布不均匀,因为三角形侧墙71是第二掺杂层n+注入的阻挡层,斜面是一个厚度渐变的斜面,如果斜面角度不一致,必然导致杂质分布的差异。如果坡度较小,第二掺杂层n+注入的宽度宽一点,过渡的区域就会比较宽。这个过渡层是n型掺杂和p型掺杂交界的位置,如果过渡区域比较宽,n型杂质和p型杂质相互抵消,形成的高阻区域就比较宽,不但引起导通压降的不一致,也会引起阈值电压的离散。

技术实现思路

1、本发明的目的在于,提供一种提高阈值电压一致性的碳化硅半导体器件制造方法,解决以上技术问题;

2、本发明所解决的技术问题可以采用以下技术方案来实现:

3、一种提高阈值电压一致性的碳化硅半导体器件制造方法,其特征在于,包括,

4、步骤s1,选取一外延片,在所述外延片上通过光刻获得第一离子注入区,进行第一离子的注入获得第一掺杂层(p+),通过光刻获得第二离子注入区,进行第二离子的注入获得第一阱区(pwell);

5、步骤s2,沉积可控制厚度的一多晶硅层(poly),对所述多晶硅层(poly)的表面进行氧化获得可控制厚度的一第一氧化层(1),通过设置阻挡层确定第三离子注入区的蚀刻位置;

6、步骤s3,对所述第一氧化层(1)和所述多晶硅层(poly)进行蚀刻,获得位于所述第一阱区(pwell)的边缘的上方的可控制宽度的矩形状侧墙(7),以及形成所述第三离子注入区;

7、步骤s4,进行第三离子的注入获得第二掺杂层(n+);

8、步骤s5,通过光刻获得第四离子注入区,进行第四离子的注入获得结型场效应区(jfet);

9、步骤s6,形成与所述第一阱区(pwell)和所述第二掺杂层(n+)相对应的接触孔(9),沉积连接所述接触孔(9)的金属电极(metal)。

10、优选的,步骤s1包括,

11、步骤s11,在所述外延片上沉积第二氧化层(2),在所述第二氧化层(2)上通过设置光刻胶(8)定义所述第一离子注入区;

12、步骤s12,在所述第二氧化层(2)上进行光刻形成所述第一离子注入区,以所述第二氧化层(2)为掩膜对所述第一离子注入区进行所述第一离子的注入获得所述第一掺杂层(p+);

13、步骤s13,在所述外延片上重新沉积氧化物形成一第三氧化层(3),在所述第三氧化层(3)上通过设置光刻胶(8)定义所述第二离子注入区;

14、步骤s14,在所述第三氧化层(3)上进行光刻形成所述第二离子注入区,对所述第二离子注入区进行所述第二离子的注入获得所述第一阱区(pwell)。

15、优选的,所述第一掺杂层(p+)位于所在的所述第一阱区(pwell)的中心处,所述第一掺杂层(p+)为p掺杂类型,所述第一阱区(pwell)为p阱区。

16、优选的,步骤s2包括,

17、步骤s21,沉积可控制厚度的所述多晶硅层(poly),对所述多晶硅层(poly)的表面进行氧化获得可控制厚度的所述第一氧化层(1);

18、步骤s22,在位于所述第一掺杂层(p+)上方的所述第一氧化层(1)上设置光刻胶(8)形成所述阻挡层用以确定所述第三离子注入区的蚀刻位置,所述第三离子注入区位于所述第一阱区(pwell)的上端。

19、优选的,步骤s3包括,

20、步骤s31,通过各向异性的方式蚀刻所述第一氧化层(1);

21、步骤s32,向下蚀刻所述多晶硅层(poly),直至露出所述第一阱区(pwell)的表面,在所述第三氧化层(3)的侧面形成所述侧墙(7),在所述第一阱区(pwell)上形成所述第三离子注入区。

22、优选的,步骤s3中,所述侧墙(7)具备可控制的宽度,所述侧墙(7)的宽度为所述多晶硅层(poly)的厚度加上所述第一氧化层(1)的厚度。

23、优选的,步骤s4中,所述第二掺杂层(n+)为n掺杂类型。

24、优选的,步骤s5包括,

25、步骤s51,在所述外延片上重新沉积氧化物形成一第四氧化层(4),在所述第四氧化层(4)上通过设置光刻胶(8)定义所述第四离子注入区;

26、步骤s52,对所述第四离子注入区进行所述第四离子的注入获得所述结型场效应区(jfet)。

27、优选的,步骤s6包括,

28、步骤s61,在所述外延片上形成连接所述第一阱区(pwell),所述第二掺杂层(n+)和所述结型场效应区(jfet)的多晶硅电极(poly2);

29、步骤s62,在所述多晶硅电极(poly2)上形成第五氧化层(5),所述第五氧化层(5)上形成有位于所述第一掺杂层(p+)上方的所述接触孔(9),所述第二掺杂层(n+)和所述第一阱区(pwell)的至少一部分位于所述接触孔(9)下方;

30、步骤s63,在所述第五氧化层(5)上形成连接所述接触孔(9)的所述金属电极(metal)。

31、优选的,所述外延片为n导电类型,所述外延片包括一重掺杂层(n1+)和设于所述重掺杂层(n1+)上方的一轻掺杂层(n-)。

32、本发明的有益效果:由于采用以上技术方案,本发明通过使用矩形的侧墙工艺,不但解决了沟道长度不一致的问题,也解决了第二掺杂离子杂质分布不均匀的问题,大大提高了阈值电压的一致性,为器件在车上并联使用提供了便利。

- 还没有人留言评论。精彩留言会获得点赞!