一种MIS–HEMT器件、电子设备和制造方法与流程

本发明涉及半导体,尤其涉及一种mis–hemt器件、电子设备和制造方法。

背景技术:

1、近年来,关于高电子迁移率晶体管(hemt)的深入研究已经非常普遍,尤其是对于高功率切换和高频率应用。iii族氮化物基hemt利用具有不同带隙的两种材料之间的异质结界面来形成量子阱类结构,所述量子阱类结构容纳二维电子气体(2deg)区,从而满足高功率/频率装置的需求。除了hemt之外,具有异质结构的器件的示例还包括异质结双极晶体管(heterojunction bipolar transistors,hbt)、异质结场效应晶体管(heterojunctionfield effect transistor,hfet)和调制掺杂的fet(modulation-doped fets,modfet)。

2、氮化镓(gan)作为一种宽禁带半导体材料,可以承受更高的工作电压,其功率密度以及可工作温度范围更高,因而gan制备的半导体器件具有高功率密度、低能耗、高频率以及高带宽的优点。

3、mis-hemt(metal-insulator-semiconductor hemt)器件,即金属-绝缘体-半导体结构的高电子迁移率晶体管器件是一种gan hemt器件。mis-hemt器件的静电释放(esd)能力最薄弱处为栅极。针对无esd电路设计或无法设计esd电路的mis-hemt器件,栅极esd能力依靠栅极介质层的介质击穿电压决定,而mis-hemt器件的栅极esd能力普遍小于100v,这就导致在封装器件过程中极大概率造成器件失效。

技术实现思路

1、本发明提供一种mis-hemt器件、电子设备和制造方法,用以解决现有技术中mis-hemt器件存在的栅极的esd能力较弱的问题。

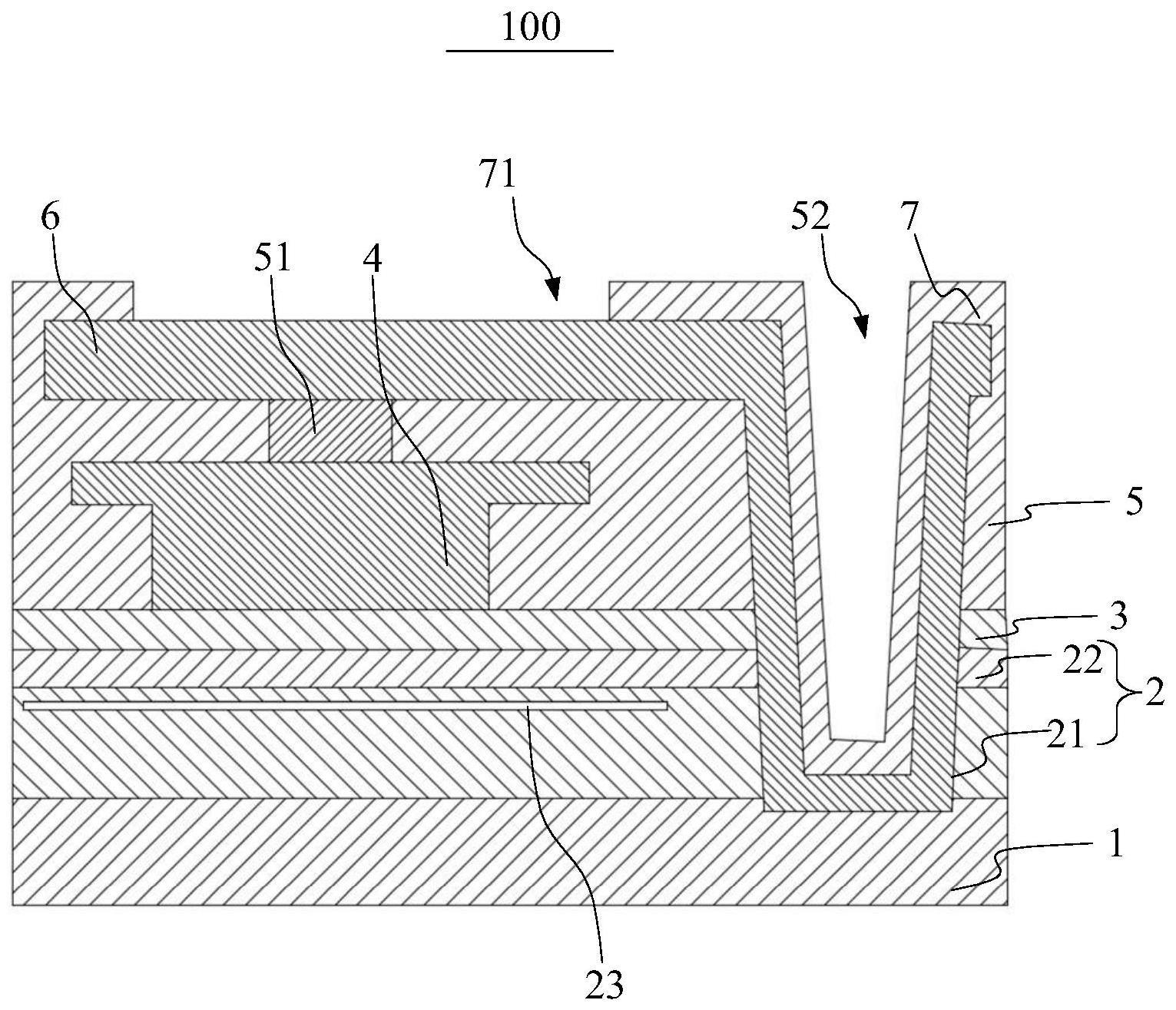

2、本发明提供一种mis-hemt器件,包括:

3、衬底;

4、外延层,形成于所述衬底的一侧;

5、栅极介质层,形成于所述外延层背离所述衬底的一侧;

6、层间介质,形成于所述栅极介质层背离所述外延层的一侧;所述层间介质形成有接触孔和开口;所述开口贯穿所述栅极介质层和所述外延层后延伸至所述衬底;

7、栅极,形成于所述栅极介质层背离所述外延层的一侧,且位于所述层间介质内;

8、栅极顶层金属,通过所述接触孔与所述栅极连接,并通过所述开口与所述衬底连接。

9、根据本发明提供的mis-hemt器件,所述栅极顶层金属包括:

10、覆盖层,通过所述接触孔与所述栅极背离所述栅极介质层的一侧连接;

11、连接件,与所述覆盖层连接,所述连接件位于所述开口内并与所述衬底连接。

12、根据本发明提供的mis-hemt器件,所述连接件形成于所述开口的内壁。

13、根据本发明提供的mis-hemt器件,所述开口的直径沿着朝向所述衬底的方向逐渐减小。

14、根据本发明提供的mis-hemt器件,所述开口设于所述栅极与源极或漏极之间。

15、根据本发明提供的mis-hemt器件,所述层间介质形成有多个所述接触孔;所述源极通过对应的所述接触孔与源极顶层金属连接;所述漏极通过对应的所述接触孔与漏极顶层金属连接。

16、根据本发明提供的mis-hemt器件,所述外延层包括:

17、沟道层,设于所述衬底的一侧;

18、势垒层,形成于所述沟道层背离所述衬底的一侧;且所述势垒层的带隙大于所述沟道层的带隙。

19、根据本发明提供的mis-hemt器件,位于所述外延层内的所述栅极顶层金属与所述外延层内的二维电子气间隔设置。

20、根据本发明提供的mis-hemt器件,还包括:

21、钝化层,形成于所述栅极顶层金属背离所述衬底的一侧;所述钝化层上形成有通孔以露出部分所述栅极顶层金属。

22、根据本发明提供的mis-hemt器件,所述接触孔内填充导电介质,以使所述栅极与所述栅极顶层金属导通。

23、根据本发明提供的mis-hemt器件,填充所述接触孔的导电介质的材料与顶层金属的材料相同或不同;所述顶层金属包括所述栅极顶层金属、源极顶层金属和漏极顶层金属。

24、本发明还提供了一种电子设备,包括上述任一所述的mis-hemt器件。

25、本发明还提供了一种mis-hemt器件的制造方法,用于制造上述任一项所述的mis-hemt器件,包括如下步骤:

26、在衬底的一侧形成外延层;

27、在所述外延层背离所述衬底的一侧形成栅极介质层;

28、在所述栅极介质层背离所述外延层的一侧形成栅极和层间介质,并使所述栅极位于所述层间介质内;

29、在所述层间介质内形成接触孔和开口,并使所述开口贯穿所述栅极介质层和所述外延层后延伸至所述衬底;

30、在所述层间介质远离所述栅极介质层的一侧沉积栅极顶层金属,所述顶层金属通过所述接触孔与所述栅极连接,并通过所述开口与所述衬底连接。

31、根据本发明提供的mis-hemt器件的制造方法,还包括如下步骤:

32、在所述栅极顶层金属远离所述衬底的一侧形成钝化层,且所述钝化层上形成有通孔以露出部分所述栅极顶层金属。

33、本发明提供的一种mis-hemt器件、电子设备和制造方法,通过在层间介质上形成开口,且开口贯穿栅极介质层和外延层延伸至衬底;再结合通过接触孔与栅极连接,同时通孔开口与衬底连接的栅极顶层金属,使栅极端与衬底端等电位,提高了mis-hemt器件栅极的esd能力。而且将本发明的mis-hemt器件进行测试或/和封装的过程中,栅极接收到尖峰电压会直接通过栅极顶层金属导到衬底,而衬底又与接地的晶圆(wafer)承载台,这样就使尖峰电压从mis-hemt器件的栅极到mis-hemt器件的衬底,最后到晶圆(wafer)承载台释放,避免出现栅极介质层直接承受高压而导致被击穿进而使mis-hemt器件失效的问题。

技术特征:

1.一种mis-hemt器件,其特征在于,包括:

2.根据权利要求1所述的mis-hemt器件,其特征在于,所述栅极顶层金属(6)包括:

3.根据权利要求2所述的mis-hemt器件,其特征在于,所述连接件(62)形成于所述开口(52)的内壁。

4.根据权利要求3所述的mis-hemt器件,其特征在于,所述开口(52)的直径沿着朝向所述衬底(1)的方向逐渐减小。

5.根据权利要求1至4任一项所述的mis-hemt器件,其特征在于,所述开口(52)设于所述栅极(4)与源极或漏极之间。

6.根据权利要求1至4任一项所述的mis-hemt器件,其特征在于,所述层间介质(5)形成有多个所述接触孔(51);源极通过对应的所述接触孔(51)与源极顶层金属连接;漏极通过对应的所述接触孔(51)与漏极顶层金属连接。

7.根据权利要求1至4任一项所述的mis-hemt器件,其特征在于,所述外延层(2)包括:

8.根据权利要求7所述的mis-hemt器件,其特征在于,位于所述外延层(2)内的所述栅极顶层金属(6)与所述外延层(2)内的二维电子气间(23)隔设置。

9.根据权利要求1至4任一项所述的mis-hemt器件,其特征在于,还包括:

10.根据权利要求1至4任一项所述的mis-hemt器件,其特征在于,所述接触孔(51)内填充导电介质,以使所述栅极(4)与所述栅极顶层金属(6)导通。

11.根据权利要求10所述的mis-hemt器件,其特征在于,填充所述接触孔(51)的导电介质的材料与顶层金属的材料相同或不同;所述顶层金属包括所述栅极顶层金属(6)、源极顶层金属和漏极顶层金属。

12.一种电子设备,其特征在于,包括权利要求1至11任一项所述的mis-hemt器件。

13.一种mis-hemt器件的制造方法,用于制造权利要求1至11任一项所述的mis-hemt器件,其特征在于,包括如下步骤:

14.根据权利要求13所述的mis-hemt器件的制造方法,其特征在于,还包括如下步骤:

技术总结

本发明涉及半导体技术领域,提供MIS‑HEMT器件、电子设备和制造方法。该器件包括衬底,形成于衬底一侧的外延层;形成于外延层背离衬底一侧的栅极介质层和层间介质;形成于栅极介质层背离外延层一侧的栅极,且栅极位于层间介质内;层间介质还形成有接触孔和开口;开口贯穿栅极介质层和外延层后延伸至衬底。该MIS‑HEMT器件还包括栅极顶层金属,且栅极顶层金属通过接触孔与栅极连接,并通过开口与衬底连接。本发明通过在层间介质上形成贯穿栅极介质层和外延层后并延伸至衬底的开口,再结合通过接触孔与栅极连接,同时通过开口连接于衬底的栅极顶层金属,使栅极端与衬底端等电位,提高了MIS‑HEMT器件栅极的ESD能力。

技术研发人员:张忠宇,胡凯,何惠欣

受保护的技术使用者:英诺赛科(苏州)半导体有限公司

技术研发日:

技术公布日:2024/1/16

- 还没有人留言评论。精彩留言会获得点赞!