多通道P-GANHEMT器件及其提高通道控制能力的制备方法与流程

本发明涉及半导体器件,尤其涉及一种多通道p-gan hemt器件及其提高通道控制能力的制备方法。

背景技术:

1、高迁移率晶体管(hemt)具有击穿场强大、电子迁移率高、热导率高等优点,使得其在电力电子领域有望取代传统硅基器件。p-gan hemt功率器件凭借其常关特性、低功耗、驱动电路简单等优势在高功率电路中得到广泛的应用。

2、多通道p-gan hemt功率器件相较于单通道p-gan hemt功率器件具有更高的电流密度和耐压能力,因此受到更广泛地关注。然而,由于多通道p-gan hemt功率器件的多个通道的特殊结构,2deg距离p-gan越远,关闭通道的难度越大,因此使得p-gan hemt功率器件无法完全关闭通道,容易存在漏电问题。

技术实现思路

1、为了解决上述提出的至少一个技术问题,本发明提供一种多通道p-gan hemt器件及其提高通道控制能力的制备方法,能够提高p-gan hemt功率器件对通道的控制能力,以减少器件漏电。

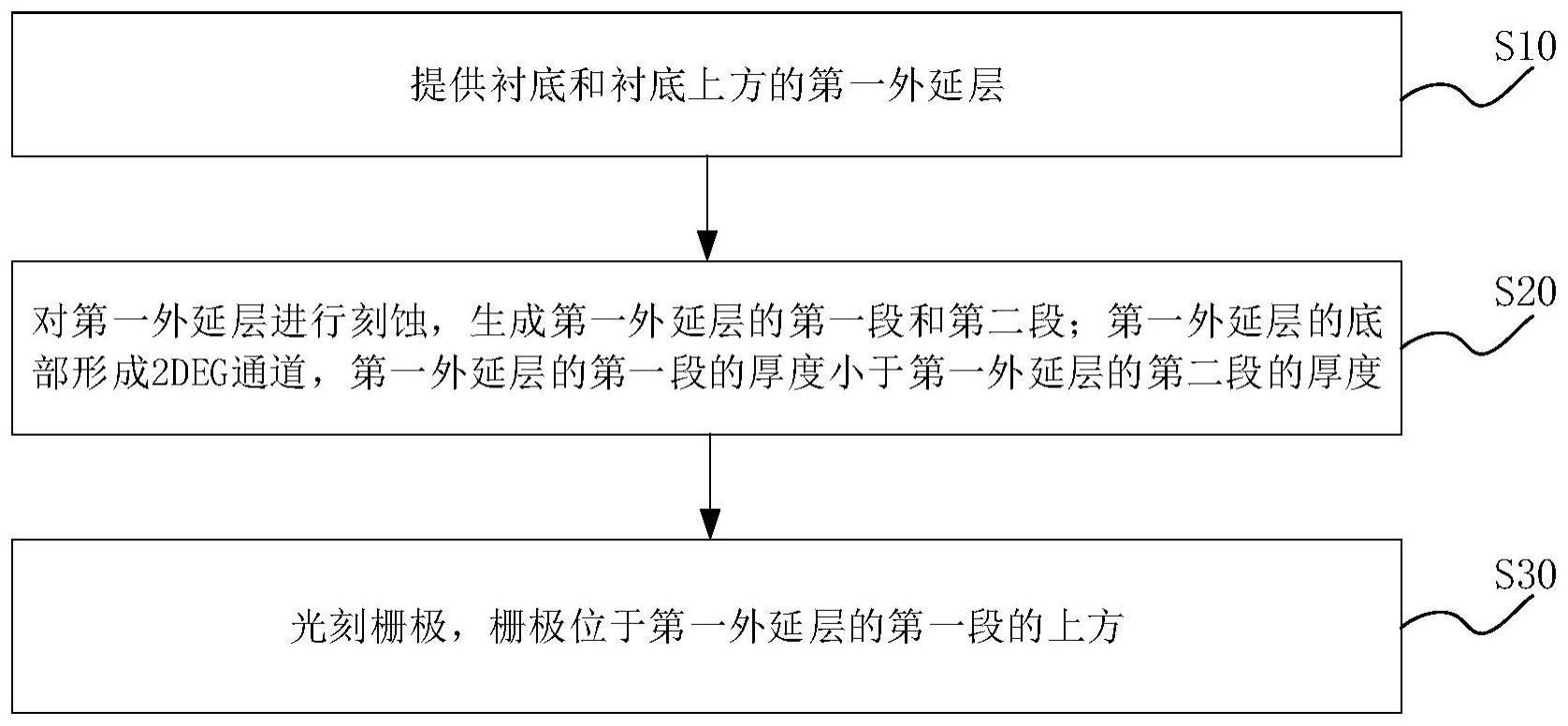

2、本发明提供了一种提高通道控制能力的多通道p-gan hemt器件的制备方法,所述方法包括:

3、提供衬底和所述衬底上方的第一外延层;

4、对所述第一外延层进行刻蚀,生成第一外延层的第一段和第二段;所述第一外延层的底部形成2deg通道,所述第一外延层的第一段的厚度小于所述第一外延层的第二段的厚度;

5、光刻栅极,所述栅极位于所述第一外延层的第一段的上方。

6、在一种可能的实施方式中,对所述第一外延层进行刻蚀,包括:

7、利用台面刻蚀法对所述第一外延层进行刻蚀,形成台面结构。

8、在一种可能的实施方式中,在对所述第一外延层进行刻蚀之前,还包括:

9、在所述衬底上外延出第二外延层;

10、对所述第二外延层进行刻蚀,生成第二外延层的第一段和第二段,所述第二外延层的第一段的厚度大于所述第二外延层的第二段的厚度;

11、在所述第二外延层外延出所述第一外延层。

12、在一种可能的实施方式中,在对所述第一外延层进行刻蚀之后,还包括:

13、在所述第一外延层上外延出第三外延层;

14、在所述第三外延层上外延出第四外延层。

15、在一种可能的实施方式中,所述第二外延层为未掺杂的gan层;所述第一外延层、所述第三外延层及所述第四外延层为algan层。

16、在一种可能的实施方式中,所述第一外延层、所述第三外延层及所述第四外延层的厚度依次减小。

17、在一种可能的实施方式中,在所述第三外延层上外延出第四外延层之后,还包括:

18、在所述第四外延层上沉积钝化层;

19、在所述钝化层上光刻所述栅极;

20、利用光刻或蒸镀方式在所述钝化层上形成源极和漏极;

21、本发明还提供了一种多通道p-gan hemt器件,包括:

22、衬底、在所述衬底上方的第一外延层及栅极;

23、所述第一外延层的底部形成2deg通道,所述第一外延层的第一段的厚度小于所述第一外延层的第二段的厚度;

24、所述栅极位于所述第一外延层的第一段的上方。

25、在一种可能的实施方式中,所述第一外延层的形状包括台面。

26、在一种可能的实施方式中,所述衬底上依次包括第二外延层、第一外延层、第三外延层和第四外延层;

27、所述第二外延层为gan层,所述第一外延层、第三外延层和第四外延层均为algan层;所述第一外延层、所述第三外延层及所述第四外延层的厚度依次减小。

28、与现有技术相比,本发明的有益效果在于:

29、本发明提供了一种提高通道控制能力的多通道p-gan hemt器件的制备方法,所述方法包括:提供衬底和所述衬底上的外延层;对所述外延层进行刻蚀,生成外延层的第一段和第二段;所述第一段的厚度小于所述第二段的厚度;光刻栅极,所述栅极位于所述外延层的第一段的上方。

30、本发明能够在靠近栅极附近的外延层中,提高器件的2deg通道位置,使得2deg通道更加靠近栅极,从而提高栅极对通道的控制能力,减少漏电问题。

31、应当理解的是,以上的一般描述和后文的细节描述仅是示例性和解释性的,而非限制本公开。

技术特征:

1.一种提高通道控制能力的多通道p-gan hemt器件的制备方法,其特征在于,所述方法包括:

2.根据权利要求1所述的提高通道控制能力的多通道p-gan hemt器件的制备方法,其特征在于,对所述第一外延层进行刻蚀,包括:

3.根据权利要求1所述的提高通道控制能力的多通道p-gan hemt器件的制备方法,其特征在于,在对所述第一外延层进行刻蚀之前,还包括:

4.根据权利要求3所述的提高通道控制能力的多通道p-gan hemt器件的制备方法,其特征在于,在对所述第一外延层进行刻蚀之后,还包括:

5.根据权利要求4所述的提高通道控制能力的多通道p-gan hemt器件的制备方法,其特征在于,所述第二外延层为未掺杂的gan层;所述第一外延层、所述第三外延层及所述第四外延层均为algan层。

6.根据权利要求4所述的提高通道控制能力的多通道p-gan hemt器件的制备方法,其特征在于,所述第一外延层、所述第三外延层及所述第四外延层的厚度依次减小。

7.根据权利要求4所述的提高通道控制能力的多通道p-gan hemt器件的制备方法,其特征在于,在所述第三外延层上外延出第四外延层之后,还包括:

8.一种多通道p-gan hemt器件,其特征在于,包括:

9.根据权利要求8所述的一种多通道p-gan hemt器件,其特征在于,所述第一外延层的形状包括台面。

10.根据权利要求8所述的一种多通道p-gan hemt器件,其特征在于,所述衬底上依次包括第二外延层、第一外延层、第三外延层和第四外延层;

技术总结

本发明公开了一种多通道P‑GAN HEMT器件及其提高通道控制能力的制备方法,所述方法包括:提供衬底和所述衬底上的外延层;对所述外延层进行刻蚀,生成外延层的第一段和第二段;所述第一段的厚度小于所述第二段的厚度;在所述外延层上沉积钝化层,在所述钝化层光刻栅极,所述栅极位于所述外延层的第一段的上方。本发明能够在靠近栅极附近的外延层中,提高器件的2DEG通道位置,使得2DEG通道更加靠近栅极,从而提高栅极对通道的控制能力,减少漏电问题。

技术研发人员:黄汇钦

受保护的技术使用者:天狼芯半导体(成都)有限公司

技术研发日:

技术公布日:2024/1/16

- 还没有人留言评论。精彩留言会获得点赞!