减少等离子体引起的损坏的工艺的制作方法

领域本公开内容的实施方式总体涉及薄膜晶体管(tft)和减少在tft中的等离子体引起的损坏的工艺。相关技术描述平板显示器通常用于有源矩阵显示器,诸如计算机和电视机监视器。一般采用等离子体增强化学气相沉积(pecvd)在衬底(诸如用于平板显示器实现方式的透明衬底)上沉积薄膜。pecvd一般通过将前驱物气体或气体混合物引入容纳有衬底的真空腔室中来完成。前驱物气体或气体混合物典型地通过安置在腔室的与衬底相对的顶部附近的分配板被引导朝向衬底。通过将射频(rf)功率从耦接到腔室的一个或多个rf源施加到腔室来将腔室中的前驱物气体或气体混合物激励(例如,激发)成等离子体。所激发的气体或气体混合物进行反应以在所述衬底的表面上形成材料层。通过pecvd技术处理的平坦面板典型地是大的,通常超过数平方米。特别是与用于200mm和300mm半导体晶片处理的气体分配板相比,用于在平坦面板上方提供均匀工艺气流的气体分配板(或气体扩散器板)的尺寸相对地大。此外,由于衬底是矩形的,衬底的边缘,诸如衬底的侧面和拐角,就会经历可能与在衬底的其他部分处所经历的条件不同的条件。这些不同的条件影响处理参数,诸如膜厚度、沉积均匀性和/或膜应力。pecvd经常用于沉积用于tft的膜。由于pecvd工艺的本质,形成了等离子体。等离子体环境可能是严苛的,并且经常导致损坏。甚至可能损坏下层(在所述下层上沉积后续的层)。因此,需要的是具有减少的等离子体损坏的tft和减少等离子体引起的损坏的改善的工艺。

背景技术:

技术实现思路

1、在一个实施方式中,提供了一种薄膜晶体管(tft)。所述tft包括:衬底;栅电极,所述栅电极设置在所述衬底上;栅介质层,所述栅介质层设置在所述栅电极和所述衬底上;半导体层,所述半导体层设置在所述栅介质层上;和源电极与漏电极,所述源电极和所述漏电极设置在所述半导体层上。所述栅介质层具有在约6mv/cm与约10mv/cm之间的击穿场、约5e10 cm-2ev-1至约5e11 cm-2ev-1的界面陷阱密度(dit)和约0.10v至约0.30v的磁滞(hysteresis)。

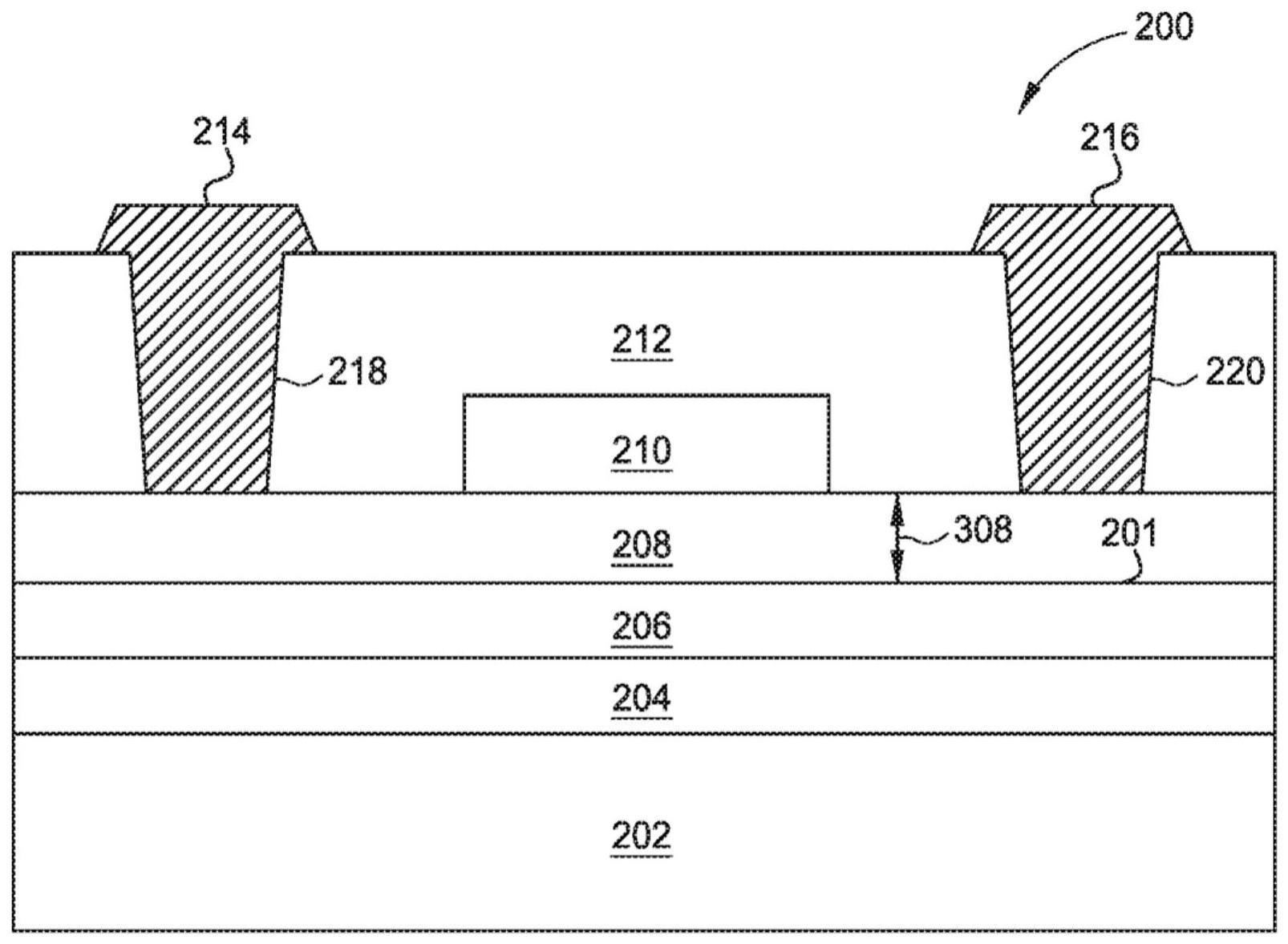

2、在一个实施方式中,提供了一种薄膜晶体管(tft)。所述tft包括:衬底;缓冲层,所述缓冲层设置在所述衬底上;半导体层,所述半导体层设置在所述缓冲层上;栅介质层,所述栅介质层设置在所述半导体层上;栅电极,所述栅电极设置在所述栅介质层上;层间介电(ild)层,所述层间介电层设置在所述栅介质层和所述栅电极上;和源电极与漏电极,所述源电极设置在所述ild层的源电极过孔中,所述漏电极设置在所述ild层的漏电极过孔中。所述栅介质层具有在6mv/cm与约10mv/cm之间的击穿场、约5e10 cm-2ev-1至约5e11 cm-2ev-1的界面陷阱密度(dit)和约0.10v至约0.30v的磁滞。

3、在一个实施方式中,提供了一种制造薄膜晶体管(tft)的方法。所述方法包括:使沉积气体以沉积气体流率流动到腔室的工艺容积中;在初始间隔内以初始功率水平将射频(rf)功率施加到所述沉积气体,从而形成栅介质层的区范围的初始区,所述初始区具有带有最小密度的区密度;和在间隔中增大所述初始功率水平,从而形成所述区范围的区,直到在最终间隔内以最终功率水平施加所述rf功率,从而形成所述区范围内的最终区,所述最终区具有带有最大密度的所述区密度,并且所形成的每个区的所述区密度具有不小于前一个区的所述区密度的密度。

技术特征:

1.一种薄膜晶体管(tft),包括:

2.如权利要求1所述的tft,进一步包括:

3.如权利要求2所述的tft,进一步包括:

4.如权利要求3所述的tft,其中所述栅电极、所述源电极和所述漏电极各自包括铜、钛和含钽材料中的至少一种。

5.如权利要求2所述的tft,其中所述缓冲层包括以下材料中的至少一种:含一氮化硅(sin)和二氧化硅(sio2)的材料,或含sio2的材料。

6.如权利要求1所述的tft,其中所述区厚度为所述厚度的约0.001%至约20%。

7.如权利要求1所述的tft,其中所述栅介质层具有约500埃至约1500埃的厚度。

8.如权利要求1所述的tft,其中所述半导体层包括硅、多晶硅、低温多晶硅、非晶硅、铟镓锌氧化物(igzo)和含氮氧化锌(znon)的材料中的至少一种。

9.如权利要求1所述的tft,其中所述栅介质层包括sin、四氮化三硅(si3n4)、一氧化硅(sio)、二氧化硅sio2和含氮氧化硅si2n2o的材料中的至少一种。

10.一种薄膜晶体管(tft),包括:

11.如权利要求10所述的tft,其中所述区厚度为所述厚度的约0.001%至约20%。

12.如权利要求10所述的tft,其中所述栅介质层具有约500埃至约1500埃的厚度。

13.一种制造薄膜晶体管(tft)的方法,包括:

14.如权利要求13所述的方法,进一步包括:在使所述沉积气体以所述沉积气体流率流动之前,在衬底上形成所述tft的初始层。

15.如权利要求13所述的方法,进一步包括:在所述最终间隔内以所述最终功率水平施加所述rf功率之后,形成所述tft的剩余结构。

16.如权利要求13所述的方法,其中使所述沉积气体以初始压力在所述初始间隔上流动,并且在这些间隔中降低所述初始压力,直到在所述最终间隔上达到最终压力。

17.如权利要求13所述的方法,其中所述初始功率水平在这些间隔中逐步地、指数地或线性地增大,直到以所述最终功率水平施加所述rf功率。

18.如权利要求13所述的方法,其中所述rf功率为约2000瓦(w)至约16000w。

19.如权利要求13所述的方法,其中所述初始功率水平为约2000w至约5000w。

20.如权利要求13所述的方法,其中所述最终功率水平为约12000w至约16000w。

技术总结

本文所描述的实施方式提供了薄膜晶体管(TFT)和工艺以减少在TFT中的等离子体引起的损坏。在一个实施方式中,缓冲层设置在衬底上方,并且半导体层设置在所述缓冲层上方。栅介质层设置在所述半导体层上方。所述栅介质层在界面处接触所述半导体层。栅电极204设置在所述栅介质层上方。所述栅介质层具有约5e<supgt;10</supgt;cm<supgt;‑</supgt;<supgt;2</supgt;eV<supgt;‑1</supgt;至约5e<supgt;11</supgt;cm<supgt;‑2</supgt;eV<supgt;‑1</supgt;的D<subgt;it</subgt;和约0.10V至约0.30V的磁滞以改善所述TFT的性能能力,同时具有在约6MV/cm与约10MV/cm之间的击穿场。

技术研发人员:李建恒,赵来,翟羽佳,崔寿永

受保护的技术使用者:应用材料公司

技术研发日:

技术公布日:2024/1/15

- 还没有人留言评论。精彩留言会获得点赞!