晶体管及其制造方法与流程

本专利文件涉及一种半导体技术,更具体地,涉及一种半导体装置中的晶体管。

背景技术:

1、晶体管是半导体装置的基本单元。随着近来各种小型化、低功率、高性能电子设备使用的增加,需要一种新的晶体管设计来满足减小晶体管的尺寸和功耗的要求。

技术实现思路

1、可以在一些实施例中实施本公开技术,以提供以低成本采用简单工艺制造低能耗的晶体管。也可以在一些实施例中实施本公开技术,以提供用于制造低功耗晶体管的方法。

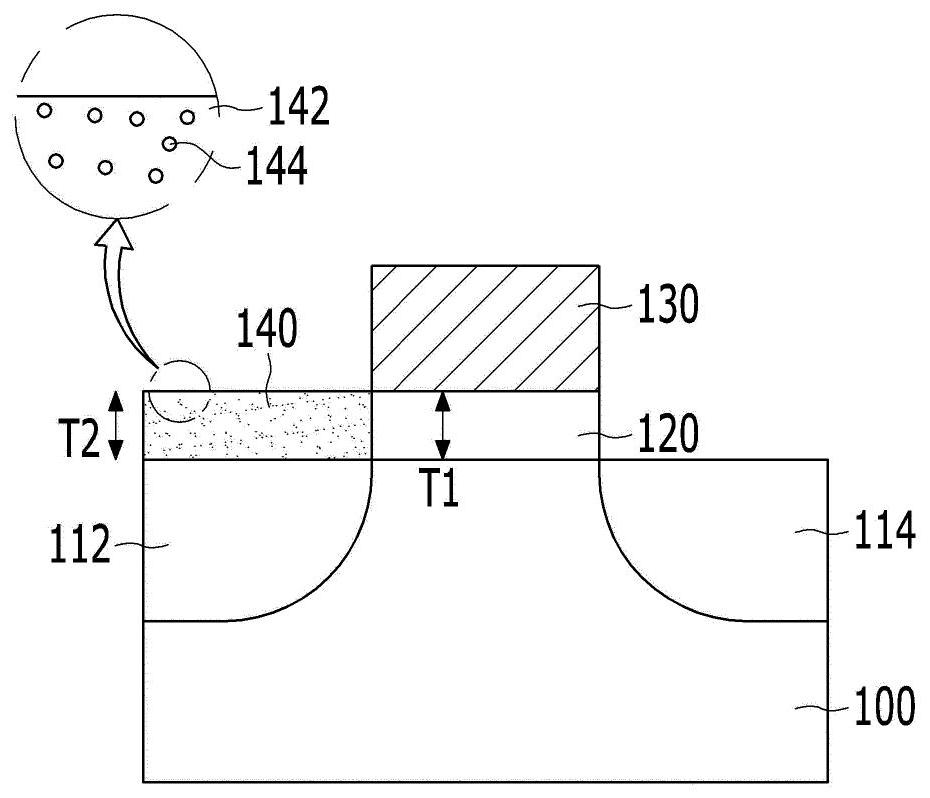

2、在所公开技术的一些实施例中,晶体管可以包括:衬底;设置在所述衬底之上的栅电极;设置在所述栅电极和所述衬底之间的栅绝缘层;形成在所述衬底中的一个或更多个掺杂区;以及设置在所述衬底之上的一个或更多个选择器层,所述一个或更多个选择器层至少一个与所述一个或更多个掺杂区至少一个垂直重叠,其中所述一个或更多个选择器层中的每个包括绝缘材料层和掺杂剂,其中所述绝缘材料层包括与所述栅绝缘层相同的材料,并且所述掺杂剂掺杂在所述绝缘材料层中。

3、在所公开技术的一些实施例中,用于制造晶体管的方法可以包括:在衬底之上形成绝缘材料层;在绝缘材料层的至少第一部分之上形成栅电极;通过注入第一掺杂剂在衬底的第一区域和第二区域形成掺杂区,其中注入第一掺杂剂至与所述栅电极的一侧相邻的所述衬底的第一区域和与所述栅电极的另一侧相邻的所述衬底的第二区域;以及通过将第二掺杂剂注入至绝缘材料层的至少部分中来形成选择器层,所述绝缘材料层设置在所述衬底的第一区域或第二区域中的至少一个之上。

技术特征:

1.一种晶体管,包括:

2.根据权利要求1所述的晶体管,其中,所述一个或更多个选择器层的侧表面直接接触所述栅绝缘层的侧表面。

3.根据权利要求1所述的晶体管,其中,所述一个或更多个选择器层的厚度小于或等于所述栅绝缘层的厚度。

4.根据权利要求1所述的晶体管,其中,选择掺杂在所述绝缘材料层中的掺杂剂以产生浅陷阱,所述浅陷阱提供用于导电载流子在所述绝缘材料层中移动的通路。

5.根据权利要求1所述的晶体管,其中,所述一个或更多个掺杂区包括位于所述栅电极一侧的第一掺杂区和位于所述栅电极另一侧的第二掺杂区,以及

6.根据权利要求1所述的晶体管,其中,所述选择器层包括与所述掺杂区相邻的界面部分,并且包括掺杂在所述掺杂区中的掺杂剂。

7.根据权利要求1所述的晶体管,其中,所述掺杂区包括与所述选择器层相邻的界面部分,并且包括在所述选择器层中的所述掺杂剂。

8.一种用于制造晶体管的方法,包括:

9.根据权利要求8所述的方法,其中,所述绝缘材料层的第二部分未被所述栅电极覆盖,其中所述绝缘材料层的所述第二部分的厚度小于或等于所述绝缘材料层的所述第一部分的厚度。

10.根据权利要求8所述的方法,其中,所述第一掺杂剂或所述第二掺杂剂中的至少一种是通过执行离子注入工艺注入的。

11.根据权利要求8所述的方法,其中,所述第一掺杂剂的注入的投影范围点位于所述衬底中。

12.根据权利要求8所述的方法,其中,所述第二掺杂剂的注入的投影范围点位于所述绝缘材料层中。

13.根据权利要求8所述的方法,还包括:

14.根据权利要求13所述的方法,其中,与所述掺杂区相邻的所述选择器层的界面部分或与所述选择器层相邻的所述掺杂区的界面部分中的至少一个包括所述第一掺杂剂和所述第二掺杂剂。

15.根据权利要求8所述的方法,其中,所述第二掺杂剂产生浅陷阱,所述浅陷阱提供用于导电载流子在所述绝缘材料层中移动的通路。

技术总结

本申请公开晶体管和用于制造晶体管的方法。在一些实施方式中,晶体管包括:衬底;设置在所述衬底之上的栅电极;设置在所述栅电极和所述衬底之间的栅绝缘层;形成在所述衬底中的一个或更多个掺杂区;以及设置在所述衬底之上的一个或更多个选择器层,所述一个或更多个选择器层中的至少一个所述一个或更多个掺杂区中的至少一个垂直重叠,其中所述一个或更多个选择器层中的每个包括绝缘材料层和掺杂剂,其中所述绝缘材料层包括与所述栅绝缘层相同的材料,并且所述掺杂剂掺杂在所述绝缘材料层中。

技术研发人员:宋政桓

受保护的技术使用者:爱思开海力士有限公司

技术研发日:

技术公布日:2024/5/20

- 还没有人留言评论。精彩留言会获得点赞!