一种ESD自保护的高压隔离环的制作方法

本发明属于半导体集成电路,具体涉及一种esd自保护的高压隔离环。

背景技术:

1、静电释放(esd)目前造成ic失效的一大主要原因。esd是指积累的电荷能量以ns级的速度实现放电,可能形成瞬间的高压大电流冲击。产生esd可能是人触摸,设备积累电荷和ic自身积累电荷的泄放。这些esd现象都属于短时间的过负荷,ic管脚短时间内受到尖峰电压或者尖峰电流的冲击,如果这种电压或者电流的能量超过了该管脚能承受的最大额定值,就会造成了ic内部损伤。

2、解决芯片级静电释放esd最直接的方法就是在每个管脚与内部电路之间接入esd器件,在现有技术中,可以用增加各种esd保护器件或esd触发电路模块的方式实现esd保护,而对于高于芯片cmos逻辑电压的高电压管脚需要用到定制的高压esd,由于高压esd的保护需要保证esd保护管的触发电压和维持电压处在被保护管脚的最高工作电压和管脚内部电路的最低击穿电压之间,所以通常同样需要一个高压esd管或者堆叠的低压管来实现高压esd保护,而无论是哪种方案,高压esd管通常都需要占用较大的芯片面积,如果对于这样的高压管脚较多的芯片或者对高压esd防护等级要求较高的芯片,高压esd保护管占用的面积就会很大,由于高压esd管并不参与芯片的主要功能,而仅作为高压管脚esd异常情况下的保护器件,那么如果高压esd保护器件占用了较大的芯片面积就浪费芯片的面积有效利用率,增加了产品成本。

3、因此,提出一种esd自保护的高压隔离环,来解决现有技术存在的面积利用率低的缺点,是本领域技术人员亟需解决的问题。

技术实现思路

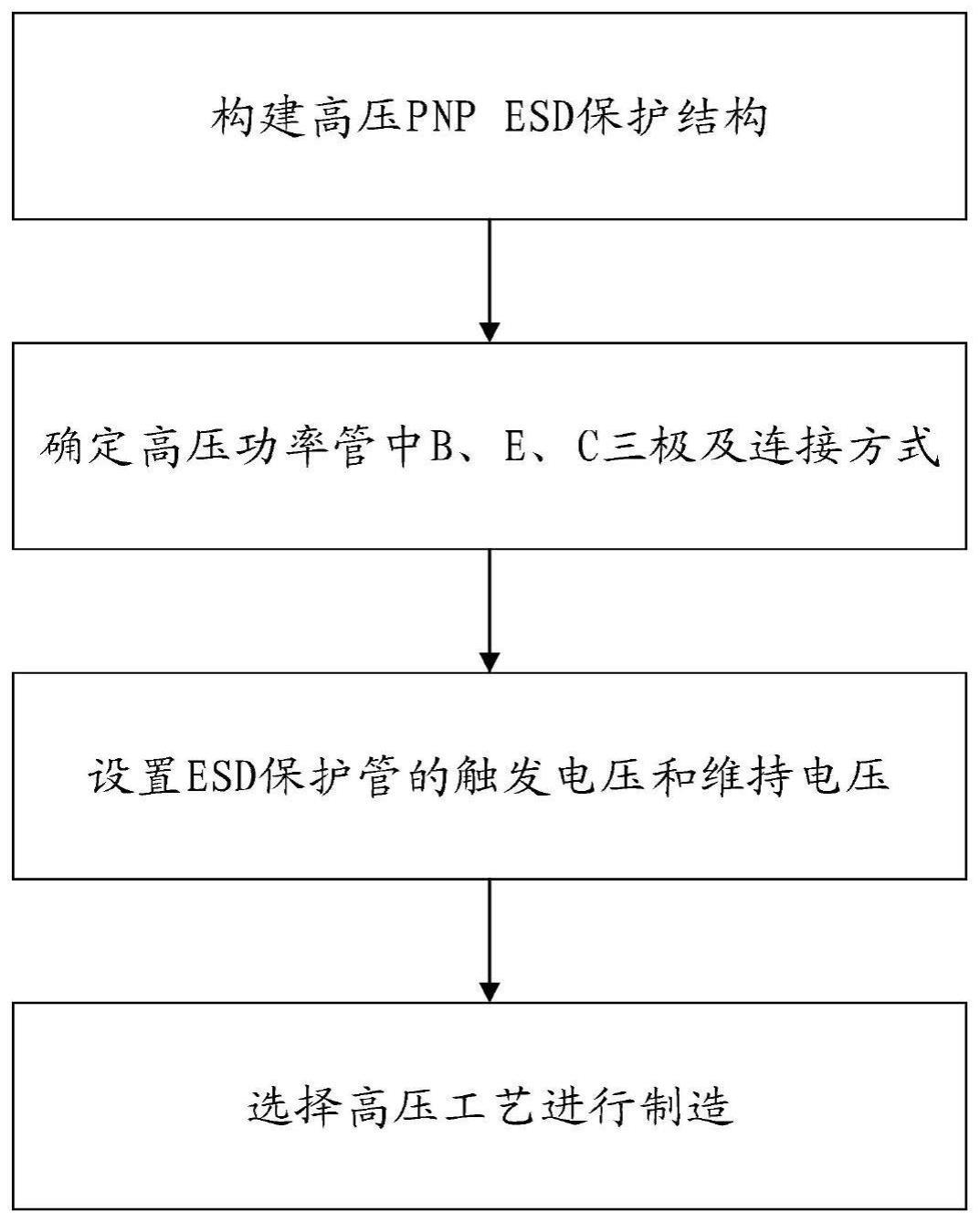

1、有鉴于此,本发明提供了一种esd自保护的高压隔离环,在连接引出管脚的高压管隔离环上实现高压pnpesd保护的结构和实现方法,提出的高压esd结构无需额外的高压esd器件或电路模块,不需要工艺mask层次的增加,也不需要在隔离环外再增加额外占面积较大的掺杂阱,仅利用现有的高压隔离环自身和接地环就可实现高压esd保护,节省了高压esd保护的面积,提升了高压芯片的面积效率。

2、为了实现上述目的,本发明采用如下技术方案:

3、本发明公开了一种esd自保护的高压隔离环,具体的:

4、高压功率管的隔离环作为基极,将其外部的接地环作为集电极,而作为隔离环的n型掺杂阱中插入p型有源区作为发射极形成的pnp结构。

5、上述的方法,可选的,隔离环内作为基极引出的n型有源区和插入的p型有源区,即发射极的引出,通过金属或电阻短接在一起处于同电位。

6、上述的方法,可选的,插入的p型有源区处于靠近接地环一侧,即处于集电极的接地有源区与基极的有源区之间。

7、上述的方法,可选的,插入的p型有源区的宽度l为0.3um~5um。

8、上述的方法,可选的,隔离环采用深n阱隔离高压工艺中的整个深n阱隔离区域或包含n型埋层的高压外延工艺中的引出n阱隔离环。

9、上述的方法,可选的,作为集电极的接地环由有源区引出的p阱形成或带有p型埋层的p阱形成。

10、上述的方法,可选的,触发电压由接地p阱到隔离环n阱的间距s调节,间距的范围为0~5um。

11、经由上述的技术方案可知,与现有技术相比,本发明提供了一种esd自保护的高压隔离环,具有以下有益效果:1)不需要额外增加芯片面积,利用芯片功率开关器件本身的隔离环与衬底地之间形成的寄生的pnp高压esd保护管,特别适合于芯片自身功率开关管自身的面积较大,或者有较多的控制电路放在较大的隔离岛中的芯片,可以实现非常可观的esd保护功能。2)本发明无需增加工艺层次以及额外任何电路结构,仅在隔离中加入p型有源区发射极就可以形成,是一种非常高效,低成本的解决高压esd的集成化保护的创新方案,尤其对于高压esd管脚众多和等级要求较高的芯片,提升有效面积利用率的效果尤其显著。

技术特征:

1.一种esd自保护的高压隔离环,其特征在于,

2.根据权利要求1所述的一种esd自保护的高压隔离环,其特征在于,

3.根据权利要求1所述的一种esd自保护的高压隔离环,其特征在于,

4.根据权利要求1所述的一种esd自保护的高压隔离环,其特征在于,

5.根据权利要求1所述的一种esd自保护的高压隔离环,其特征在于,

6.根据权利要求1所述的一种esd自保护的高压隔离环,其特征在于,

7.根据权利要求1所述的一种esd自保护的高压隔离环,其特征在于,

技术总结

本发明公开了一种ESD自保护的高压隔离环,涉及半导体集成电路技术领域。本发明把高压功率管的隔离环作为基极,将其外部的接地环作为集电极,而作为隔离环的N型掺杂阱中插入P型有源区作为发射极形成的PNP结构。本发明是一种非常高效,低成本的解决高压ESD的集成化保护的创新方案,尤其对于高压ESD管脚众多和等级要求较高的芯片,提升有效面积利用率的效果尤其显著。

技术研发人员:吕宇强

受保护的技术使用者:上海帝迪集成电路设计有限公司

技术研发日:

技术公布日:2024/1/15

- 还没有人留言评论。精彩留言会获得点赞!