制造垂直取向半导体器件的方法以及通过该方法获得的相应垂直取向半导体器件与流程

本公开涉及垂直取向半导体器件,并且更具体地涉及如晶体管或二极管的垂直取向半导体器件,其中在半导体主体中产生阱区。

背景技术:

1、垂直取向半导体器件通常用于功率应用。在这样的器件中,主电流垂直取向,即垂直于半导体器件表面。在晶体管的情况下,漏极接触件可以因此被放置在垂直取向晶体管的底侧。基本晶体管单元可以并排放置在特定芯片上,并且可以并联连接。这是实现高电流分量的常用方法,因此对于分立的高电流功率器件尤其有用。

2、通常,半导体器件是用硅基材料制造的。然而,存在一种趋势值得注意,其中垂直取向半导体器件是用碳化硅基材料制造的。这种类型的材料可以提供更好的性能,尤其是对于高功率和/或高电压半导体器件。

3、碳化硅基半导体器件可以例如具有优于常规硅基半导体器件的多个优点,例如较高的临界击穿场、较高的热导率和较宽的带隙。

4、减小垂直取向晶体管(例如金属氧化物半导体(mos)场效应晶体管(mosfet))的单元尺寸,从而增加每单位面积的沟道密度是提高器件的导电性能的主要方式之一。

5、单元尺寸的这种减小通常受到制造精度和相邻体注入之间为了避免夹断所需的空间的限制。为了对抗传导性能的降低,尤其在体注入之间的区域中使用局部掺杂变化。这些掺杂变化也可能影响器件的寄生电特性,从而也影响动态器件性能。参考文献us2008/169517和文献us2017/077237。

技术实现思路

1、下面阐述了本文公开的某些示例的方面的概述。应当理解,这些方面仅被呈现以向读者提供这些特定实施例的简要概述,并且这些方面不旨在限制本公开的范围。实际上,本公开可以涵盖可能未阐述的各种方面和/或方面的组合。

2、本公开的目的是提供用于制造垂直半导体器件的方法。本公开的另一目的是提供对应的垂直半导体器件。

3、在第一方面,提供了一种制造垂直取向半导体器件的方法,包括以下步骤:

4、提供具有顶表面和第一导电类型的电流调节区的半导体主体;

5、使用掩模,在所述半导体主体的所述顶表面上注入第二导电类型的自由电荷载流子,使得提供所述第二导电类型的阱区,所述阱区横向间隔开,使得在所述半导体材料中的特定深度处在所述阱区间提供所述电流调节区,所述第二导电类型与所述第一导电类型相反;

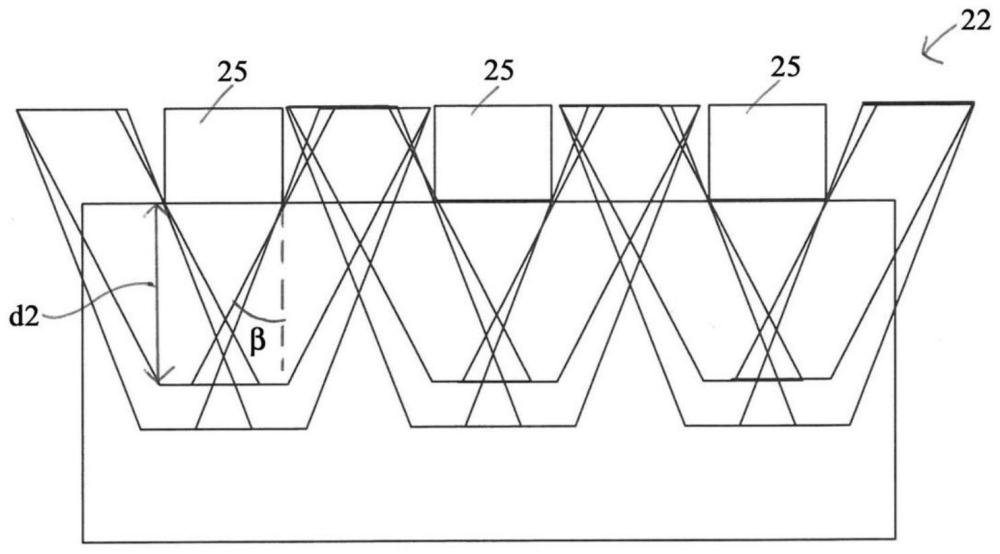

6、其中,在相对于所述顶表面的表面法线的至少两个锐角下执行所述注入,使得在所述半导体材料中提供w形第二导电类型区;

7、从所述顶表面蚀刻所述半导体材料至所述特定深度,使得所述w形第二导电区被分成其间具有所述电流调节区的所述阱区。

8、发明人发现,注入工艺的对准对于在不同沟道之间实现恒定性能可能是重要的。本公开以减少的掩模数量以及改进的掺杂分布来改进自对准注入物的量,从而实现更高的器件性能,如稍后将在下面阐述的。

9、本公开的一个方面是使用相对于顶表面的表面法线成一定角度的注入物,以在半导体材料中产生自对准掺杂分布。

10、使用随后的蚀刻和处理,可以制造在导电路径中具有改善的掺杂分布的小间距的半导体器件。

11、蚀刻进行到这样的深度,使得w形第二导电区被分成阱区。也就是说,在蚀刻之后,结果是提供两个分离的阱区,其中在这两个阱区之间提供电流调节区。

12、在至少两个锐角下执行注入。第一锐角与第二锐角相对于表面法线成镜像。例如,第一角度可以是20度,第二角度可以是-20度。因此,这两个角度在垂直轴上是镜像的,其中垂直轴与半导体材料的顶表面的表面法线重合。

13、在本文的其余部分中,关于垂直取向金属氧化物半导体(mos)场效应晶体管(mosfet)来解释垂直取向半导体器件。然而,应注意,本公开还涉及垂直二极管,例如pn二极管或肖特基二极管。

14、mosfet通常是一种绝缘栅场效应晶体管,其由半导体材料(例如硅或碳化硅材料)制成。栅极端子处的电压决定了器件的电导率。改变电导率的能力可以用于例如放大或切换特定的电子信号。

15、根据本公开,阱区也可以被称为体注入物。通常在这些阱区域中提供相反导电性的源极连接件,以提供mosfet的源极接触件。所谓的电流调节区设置在两个阱区之间。电流调节区可以被认为是结晶型场效应晶体管(junction field-effect transistor,jfet)区。例如,当两个相邻放置的阱区二极管的耗尽宽度随着漏极电压的增加而延伸到半导体器件的漂移区时,jfet区可以限制电流。

16、半导体器件可以包括衬底区,该衬底区设置在与顶表面垂直相对的底表面处,其中衬底区具有第一导电类型。衬底区可以例如连接到mosfet的漏极接触件。这样,电流将根据施加到栅极接触件的电压在源极接触件和漏极接触件之间垂直流动。稍后在下面解释栅极接触件。

17、除了衬底区,例如,外延层(epitaxial layer,epi层)可以设置在衬底区的顶部上以增加半导体器件的击穿电压。epi层可以具有与衬底区相同的导电类型。

18、在典型的mosfet设计中,将在源极接触件和jfet区(即电流调节区)之间建立沟道。在对应的阱区中建立沟道。在沟道的顶部上可以提供电介质层,并且在氧化层的顶部上可以提供栅极接触件。然后,施加到栅极接触件的电压可以影响阱区中存在的自由载流子,使得可以形成沟道。这将在下面参考图1更详细地解释。

19、在示例中,该方法包括以下步骤:

20、使用相同的掩模,在所述半导体主体的所述顶表面上注入所述第一导电类型的另外的自由电荷载流子,其中在相对于所述顶表面的表面法线的不同于所述至少两个锐角的至少两个另外的锐角下执行所述注入,使得在所述半导体材料中提供另外的w形第一导电类型区。

21、上述优点在于,通过使用与用于初始注入步骤的掩模相同的掩模,可以实现掺杂分布的自对准。注入另外的自由电荷载流子实现了产生交替注入浓度的区域,与初始注入相比,这些区域在半导体材料中具有不同的间隔并且可以具有不同的深度。

22、注入另外的自由电荷载流子的步骤可以用于生成金属氧化物半导体(mos)场效应晶体管(fet)的源极注入物。

23、在另一示例中,所述注入的另外的自由电荷载流子在所述半导体材料中的深度与所述注入的自由电荷载流子在所述半导体材料中的深度不同。

24、在另一示例中,垂直取向半导体器件是金属氧化物半导体(mos)场效应晶体管(mosfet),例如碳化硅(sic)mosfet。也就是说,在制造工艺中使用的半导体材料是碳化硅。相比于碳化硅(sic)mosfet的硅对应物,碳化硅(sic)mosfet通常呈现更高的阻断电压、更低的导通状态电阻和更高的热导率,使得它们对于功率应用特别有用。

25、在另一示例中,第一导电类型和所述第二导电类型包括n型和p型半导体材料中的任一种。

26、在又一示例中,该方法还包括以下步骤中的任何步骤:

27、生长或沉积栅极氧化物;

28、制造栅极导线;

29、制造层间电介质;

30、接触蚀刻;

31、金属沉积。

32、在本公开的第二方面中,提供了一种通过根据以上提供的任何示例的方法获得的垂直取向半导体器件。

33、注意,参考本公开的第一方面所解释的优点,即制造垂直取向半导体器件的方法,也适用于本公开的第二方面,即对应的垂直取向半导体器件。

34、注意,根据本公开,可以每次使用相同掩模在半导体主体的顶表面上多次注入第二导电类型的自由电荷载流子,其中对于每次注入,利用不同的锐角。其主要优点在于,第二导电类型的对应阱区可以包括掺杂梯度。

35、掺杂梯度可以例如具有从阱区的一侧到阱区的另一侧单调降低的掺杂浓度。这可以具有优于现有技术阱区的多个优点。

36、结合附图描述本公开。要强调的是,根据工业中的标准实践,各种特征没有按比例绘制。事实上,为了讨论的清楚,各种特征的尺寸可以任意地增加或减小。

37、在附图中,类似的部件和/或特征可以具有相同的附图标记。此外,相同类型的各种部件可通过在附图标记之后加上破折号和区分类似部件的第二标记来区分。如果在说明书中仅使用第一附图标记,则该描述适用于具有相同第一附图标记的类似部件中的任一个,而与第二附图标记无关。

38、参考下文描述的示例,本公开的上述和其他方面将是显而易见的并且将被阐明。

- 还没有人留言评论。精彩留言会获得点赞!