一种合路单元及阵列馈电矩阵机柜的制作方法

本申请涉及射频信号传输,尤其涉及一种合路单元及阵列馈电矩阵机柜。

背景技术:

1、阵列馈电系统通常用于微波暗室半实物仿真系统,将目标模拟器生产的目标回波信号馈入天线单元进行辐射,以模拟目标及环境信号空间角位置。在实验过程中,通常需要将多个不同通道的射频信号进行合成馈入同一天线单元,实现对目标的模拟,合路单元的结构极大地影响系统的性能与复杂程度。

2、过去对多通道阵列馈电系统的信号合成方法一般采用的是直接采用一级x合一合路器(x为系统总的通道数),当合路器的输入通道数较少时,合路器的一致性与公差对系统的影响较小;但当通道数多于6时,单级的合路器已无法满足信号合成过程中公差带来的对结构可靠性的影响。因此需要采用新的设计结构实现多通道的信号合成是十分有必要的。

技术实现思路

1、本申请实施例提供一种合路单元及阵列馈电矩阵机柜,解决了合路器的输入通道数较多,公差带来的可靠性较差的问题。

2、本申请实施例提供一种合路单元,包含多个第一合路器组和一个第二合路器组。所述第一合路器组包含一个末级开关和n个第一合路器。多个所述末级开关均为一选多的开关,用于将一个通道的信号分为多路。所述第一合路器,用于将多个末级开关的一路信号通过第一合路器合成为一个通道的输出信号;每个第一合路器均连接末级开关的一路。所述第二合路器组包含至少n个第二合路器。第一合路器组的n路输出信号分别输入n个第二合路器。第一合路器组的数量与第二合路器的输入通道数对应。

3、进一步地,还包含机柜。所述机柜设置有托盘。所述第一合路器组和所述第二合路器组分别设置在单独的托盘上。

4、进一步地,所述第一合路器组的数量为四个。

5、进一步地,所述末级开关为一选五开关。所述第二合路器的数量为五个。

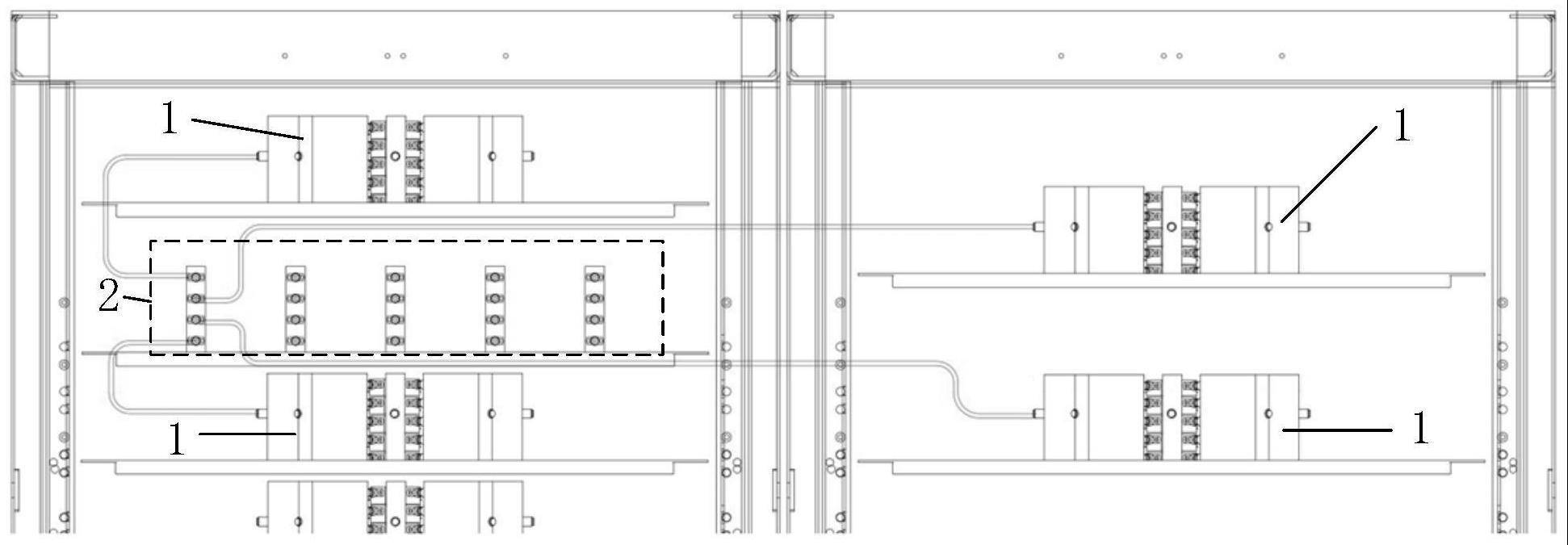

6、进一步地,用托盘作为箱体底面在两个并排放置的所述机柜的同一水平高度上分隔出两个空腔。第一空腔内水平设置两个托盘将空腔在高度方向分为三部分。所述第二合路器组放置在中间部分。两个所述第一合路器组分别放置在上下两个部分。第二空腔设置一个托盘将空腔在高度方向均分为两部分。两个所述第一合路器组分别放置在两部分中。

7、进一步地,所述第一合路器选用五合一合路器。

8、进一步地,多个所述第一合路器的输入端口到第二合路器的电缆长度相同。

9、进一步地,位于第二合路器组上下两侧第一合路器组与第二合路器的电缆在机柜外侧盘起。

10、本申请实施例还提供一种阵列馈电矩阵机柜,其特征在于,所述机柜从上到下设置五个上述任意一项所述合路单元。

11、进一步地,所述机柜中间留出空间。所述空间用于放置其他机柜配件。

12、本申请实施例采用的上述至少一个技术方案能够达到以下有益效果:

13、本申请利用多级合路单元将二十路不同的信号合成后输出,降低了合路器的公差对信号的影响,利用托盘式安装结构减少了多级合路单元连接线缆的长度,降低了插损,兼顾了低损耗与高稳定性等特点,完善了阵列馈电系统合路单元的产品体系。

技术特征:

1.一种合路单元,其特征在于,包含多个第一合路器组和一个第二合路器组;

2.根据权利要求1所述合路单元,其特征在于,还包含机柜;

3.根据权利要求1所述合路单元,其特征在于,所述第一合路器组的数量为四个。

4.根据权利要求1所述合路单元,其特征在于,所述末级开关为一选五开关;

5.根据权利要求2所述合路单元,其特征在于,用托盘作为箱体底面在两个并排放置的所述机柜的同一水平高度上分隔出两个空腔;

6.根据权利要求2所述合路单元,其特征在于,所述第一合路器选用五合一合路器。

7.根据权利要求1所述合路单元,其特征在于,多个所述第一合路器的输入端口到第二合路器的电缆长度相同。

8.根据权利要求7所述合路单元,其特征在于,位于第二合路器组上下两侧第一合路器组与第二合路器的电缆在机柜外侧盘起。

9.一种阵列馈电矩阵机柜,其特征在于,所述机柜从上到下设置五个权利要求1-7任意一项所述合路单元。

10.根据权利要求9所述阵列馈电矩阵机柜,其特征在于,所述机柜中间留出空间;

技术总结

本申请公开了一种合路单元及阵列馈电矩阵机柜,解决了合路器的输入通道数较多,公差带来的可靠性较差的问题。一种合路单元,包含多个第一合路器组和一个第二合路器组。所述第一合路器组包含一个末级开关和N个第一合路器。多个所述末级开关用于将一个通道的信号分为多路。所述第一合路器,用于将多个末级开关的一路信号通过第一合路器合成为一个通道的输出信号;每个第一合路器均连接末级开关的一路。所述第二合路器组包含N个第二合路器。第一合路器组的N路输出信号分别输入N个第二合路器。第一合路器组的数量与第二合路器的输入通道数对应。本申请利降低了合路器的公差对信号的影响,降低了插损,完善了阵列馈电系统合路单元的产品体系。

技术研发人员:何逸箫,徐源,王丹华,李呈柯,贾治国

受保护的技术使用者:北京无线电计量测试研究所

技术研发日:

技术公布日:2024/1/15

- 还没有人留言评论。精彩留言会获得点赞!