一种基于一体化平面耗尽型结终端的功率器件制备方法与流程

本发明涉及功率器件,特别涉及一种基于一体化平面耗尽型结终端的功率器件制备方法。

背景技术:

1、igbt功率器件作为必需的核心开关器件,广泛应用在各种电能变换领域,如光伏、风能、充电储能、新能源汽车等。功率器件根据耐压能力不同可以分为不同的规格系列,比如600v、1200v、1700v等,硅基器件最高耐压能达到6500v,sic器件的最高耐压能够达到数万伏。功率器件之所以能够实现数千伏的耐压能力,是因为在功率芯片的设计结构中主要包含原胞区和终端区两大主要部分,其中终端区的功能就是实现芯片的耐压能力。

2、理论上讲,p+n-的平行平面结的击穿电压是芯片能够实现的最高电压。如图1所示,p+n-结在反偏电压的作用下产生耗尽层,n-区由于掺杂较低,会产生很宽的耗尽层,耗尽层的电场方向由n区指向p区。具有场截止功能的功率器件(field stop型)具有一个n+场截止区,用于截止电场。电场区与代表漂移区厚度的横轴围成的面积与器件的外加电压相等;当外加电压达到一定数值时,p+n-结处的电场达到最大值em,此时会因碰撞电离产生雪崩倍增效应,漏电流瞬间增大,pn结两端的电压不会再继续增大;此时的电压值被称为pn结的击穿电压,即pn结的最高耐压值。实际的功率芯片不可能设计成无限延展的平行平面结,只能通过结终端结构在芯片的外周形成柱面结或球面结将pn结电场收敛起来。

3、结终端技术经历了平面扩散型终端、台面终端、浮空场环终端、多级浮空场环终端、场环场板结合型终端等多代技术的发展。目前,在功率器件领域里应用最广泛的终端是多级场环场板结合型终端。该类型终端利用p+型重掺杂的浮空场环注入,在器件反偏工作时能够轻松耗尽n-型衬底,在多级浮空场环的作用下,反偏耗尽层得到有效扩展,能实现较高的终端效率。理论上如果不考虑芯片的利用率,可以设计很多个环逐渐的收敛平面结电场,使芯片的耐压尽可能的接近理想pn结击穿电压。

4、现有多级场环场板技术是一种应用非常广泛的结终端技术,但依然存在着如下问题:

5、问题1.设计相对复杂,多级场环场板结终端结构的耐压能力受场环的浓度、数量、宽度、间距、场板长度、场板高度等诸多因素的影响,给设计工作带来比较高的难度;为了设计出更高终端效率的终端结构,往往需要进行大量的运算工作。

6、问题2.终端效率低,理论上多级场环场板结终端的终端效率与浮空场环的数量成正比,也就是说为了获得更高的终端效率,可以在设计环节加入更多的终端环数量,换取更高的终端耐压;但是,即便如此场环场板型结终端的终端效率也很难高于85%。

7、问题3.较大的终端面积,会使得芯片的面积相应增大,进而使芯片的成本增加,竞争力下降。如果以相同的芯片面积为前提,就会牺牲原胞区的有效面积,影响芯片的各项参数。比如影响芯片的额定电流,增加芯片的开关损耗等。

8、问题4.电场均担实现难度高、可靠性差,理想的多级场环场板结构在每个环上的电场分布呈均匀分布,这样能够实现较高的终端效率同时,芯片终端的漏电流也最小,如图4所示。然而实际设计中很容易出现类似于图5甚至比图5更差的表面电场分布情况。有的场环电场很弱,没有起到作用;而有的场环电场峰值总是很高,承受压力较大,容易疲劳以及优先击穿,且漏电大、工作不稳定、寿命段等可靠性风险突出。

9、问题5.表面工艺复杂,场环场板结构往往需要多道工艺实现,为了使浮空场板与场环相连需要将芯片表面的氧化层刻蚀成接触孔,并淀积金属;在氧化层刻蚀与金属填充环节,容易形成填充孔隙,影响芯片的可靠性;同时,在工艺过程中也容易受离子沾污的影响,造成芯片性能降低,也会影响可靠性。

技术实现思路

1、本发明实施例的目的是提供一种基于一体化平面耗尽型结终端的功率器件制备方法,通过采用宽区域氧化隔离和超轻掺杂一体化p-型终端结类型结构,实现了栅极结构与终端结构的有效集成,并利用轻掺杂的p-型终端和n-型衬底电荷平衡原理提高了芯片耐压性能,且有效提高了芯片有源区的面积占比,显著提高芯片的功率密度。

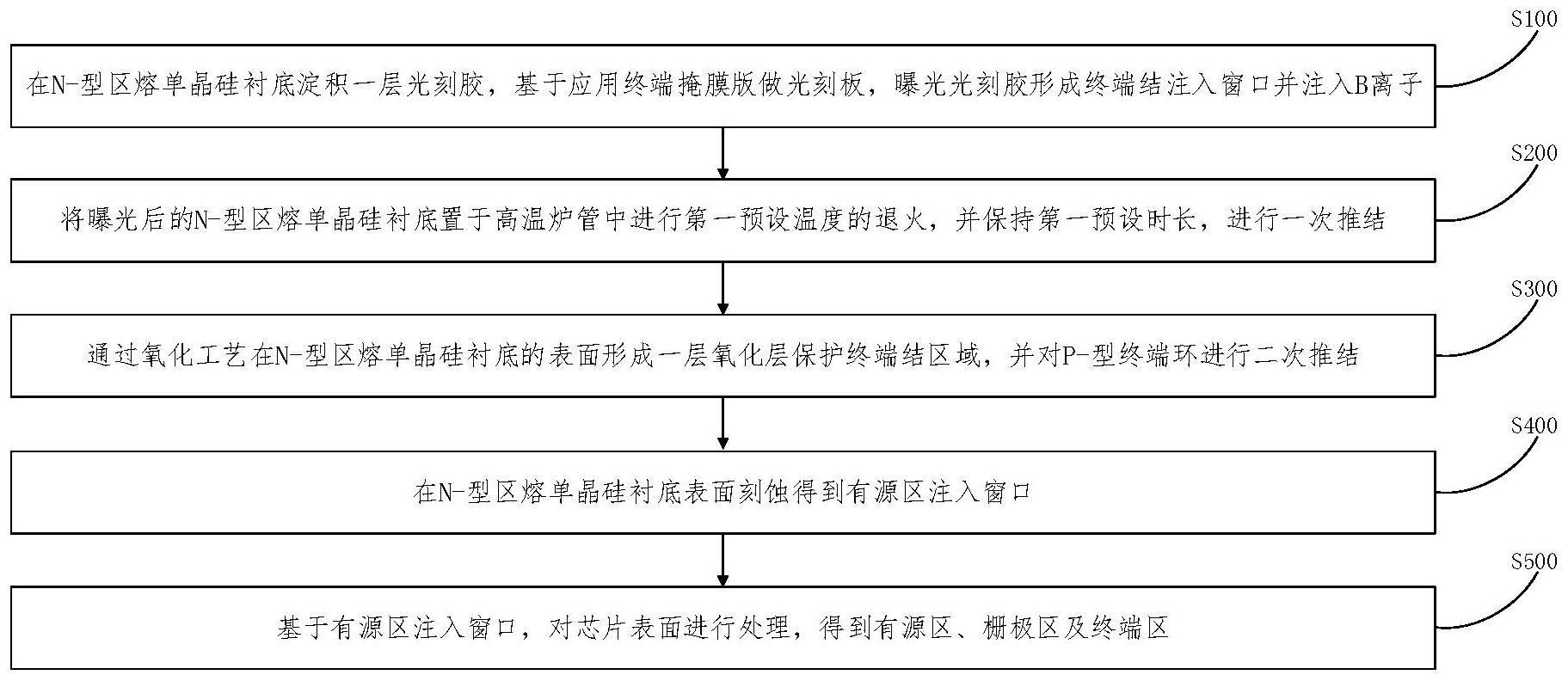

2、为解决上述技术问题,本发明实施例提供了一种基于一体化平面耗尽型结终端的功率器件制备方法,包括如下步骤:

3、在n-型区熔单晶硅衬底淀积一层光刻胶,基于应用终端掩膜版做光刻板,曝光光刻胶形成终端结注入窗口并注入b离子;

4、将曝光后的所述n-型区熔单晶硅衬底置于高温炉管中进行第一预设温度的退火,并保持第一预设时长,进行一次推结;

5、通过氧化工艺在所述n-型区熔单晶硅衬底的表面形成一层氧化层保护终端结区域,并对p-型终端环进行二次推结;

6、在所述n-型区熔单晶硅衬底表面刻蚀得到有源区注入窗口;

7、基于有源区注入窗口,对芯片表面进行处理,得到有源区、栅极区、终端区。

8、进一步地,所述在n-型区熔单晶硅衬底淀积一层光刻胶之前,还包括:

9、基于湿法氧化工艺在n-型区熔单晶硅衬底形成第一预设厚度的氧化层,并基于湿法复式工艺将所述氧化层去除并清洗。

10、进一步地,所述b离子的注入量为1e12-1 e13,所述终端结注入窗口的宽度为200um-300um。

11、进一步地,所述第一预设温度的数值范围为1050℃-1200℃,所述第一预设时长的数值范围为100min-200min。

12、进一步地,所述氧化工艺的氧化层厚度为1um-2um,p-型结的推进深度为6um-12um。

13、进一步地,所述通过氧化工艺在所述n-型区熔单晶硅衬底的表面形成一层氧化层保护终端结区域,包括:

14、通过湿氧氧化工艺在所述n-型区熔单晶硅衬底的表面形成一层氧化层保护终端结区域;或者,

15、通过locos氧化工艺在所述n-型区熔单晶硅衬底的表面形成一层氧化层保护终端结区域。

16、进一步地,当所述采用湿氧氧化工艺在所述n-型区熔单晶硅衬底的表面形成一层氧化层时,所述在所述n-型区熔单晶硅衬底表面刻蚀得到有源区注入窗口,具体为:

17、在所述n-型区熔单晶硅衬底表面涂覆光刻胶后,利用有源区光刻版曝光有源区,并刻蚀掉有源区的氧化层,得到有源区注入窗口。

18、进一步地,所述通过locos氧化工艺在所述n-型区熔单晶硅衬底的表面形成一层氧化层保护终端结区域之前,还包括:

19、在所述n-型区熔单晶硅衬底表面淀积一层si3n4后涂覆光刻胶,再利用所述应用终端掩膜板曝光p-注入窗口,随后刻蚀掉注入窗口的si3n4后进行p-型离子注入。

20、进一步地,所述在所述n-型区熔单晶硅衬底表面刻蚀得到有源区注入窗口,包括:

21、在所述n-型区熔单晶硅衬底腐蚀掉si3n4层,得到有源区注入窗口。

22、本发明实施例的上述技术方案具有如下有益的技术效果:

23、通过采用宽区域氧化隔离和超轻掺杂一体化p-型终端结类型结构,实现了栅极结构与终端结构的有效集成,并利用轻掺杂的p-型终端和n-型衬底电荷平衡原理提高了芯片耐压性能,且有效提高了芯片有源区的面积占比,显著提高芯片的功率密度。

- 还没有人留言评论。精彩留言会获得点赞!