碳化硅器件及其制备方法与流程

本发明涉及半导体,尤其涉及一种碳化硅器件及其制备方法。

背景技术:

1、碳化硅器件碳化硅(sic)材料因其优越的物理特性,广泛受到人们的关注和研究。其高温大功率电子器件具备输入阻抗高、开关速度快、工作频率高、耐高温高压等优点,在开关稳压电源、高频加热、汽车电子以及功率放大器等方面取得了广泛应用。

2、现有的碳化硅器件的栅极氧化层的形成通常是以高温氧化方式来实现。通过加热碳化硅表面来生长二氧化硅。碳化硅(silicon carbide,sic)的氧化过程会于氧化物/碳化硅界面层产生积聚碳团及高密度的积存电荷,而且sic/sio2界面粗糙,存在较多的界面缺陷。又因为sio2的介电常数较低,常常会出现栅极氧化层提前击穿的现象。

技术实现思路

1、本发明的主要目的在于提供一种碳化硅器件及其制备方法,旨在解决现有的碳化硅器件常出现栅极氧化层提前击穿的问题。

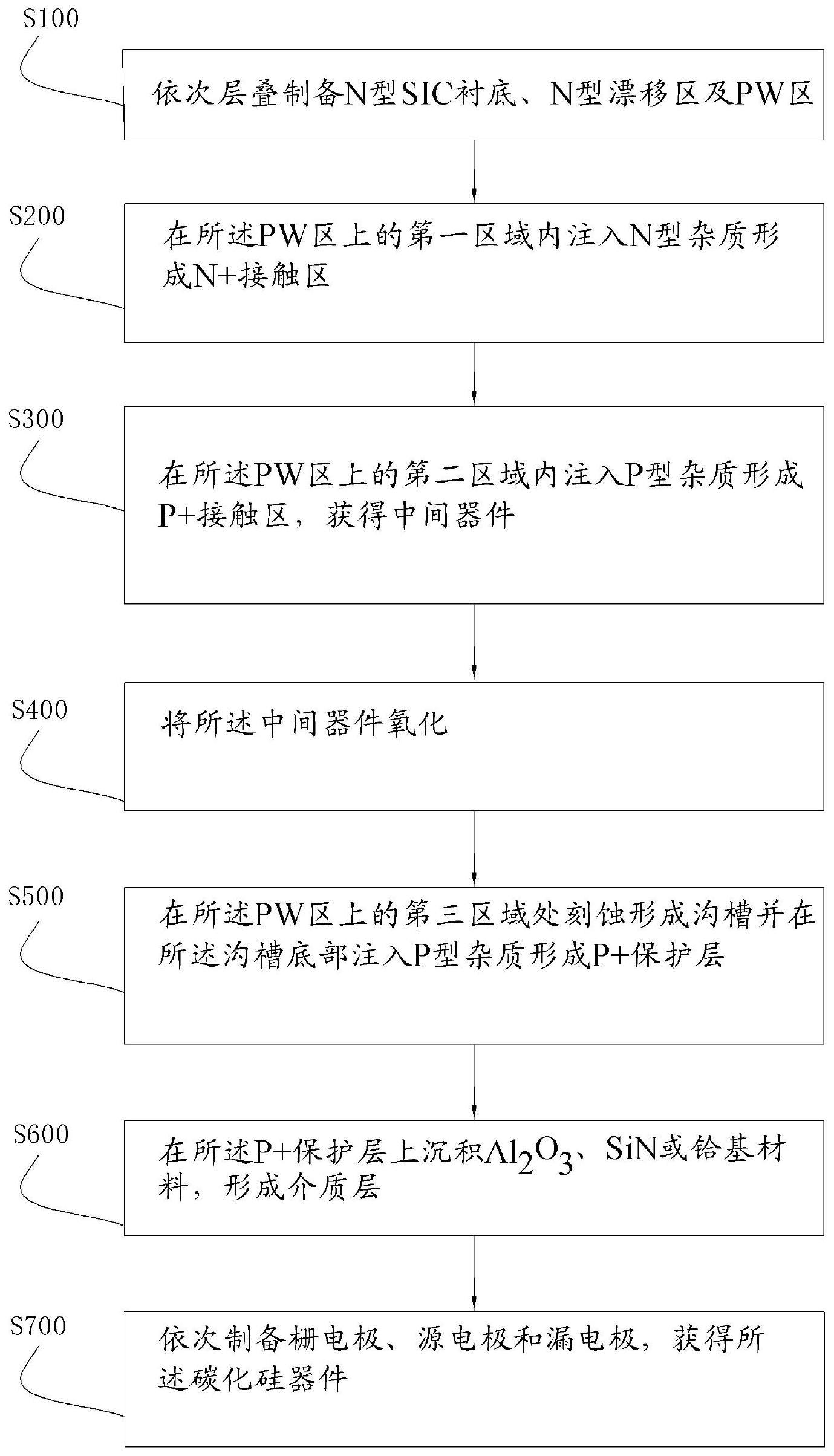

2、为实现上述目的,本发明提供一种碳化硅器件的制备方法,包括以下步骤:

3、依次层叠制备n型sic衬底、n型漂移区及pw区;

4、在pw区上的第一区域内注入n型杂质形成n+接触区;

5、在pw区上的第二区域内注入p型杂质形成p+接触区,获得中间器件,其中,所述p+接触区延伸至所述n型漂移区;

6、将所述中间器件氧化;

7、在pw区上的第三区域处刻蚀形成沟槽并在所述沟槽底部注入p型杂质形成p+保护层,其中,所述p+保护层覆盖所述沟槽底部的拐角处,所述第一区域、第二区域及所述第三区域互不相同;

8、在所述p+保护层上沉积al2o3、sin或铪基材料,形成介质层;

9、依次制备栅电极、源电极和漏电极,获得所述碳化硅器件。

10、优选地,所述依次层叠制备n型sic衬底、n型漂移区及pw区的步骤包括:

11、通过浓度为1e17/cm3-1e19/cm3的n型sic生长形成n型sic衬底;

12、通过浓度为1e14/cm3-1e16/cm3的n型sic在所述n型sic衬底上生长形成所述n型漂移区;

13、通过1e17/cm3-5e17/cm3的p型杂质在所述n型漂移区上生长形成所述pw区。

14、优选地,所述在pw区上的第一区域内注入n型杂质形成n+接触区的步骤包括:

15、在所述pw区上铺设一层光刻胶;

16、将所述第一区域处对应的所述光刻胶剔除,以露出所述第一区域下方的所述pw区;

17、将浓度为1e18/cm3-1e19/cm3的n型杂质注入所述第一区域下方的所述pw区,形成所述n+接触区。

18、优选地,所述在pw区上的第二区域内注入p型杂质形成p+接触区,获得中间器件的步骤包括:

19、在所述pw区上铺设一层光刻胶;

20、将所述第二区域处对应的所述光刻胶剔除,以露出所述第二区域下方的所述pw区,其中,所述第二区域位于所述pw区的边缘,且两个所述第一区域均位于两个所述第二区域之间;

21、将浓度为1e18/cm3-1e19/cm3的p型杂质注入所述第一区域下方的所述pw区,形成所述p+接触区,获得所述中间器件,其中,所述p+接触区贯通所述pw区并延伸至所述n型漂移区。

22、优选地,所述将所述中间器件氧化的步骤包括:

23、将所述中间器件放入扩散炉中,以1700℃~1900℃对所述中间器件加热200min~300min,以使所述中间器件氧化。

24、优选地,所述在pw区上的第三区域处刻蚀形成沟槽并在所述沟槽底部注入p型杂质形成p+保护层的步骤包括:

25、在所述pw区上铺设一层光刻胶;

26、将第三区域对应的所述光刻胶剔除,以露出所述第三区域下方的所述pw区,其中,所述第三区域位于两个所述第一区域之间;

27、在所述第三区域下方的所述pw区上刻蚀形成贯通所述pw区并延伸至所述n型漂移区的沟槽;

28、将浓度为1e18/cm3-1e19/cm3的p型杂质注入所述沟槽的槽底,形成所述p+保护层。

29、优选地,所述依次制备栅电极、源电极和漏电极,获得所述碳化硅器件的步骤包括:

30、在所述pw区上沉积栅极金属,并刻蚀外露于所述沟槽的栅极金属,形成与所述沟槽的顶部平齐的所述栅电极;

31、在所述pw区上生长形成一层imd层,其中,所述imd覆盖所述栅电极;

32、在所述imd层的第四区域处铺设一层光刻胶,并将除所述第四区域外的所述imd层刻蚀,形成隔离层,其中,所述隔离层将所述栅电极完全遮挡;

33、在所述pw区上生长金属ni形成所述源电极,其中,所述源电极覆盖所述隔离层;

34、在所述n型sic衬底上生长金属ni形成所述漏电极。

35、优选地,所述在所述pw区上沉积栅极金属,并刻蚀外露于所述沟槽的栅极金属,形成所述栅电极的步骤包括:

36、在所述pw区上沉积al或ni,形成过渡层;

37、通过干法刻蚀工艺或cmp工艺将外露于所述沟槽的所述过渡层全部刻蚀,形成所述栅电极。

38、优选地,所述过渡层的厚度为1μm~2μm,所述imd层的厚度为1μm~2μm,所述源电极的厚度为1μm~3μm,所述漏电极的厚度为1μm~3μm。

39、本发明还提供一种碳化硅器件,包括依次层叠设置的漏电极、衬底层、n型漂移区、pw区和源电极,所述pw区上开设有沟槽,所述沟槽的槽底形成一层p+保护层,所述p+保护层上设置有一层介质层,所述p+保护层上设置有栅电极,所述栅电极填满所述沟槽且所述栅电极的顶部与所述沟槽的顶部平齐,所述沟槽的槽口处设置有imd层,所述imd层覆盖所述沟槽并将所述沟槽完全遮挡,所述源电极覆盖所述imd层,所述pw区的两侧边缘形成有p+接触区,所述p+接触区贯通所述pw区并延伸至所述n型漂移区,两个所述p+接触区与所述沟槽的两侧侧壁之间分别对应形成有n+接触区。

40、在本发明的技术方案中,碳化硅器件为沟槽型碳化硅器件,沟槽型sic功率mosfet的栅槽暴露在耐压的漂移区中,在阻断情况下,沟槽拐角存在电场拥挤效应,使得栅极氧化层电场峰值远超sio2材料的临界击穿电场,更容易造成器件栅极氧化层提前击穿。因此在沟槽处设置一层p型杂质形成的p+保护层用于保护栅极介质的拐角处,同时将栅极氧化层的材质更换为al2o3、sin或铪基材料,上述材料具有更高的介电常数,可以在相同的厚度下拥有更高的临界击穿电场,使得栅极氧化层不易被击穿,减小栅极氧化层被提前击穿的概率。

技术特征:

1.一种碳化硅器件的制备方法,其特征在于,包括以下步骤:

2.如权利要求1所述的碳化硅器件的制备方法,其特征在于,所述依次层叠制备n型sic衬底、n型漂移区及pw区的步骤包括:

3.如权利要求1所述的碳化硅器件的制备方法,其特征在于,所述在pw区上的第一区域内注入n型杂质形成n+接触区的步骤包括:

4.如权利要求1所述的碳化硅器件的制备方法,其特征在于,所述在pw区上的第二区域内注入p型杂质形成p+接触区,获得中间器件的步骤包括:

5.如权利要求1所述的碳化硅器件的制备方法,其特征在于,所述将所述中间器件氧化的步骤包括:

6.如权利要求1至5中任一项所述的碳化硅器件的制备方法,其特征在于,所述在pw区上的第三区域处刻蚀形成沟槽并在所述沟槽底部注入p型杂质形成p+保护层的步骤包括:

7.如权利要求1至5中任一项所述的碳化硅器件的制备方法,其特征在于,所述依次制备栅电极、源电极和漏电极,获得所述碳化硅器件的步骤包括:

8.如权利要求7所述的碳化硅器件的制备方法,其特征在于,所述在所述pw区上沉积栅极金属,并刻蚀外露于所述沟槽的栅极金属,形成所述栅电极的步骤包括:

9.如权利要求8所述的碳化硅器件的制备方法,其特征在于,所述过渡层的厚度为1μm~2μm,所述imd层的厚度为1μm~2μm,所述源电极的厚度为1μm~3μm,所述漏电极的厚度为1μm~3μm。

10.一种碳化硅器件,其特征在于,包括依次层叠设置的漏电极、衬底层、n型漂移区、pw区和源电极,所述pw区上开设有沟槽,所述沟槽的槽底形成一层p+保护层,所述p+保护层上设置有一层介质层,所述p+保护层上设置有栅电极,所述栅电极填满所述沟槽且所述栅电极的顶部与所述沟槽的顶部平齐,所述沟槽的槽口处设置有imd层,所述imd层覆盖所述沟槽并将所述沟槽完全遮挡,所述源电极覆盖所述imd层,所述pw区的两侧边缘形成有p+接触区,所述p+接触区贯通所述pw区并延伸至所述n型漂移区,两个所述p+接触区与所述沟槽的两侧侧壁之间分别对应形成有n+接触区。

技术总结

本发明提供了一种碳化硅器件及其制备方法,其中,碳化硅器件的制备方法在碳化硅器件的制备过程中在栅极氧化层与沟槽之间制备了一层P+保护层,同时将栅极氧化层的材质更换。本发明通过在碳化硅器件沟槽处设置一层P型杂质形成的P+保护层用于保护栅极介质的拐角处,同时将栅极氧化层的材质更换为Al<subgt;2</subgt;O<subgt;3</subgt;、SiN或铪基材料,上述材料具有更高的介电常数,可以在相同的厚度下拥有更高的临界击穿电场,使得栅极氧化层不易被击穿,减小栅极氧化层被提前击穿的概率。

技术研发人员:梁帅,樊永辉,许明伟,樊晓兵

受保护的技术使用者:深圳市汇芯通信技术有限公司

技术研发日:

技术公布日:2024/1/15

- 还没有人留言评论。精彩留言会获得点赞!