半导体器件、光器件及半导体结构的制造方法与流程

本发明属于半导体,具体涉及一种半导体器件、光器件及半导体结构的制造方法。

背景技术:

1、随着摩尔定律的不断推进,半导体工艺发展到3nm节点以后,环栅型(gate allaround,gaa)晶体管被认为是鳍式场效应晶体管(finfet)的有效替代者。在gaa制造工艺工程中,高选择性比刻蚀牺牲层的水平堆叠纳米片至关重要。业界通常是通过在si和sige多层叠层中选择性地去除sige产生垂直叠层的si纳米线,进而形成n型gaa-fet。

2、然而,由于si和sige之间的晶格常数(lattice constant)之间存在较大差异,随着si层和sige层的堆叠层数不断增加,其内部应力也会不断累积,当si层和sige层的堆叠层数达到一定程度时,会导致晶圆翘曲,严重时甚至会导致晶圆破裂。此外,由于si层与sige层之间的晶格失配,会使得在sige层上外延生长的si层的位错缺陷增大,由于si层会作为gaa-fet的沟道,si层中的位错缺陷也会使得gaa-fet的性能下降。

技术实现思路

1、本发明实施例公开了一种半导体器件、光器件及半导体结构的制造方法,以解决相关技术中堆叠层数不高且易产生位错缺陷的问题。

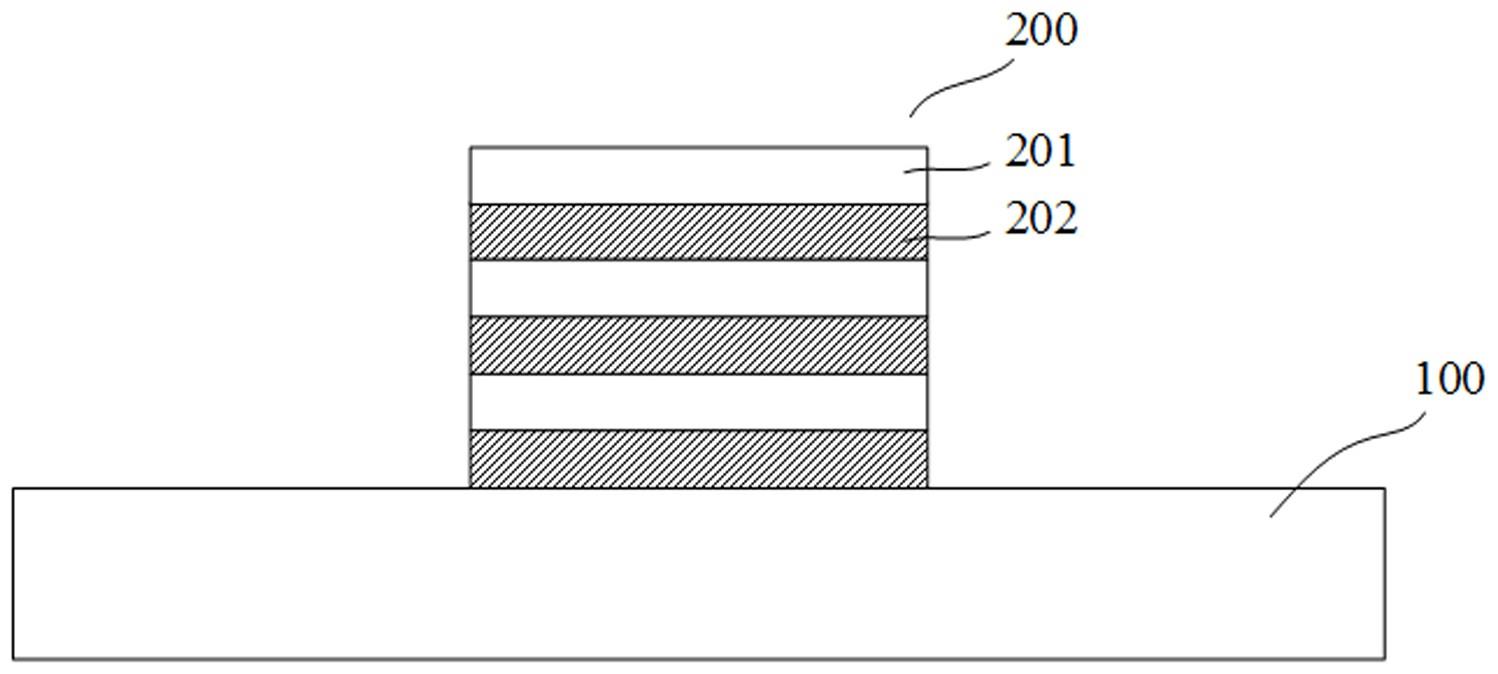

2、为了解决上述技术问题,根据第一方面,本发明实施例公开了一种半导体结构的制造方法,包括:在衬底上形成叠层结构,所述叠层结构包括交替堆叠的功能层和牺牲层,所述功能层和所述牺牲层由相同材料构成,所述牺牲层掺杂有n型或p型杂质,且所述牺牲层的掺杂浓度大于所述功能层;从所述叠层结构中选择性地去除所述牺牲层。

3、在一些可选实施方式中,所述功能层和所述牺牲层为多个,所述功能层中的至少一个的至少部分为弯曲状或弯折状;和/或所述牺牲层中的至少一个的至少部分为弯曲状或弯折状。

4、在一些可选实施方式中,所述衬底为平面,所述叠层结构形成在所述平面上;或者所述衬底包括波浪状表面,所述叠层结构适应性地形成在所述波浪状表面上;或者所述衬底包括从衬底本体表面凸起的凸起结构,所述叠层结构适应性地形成在所述衬底本体和所述凸起结构的表面上。

5、在一些可选实施方式中,所述凸起结构包括:第一凸起部,位于所述衬底本体上;第二凸起部,位于所述第一凸起部上,所述第二凸起部在所述衬底本体所处平面上的投影面积大于所述第一凸起部在所述衬底本体所处平面上的投影面积,且所述第一凸起部在所述衬底本体所处平面上的投影位于所述第二凸起部在所述衬底本体所处平面上的投影内。

6、在一些可选实施方式中,从所述叠层结构中选择性地去除所述牺牲层,包括:对所述叠层结构进行各向异性刻蚀,保留所述第二凸起部正下方的所述叠层结构;从所保留的所述叠层结构中选择性地去除所述牺牲层。

7、在一些可选实施方式中,所述功能层为非掺杂层;或者所述功能层的掺杂浓度小于5×1014cm-3;或者所述牺牲层的掺杂浓度大于5×1014cm-3;或者所述牺牲层的掺杂浓度为6×1014cm-3至5×1021cm-3。

8、在一些可选实施方式中,所述在衬底上形成叠层结构,包括:利用化学气相沉积工艺,在所述衬底上交替外延生长所述功能层和所述牺牲层。

9、在一些可选实施方式中,所述功能层和所述牺牲层的材料为硅;所述外延生长所述功能层的步骤包括:向工艺腔室内通入含硅气体;所述外延生长所述牺牲层的步骤包括:向所述工艺腔室内通入所述含硅气体和含杂质元素的气体。

10、在一些可选实施方式中,所述含硅气体包括sih4、si2h6、sih2cl2中的至少一个;所述含杂质元素的气体包括b2h6,或者所述含杂质元素的气体包括ph3、ash3、sbh3、bih3中的至少一个。

11、在一些可选实施方式中,所述外延生长的温度为400至750℃。

12、在一些可选实施方式中,所述从所述叠层结构中选择性地去除所述牺牲层,包括:利用工艺气体对所述叠层结构进行各向同性等离子体刻蚀。

13、在一些可选实施方式中,所述功能层和所述牺牲层的材料为硅;所述工艺气体包括含氯气体、含溴气体中的至少一个。

14、在一些可选实施方式中,所述含氯气体包括cl2、hcl中的至少一个;所述含溴气体包括br2、hbr中的至少一个;所述工艺气体还包括n2、he、ar中的至少一个。

15、在一些可选实施方式中,在从所述叠层结构中选择性地去除所述牺牲层之后,还包括:对所述功能层进行氧化处理;去除所述功能层表面的氧化层。

16、根据第二方面,本发明实施例公开了一种半导体器件,包括:衬底;至少一个功能层,设置在所述衬底上,至少一个所述功能层在竖直方向上间隔设置,所述功能层中的至少一个的至少部分为弯曲状或弯折状;栅极结构,围绕各个所述功能层设置;源/漏区,分别设置在所述功能层的两侧,且与所述功能层连接。

17、根据第三方面,本发明实施例公开了一种半导体器件,包括:衬底;至少一个功能层,设置在所述衬底上,至少一个所述功能层在竖直方向上间隔设置,所述功能层由上述第一方面中任一项所述的半导体结构的制造方法得到;栅极结构,围绕各个所述功能层设置;源/漏区,分别设置在所述功能层的两侧,且与所述功能层连接。

18、根据第四方面,本发明实施例公开了一种光器件,包括:至少一个功能层,用于传输光信号,所述功能层由上述第一方面中任一项所述的半导体结构的制造方法得到。

19、在本发明实施例的半导体器件、光器件及半导体结构的制造方法中,功能层和牺牲层由相同材料构成,仅掺杂浓度存在差异,功能层和牺牲层的晶格常数几乎不存在差异,功能层和牺牲层的界面处不会出现因晶格失配而导致应力,也不会在功能层中引入位错缺陷;并且,与采用渐变牺牲层的相关技术相比,本发明实施例的牺牲层的厚度可以做的很薄,且制造工艺简单、堆叠层数高且产能大,本发明实施例的叠层结构的堆叠层数可达上百层,不会出现晶圆翘曲甚至破裂的现象。

技术特征:

1.一种半导体结构的制造方法,其特征在于,包括:

2.根据权利要求1所述的制造方法,其特征在于,所述功能层和所述牺牲层为多个,所述功能层中的至少一个的至少部分为弯曲状或弯折状;和/或

3.根据权利要求1所述的制造方法,其特征在于,所述衬底为平面,所述叠层结构形成在所述平面上;或者

4.根据权利要求3所述的制造方法,其特征在于,所述凸起结构包括:

5.根据权利要求4所述的制造方法,其特征在于,从所述叠层结构中选择性地去除所述牺牲层,包括:

6.根据权利要求1所述的制造方法,其特征在于,所述功能层为非掺杂层;或者所述功能层的掺杂浓度小于5×1014cm-3;或者

7.根据权利要求1至6中任一项所述的制造方法,其特征在于,所述在衬底上形成叠层结构,包括:

8.根据权利要求7所述的制造方法,其特征在于,所述功能层和所述牺牲层的材料为硅;

9.根据权利要求8所述的制造方法,其特征在于,所述含硅气体包括sih4、si2h6、sih2cl2中的至少一个;

10.根据权利要求7所述的制造方法,其特征在于,所述外延生长的温度为400至750℃。

11.根据权利要求1至6中任一项所述的制造方法,其特征在于,所述从所述叠层结构中选择性地去除所述牺牲层,包括:

12.根据权利要求11所述的制造方法,其特征在于,所述功能层和所述牺牲层的材料为硅;

13.根据权利要求12所述的制造方法,其特征在于,所述含氯气体包括cl2、hcl中的至少一个;

14.根据权利要求1至6中任一项所述的制造方法,其特征在于,在从所述叠层结构中选择性地去除所述牺牲层之后,还包括:

15.一种半导体器件,其特征在于,包括:

16.一种半导体器件,其特征在于,包括:

17.一种光器件,其特征在于,包括:

技术总结

本发明实施例公开一种半导体器件、光器件及半导体结构的制造方法,其中所述制造方法包括:在衬底上形成叠层结构,所述叠层结构包括交替堆叠的功能层和牺牲层,所述功能层和所述牺牲层由相同材料构成,所述牺牲层掺杂有n型或p型杂质,且所述牺牲层的掺杂浓度大于所述功能层;从所述叠层结构中选择性地去除所述牺牲层。

技术研发人员:赵晋荣,李佳阳,杨光,董博宇,袁福顺,赵万辉

受保护的技术使用者:北京北方华创微电子装备有限公司

技术研发日:

技术公布日:2024/1/15

- 还没有人留言评论。精彩留言会获得点赞!