一种半导体测试结构、测试方法及系统与流程

本申请涉及半导体集成电路制造,具体涉及一种半导体测试结构、测试方法及系统。

背景技术:

1、随着集成电路的发展,半导体器件制造趋于越来越小的尺寸,密度也会越来越大,这就要求电路中用于电路元件和电容存储器件隔离的区域会越来越小。如今业内普遍采用浅沟槽隔离(shallow trench isolation,sti)结构来完成器件之间的隔离。

2、随着半导体器件尺寸的微缩,对sti隔离的能力要求越来越高,边沟(divot,也称凹陷区)缺陷也越来越容易出现,而且边沟缺陷是当前集成电路制造中比较常见的一种缺陷,而且该类边沟缺陷容易导致局部沟道提前导通,甚至会造成栅极和栅极之间桥连(bridge)。

3、在当前集成电路制造工艺中,只能通过工艺处理来尽可能地降低边沟缺陷的出现可能,但并不能避免边沟缺陷的出现,而且随着器件尺寸向更小尺寸发展,边沟缺陷只会更加突出。目前,因缺乏边沟缺陷的测试手段,导致边沟缺陷出现后无法及时被检测出来,造成边沟缺陷隐藏于集成电路中,因而边沟缺陷仍然是造成集成电路失效的一大诱因。

技术实现思路

1、有鉴于此,本说明书实施例提供一种半导体测试结构、测试方法及系统,通过在可能出现边沟缺陷的区域设置测试结构,从而通过该测试结构能够及时检测出是否存在边沟缺陷。

2、本说明书实施例提供以下技术方案:

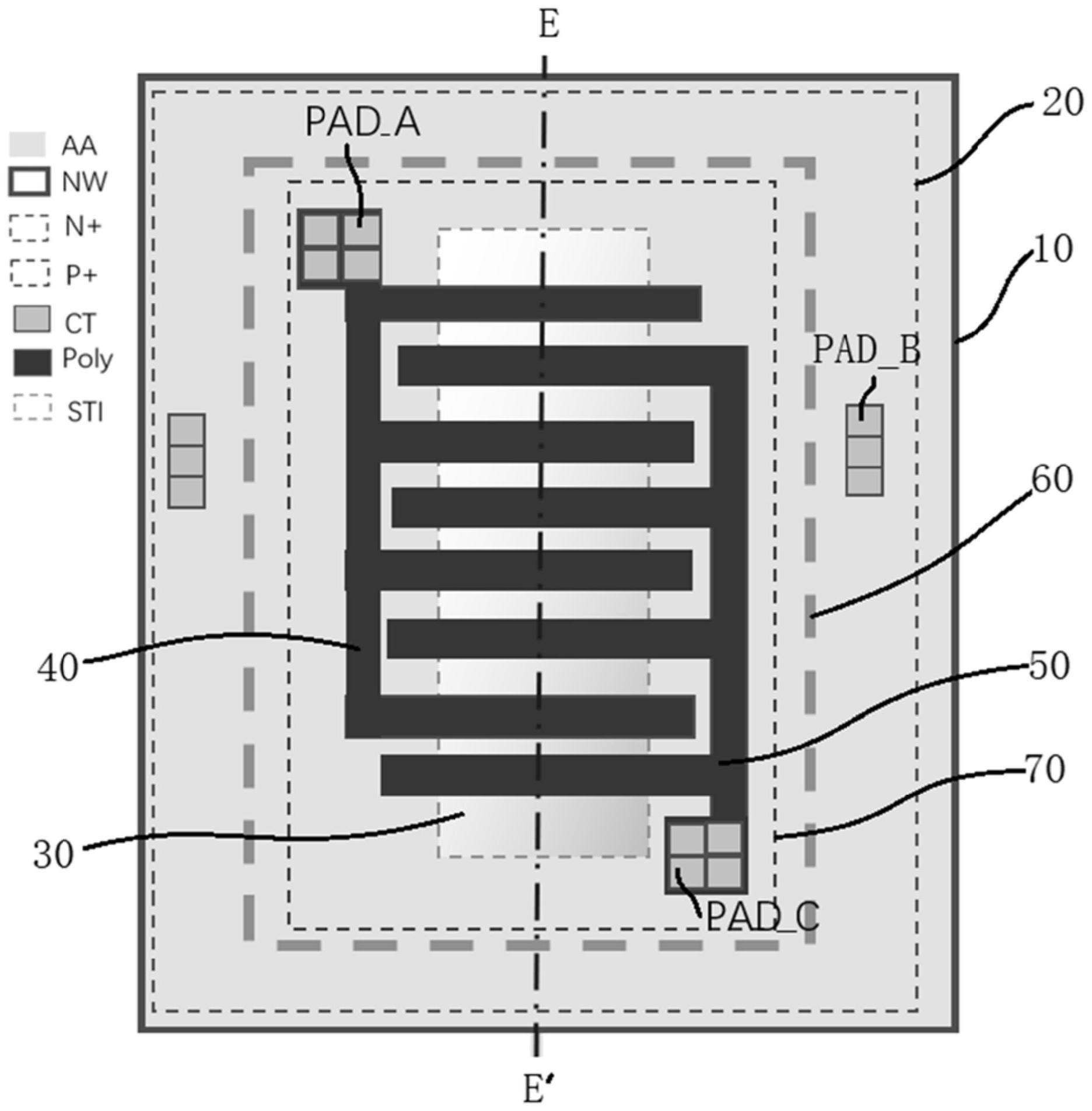

3、本说明书实施例提供一种半导体测试结构,包括:

4、第一金属衬垫形成的第一测试引脚,其中第一金属衬垫设置于n型重掺区域上,作为外接于n型重掺区域的测试接口;

5、第一多晶硅栅结构和第二多晶硅栅结构,其中第一多晶硅栅结构与第二多晶硅栅结构之间交叉且不相连;

6、第二金属衬垫形成的第二测试引脚,其中第二金属衬垫设置于第一多晶硅栅结构的一端,作为外接于第一多晶硅栅结构的测试接口;

7、第三金属衬垫形成的第三测试引脚,其中第三金属衬垫设置于第二多晶硅栅结构的一端,作为外接于第二多晶硅栅结构的测试接口;

8、其中,第一多晶硅栅结构和第二多晶硅栅结构设置于待检测的第一浅沟槽隔离结构上方,以使所述待检测的第一浅沟槽隔离结构的表面分别与第一多晶硅栅结构和第二多晶硅栅结构相交出若干处接触结构。

9、优选地,所述半导体测试结构还包括第二浅沟槽隔离结构,所述第二浅沟槽隔离结构设置于所述n型重掺区域,且包围在第一多晶硅栅结构和第二多晶硅栅结构所在区域的外面。

10、优选地,第一金属衬垫位于第二浅沟槽隔离结构外的n型重掺区域上;

11、和/或,第二浅沟槽隔离结构为环形结构。

12、优选地,在本申请中任意一项实施例中,第一多晶硅栅结构和第二多晶硅栅结构均为梳状结构,第一多晶硅栅结构与第二多晶硅栅结构构成交叉梳状结构,第二金属衬垫设置于第一多晶硅栅结构的梳掌端,第三金属衬垫设置于第二多晶硅栅结构的梳掌端。

13、优选地,第一金属衬垫位于所述交叉梳状结构的中部外侧。

14、本说明书实施例还提供一种半导体测试方法,包括:

15、将测试结构中的第一测试引脚接地,所述测试结构为如本申请中任一项实施例所述的半导体测试结构;

16、通过所述测试结构中的第二测试引脚到第三测试引脚之间的第一测试回路,获取所述第一测试回路对应的第一测试数据,其中所述第一测试数据包括以下至少一项数据:击穿电压,漏电流,电容值,电阻值;

17、根据所述第一测试数据,确定所述待检测的第一浅沟槽隔离结构是否存在边沟缺陷。

18、优选地,在获取第一测试数据前,所述半导体测试方法还包括:

19、通过所述第二测试引脚和/或所述第三测试引脚到所述第一测试引脚之间的第二测试回路,获取所述第二测试回路对应的第二测试数据,其中所述第二测试数据包括以下至少一项数据:击穿电压,漏电流,电容值,电阻值;

20、根据所述第二测试数据确定待检测的第一浅沟槽隔离结构所在的栅极结构与衬底之间的隔离性能是否满足预设要求,若是则继续获取所述第一测试数据,若否则结束测试。

21、优选地,在本申请中任意一项实施例中,在确定出所述第一浅沟槽隔离结构存在边沟缺陷时,所述半导体测试方法还包括:将所述第一测试数据与预设数据的百分比阈值进行判断,以确定所述边沟缺陷对应的缺陷等级,所述预设数据为无边沟缺陷对应的经验数据。

22、本说明书实施例还提供一种半导体测试系统,包括:

23、测试结构,其中所述测试结构为如本申请中任一项实施例所述的半导体测试结构;

24、测试设备,其中所述测试设备为用于获取测试数据的设备,所述测试数据包括以下至少一项数据:击穿电压,漏电流,电容值,电阻值;

25、其中,所述测试设备的接地端与所述测试结构的第一测试引脚连接,以及所述测试设备的测试端对应地与所述测试结构中的第二测试引脚和第三测试引脚连接,以获取所述第二测试引脚到所述第三测试引脚之间的第一测试回路对应的所述测试数据;或者,所述测试设备的接地端与所述测试结构的第一测试引脚连接,以及所述测试设备的测试端对应地与所述测试结构中的第二测试引脚和/或所述第三测试引脚连接,以获取所述第二测试引脚/或所述第三测试引脚到所述第一测试引脚之间的第二测试回路对应的所述测试数据。

26、优选地,所述半导体测试系统还包括数据处理设备,所述数据处理设备用于对所述测试数据进行判断处理。

27、与现有技术相比,本说明书实施例采用的上述至少一个技术方案能够达到的有益效果至少包括:

28、通过在待测试的sti上设置多晶硅栅结构,使得sti的边缘能够与多晶硅栅(poly)相交形成多个重复结构,从而通过对多晶硅结构的测试,能够非常容易地测试出sit是否存在边沟缺陷,因此本申请能够为边沟缺陷检测提供了一种非常有效的测试手段,有助于及时发现sti中的边沟缺陷,防止边沟缺陷隐藏在集成电路中,有效地最终避免了集成电路因边沟缺陷发生失效的可能性。

技术特征:

1.一种半导体测试结构,其特征在于,包括:

2.根据权利要求1所述的半导体测试结构,其特征在于,所述半导体测试结构还包括第二浅沟槽隔离结构,所述第二浅沟槽隔离结构设置于所述n型重掺区域,且包围在第一多晶硅栅结构和第二多晶硅栅结构所在区域的外面。

3.根据权利要求2所述的半导体测试结构,其特征在于,第一金属衬垫位于第二浅沟槽隔离结构外的n型重掺区域上;

4.根据权利要求1-3中任意一项所述的半导体测试结构,其特征在于,第一多晶硅栅结构和第二多晶硅栅结构均为梳状结构,第一多晶硅栅结构与第二多晶硅栅结构构成交叉梳状结构,第二金属衬垫设置于第一多晶硅栅结构的梳掌端,第三金属衬垫设置于第二多晶硅栅结构的梳掌端。

5.根据权利要求4所述的半导体测试结构,其特征在于,第一金属衬垫位于所述交叉梳状结构的中部外侧。

6.一种半导体测试方法,其特征在于,包括:

7.根据权利要求6所述的半导体测试方法,其特征在于,在获取第一测试数据前,所述半导体测试方法还包括:

8.根据权利要求6-7中任意一项所述的半导体测试方法,其特征在于,在确定出所述第一浅沟槽隔离结构存在边沟缺陷时,所述半导体测试方法还包括:将所述第一测试数据与预设数据的百分比阈值进行判断,以确定所述边沟缺陷对应的缺陷等级,所述预设数据为无边沟缺陷对应的经验数据。

9.一种半导体测试系统,其特征在于,包括:

10.根据权利要求9所述的半导体测试系统,其特征在于,所述半导体测试系统还包括数据处理设备,所述数据处理设备用于对所述测试数据进行判断处理。

技术总结

本申请提供一种半导体测试结构、测试方法及系统,应用于半导体集成电路制造技术领域,其中测试结构包括:第一金属衬垫形成的第一测试引脚;第一多晶硅栅结构和第二多晶硅栅结构,其中第二金属衬垫设置于第一多晶硅栅结构的一端形成的第二测试引脚,第三金属衬垫设置于第二多晶硅栅结构的一端形成的第三测试引脚。因此,第一多晶硅栅结构和第二多晶硅栅结构设置于待检测的第一浅沟槽隔离结构上方,从而第一浅沟槽隔离结构的表面分别与第一多晶硅栅结构和第二多晶硅栅结构相交出若干处接触结构,进而通过第一测试引脚、第二测试引脚和第三测试引脚能够快速准确地检测出是否存在边沟缺陷。

技术研发人员:叶亮,常建光

受保护的技术使用者:上海积塔半导体有限公司

技术研发日:

技术公布日:2024/1/16

- 还没有人留言评论。精彩留言会获得点赞!