一种提升碳化硅器件短路耐量的原胞设计及其制备方法与流程

本发明涉及半导体,尤其涉及一种提升碳化硅器件短路耐量的原胞设计及其制备方法。

背景技术:

1、sic材料由于具有宽禁带、高导热效率、耐高温、耐辐射等优点常被用在功率系统中,例如新能源汽车、光伏发电、高铁、城市轨道交通中。sic mosfet器件作为电力系统中的开关,更是被广泛应用在各种电力电子系统中。

2、在电力电子应用系统中,功率器件可能会处在极端的工作条件下,这种工作条件会使得器件承受极高的电流或电场。例如在桥式电路中,上桥臂或者下桥臂本应处于关断状态,但是由于某些原因导致处于关断状态的晶体管误开通,那么母线电压会直接加载在导通的器件中,此时器件经受极高的短路电流和功率。如果此时处于短路状态的功率器件在电路反应时间之前已经被损坏掉,那么电力电子系统就不能正常的工作甚至可能会出现安全隐患,因此怎样提升功率器件的短路耐受时间是功率器件设计的关键。

技术实现思路

1、本发明针对以上问题,提供了一种增大了器件的jfet区域电阻、减小了器件短路电流和短路功率,增大了器件的短路耐受时间的一种提升碳化硅器件短路耐量的原胞设计及其制备方法。

2、本发明的技术方案是:

3、一种碳化硅功率场效应晶体管制备方法,包括以下步骤:

4、s100、在n型外延衬底上生长一层n型外延层,作为器件的漂移区;

5、s200、在n型外延层上淀积二氧化硅sio2和多晶硅polysi,通过刻蚀工艺刻掉不需要的sio2和polysi,剩下的作为硬掩模;然后进行pwell离子注入工艺,形成pwell体区;

6、s300、祛掉步骤s200中残留在晶圆表面的sio2,通过淀积刻蚀等工艺形成sio2硬掩模层;然后进行pwell离子注入工艺,形成阶梯型pwell体区;

7、s400、在晶圆表面形成nn区和pp区;

8、s500、生长sio2作为栅氧层,并进行表面钝化处理;

9、s600、在晶圆正面上淀积一层polysi,再对polysi注入磷离子进行饱和掺杂,并刻蚀掉多余的polysi;

10、s700、在晶圆正面形成肖特基接触和欧姆接触、背面形成欧姆接触。

11、具体的,步骤s200中,pwell体区的深度为1.2um。

12、具体的,步骤s400中,依次包括以下步骤:

13、s410、在晶圆表面淀积一层sio2,再刻蚀sio2形成侧墙spacer,光刻胶和spacer作为硬掩模离子注入氮离子形成nn区;

14、s420、然后去掉表面上的光刻胶、sio2、polysi,再通过光刻、显影、离子注入铝元素形成pp区;

15、s430、再在晶圆表面上溅射一层碳膜,在高温下1800°c进行退火处理,激活所有注入的离子;

16、具体的,步骤s500中,依次包括以下步骤:

17、s510、去掉晶圆表面上的碳膜湿氧,生长30nm的sio2再去掉表面的sio2用来改善晶圆表面的粗糙度;

18、s520、再1300°c高温下干氧生长50nm的sio2作为栅氧;

19、s530、生长完栅氧后降温到1200°c通入一氧化氮no和氮气n2进行表面钝化。

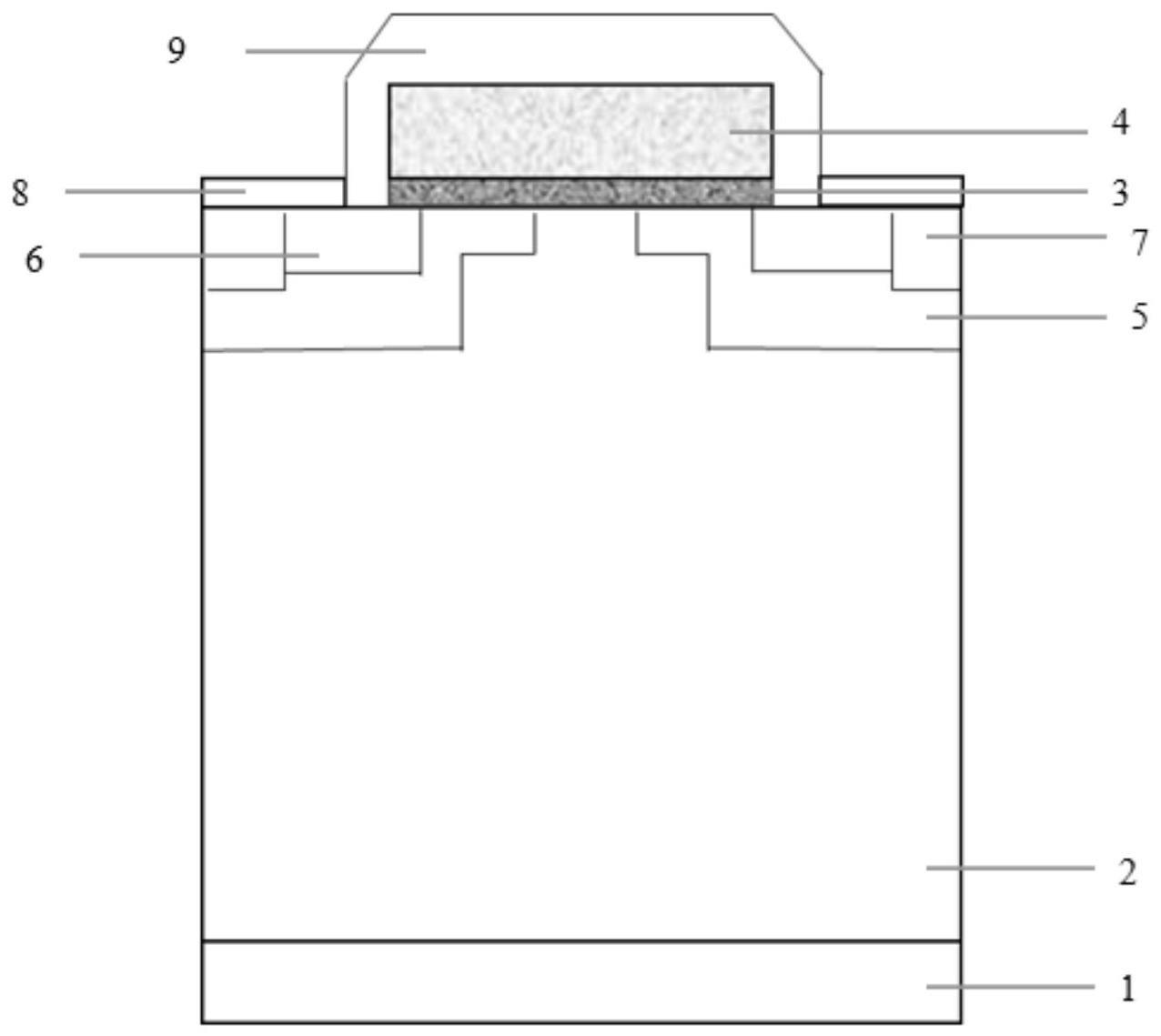

20、一种碳化硅功率场效应晶体管,包括从下而上依次连接的n型外延衬底、n型外延层、栅氧层和polysi层;

21、所述n型外延层的顶面的端部设有向下延伸的pp区;

22、所述pp区的内侧设有从n型外延层的顶面向下延伸的nn区;

23、所述nn区的内侧设有从n型外延层的顶面向下,并依次经过所述nn区和pp区伸至端部的阶梯型pwell体区;

24、所述栅氧层和polysi层的外侧设有包裹的层间介质;

25、所述nn区和pp区的顶部设有与层间介质连接的欧姆接触。

26、具体的,所述阶梯型pwell体区的中部设有间隔,使所述n型外延层的截面呈凸型结构。

27、本发明有益效果:

28、通过pwell体区形貌设置成阶梯型,这种阶梯型的pwell形貌,增大了器件的jfet区域电阻从而减小了器件的短路电流和短路功率,增大了器件的短路耐受时间。由于短路电流的减小,从而也减小了短路工况对器件的损伤增大了器件长期可靠性。

技术特征:

1.一种提升碳化硅器件短路耐量的原胞设计的制备方法,其特征在于,包括以下步骤:

2.根据权利要求1所述的一种提升碳化硅器件短路耐量的原胞设计的制备方法,其特征在于,步骤s200中,pwell体区的深度为1.2um。

3.根据权利要求1所述的一种提升碳化硅器件短路耐量的原胞设计的制备方法,其特征在于,步骤s400中,依次包括以下步骤:

4.根据权利要求1所述的一种提升碳化硅器件短路耐量的原胞设计的制备方法,其特征在于,步骤s500中,依次包括以下步骤:

5.一种如权利要求1所述一种提升碳化硅器件短路耐量的原胞设计的制备方法制备的提升碳化硅器件短路耐量的原胞设计,其特征在于,包括从下而上依次连接的n型外延衬底(1)、n型外延层(2)、栅氧层(3)和polysi层(4);

6.根据权利要求1所述的一种提升碳化硅器件短路耐量的原胞设计,其特征在于,所述阶梯型pwell体区(5)的中部设有间隔,使所述n型外延层(2)的截面呈凸型结构。

技术总结

一种提升碳化硅器件短路耐量的原胞设计及其制备方法,涉及半导体技术领域。本发明通过PWELL体区形貌设置成阶梯型,这种阶梯型的PWELL形貌,增大了器件的JFET区域电阻从而减小了器件的短路电流和短路功率,增大了器件的短路耐受时间。由于短路电流的减小,从而也减小了短路工况对器件的损伤增大了器件长期可靠性。

技术研发人员:张陈龙,杨程,王嘉良,王毅

受保护的技术使用者:扬州扬杰电子科技股份有限公司

技术研发日:

技术公布日:2024/1/16

- 还没有人留言评论。精彩留言会获得点赞!