具有密封层的半导体封装或器件的制作方法

本公开涉及半导体结构,半导体结构可以存在于半导体器件内,包括用于保护导电层的密封层。

背景技术:

1、通常,半导体器件包括导电层。例如,在一些半导体器件中,可以将半导体器件的顶部导电层(例如,顶部金属化层)以适当的方式连接到半导体封装,以保证封装引脚与半导体器件之间的输入/输出(i/o)电信号连续性。这些连接可以通过顶部金属钝化开口在顶部导电层与半导体封装之间实现,该顶部金属钝化开口可以称为pad。pad可以被加工成包含并且包括由专用金属化工艺形成的导电结构,该专用金属化工艺可以称为焊盘金属化(opm)工艺。在半导体器件的半导体制造过程的完成之后并且在半导体器件的封装之前,半导体器件的在其处存在顶部导电层和导电结构的pad可能在诸如电气测试、电晶圆分选(ews)、晶圆运送到组装fab(实现器件封装的晶圆厂)和其他相似或类似类型的过程的若干操作期间在受控环境中保持不受保护。在这些过程中,由于pad保持暴露,在pad处的顶部导电层和导电结构可能被环境污染的存在所腐蚀,环境污染诸如湿气(例如,液滴、湿度等)或污染物(例如,污染物颗粒等),其可能腐蚀在pad处的顶部导电层和导电结构。当在pad处的顶部导电层和/或导电结构暴露于这些环境污染物时,在pad处的顶部导电层和/或导电结构可能比预期更快地腐蚀,从而由于半导体封装或器件可能比预期更早发生故障而导致半导体封装或器件的使用寿命减少。

2、在半导体器件或封装中,导电结构(例如,可以利用opm工艺形成的接触焊盘或结构)可以耦合到在半导体器件或封装中使用的顶部导电层(诸如再分配层(rdl))或耦合到引线键合部(例如,球和棍等)。然而,利用opm工艺在pad处(例如,在顶部金属钝化开口中)形成导电结构可能导致在导电结构与钝化层之间形成开放通道(例如,缝隙),该开放通道可能允许环境污染物更容易腐蚀导电结构和/或顶部导电层。例如,这种开放通道可能由于在可以通过opm工艺形成的导电结构和与导电结构相邻的钝化层之间的不良粘附而形成。在形成导电结构的opm工艺期间的热膨胀和本征应力可能导致形成开放通路(例如,缝隙)。

技术实现思路

1、本公开涉及可以在制造具有顶部导电层(例如,第一金属化层或顶部金属化层)的半导体器件中利用的结构和密封层的至少一些实施例。顶部导电层可以是铜(cu)层或铝(al)层,其可以由在顶部导电层的表面上形成的焊盘金属化(opm)形成的导电结构来保护。本公开涉及在制造半导体器件时在半导体器件的导电结构与其他各个层之间形成密封层,以降低在顶部导电层和导电结构中腐蚀的可能性。

2、本公开涉及可以在半导体封装或器件内利用的结构的至少一些实施例,包括根据本公开的实施例的导电结构和密封层。这些结构具有由于外部环境中存在的湿气和污染物而被腐蚀的降低的可能性。例如,密封层可以阻挡或防止环境污染物到达与开放通道(例如,缝隙)相邻的导电层,环境污染物可以通过该开放通道容易地进入。这些环境污染物可以包括湿气(如液滴、湿度等)或者可以是外部环境内的其他污染物(例如,污染颗粒)。开放通路(例如,缝隙)可能由于在可以通过opm工艺形成的导电结构和与导电结构相邻的钝化层之间的不良粘附而形成。在形成导电结构的opm工艺期间的热膨胀和本征应力可能导致形成开放通路(例如,缝隙)。密封层通过防止环境污染物到达导电层,以降低导电层早期腐蚀的可能性。

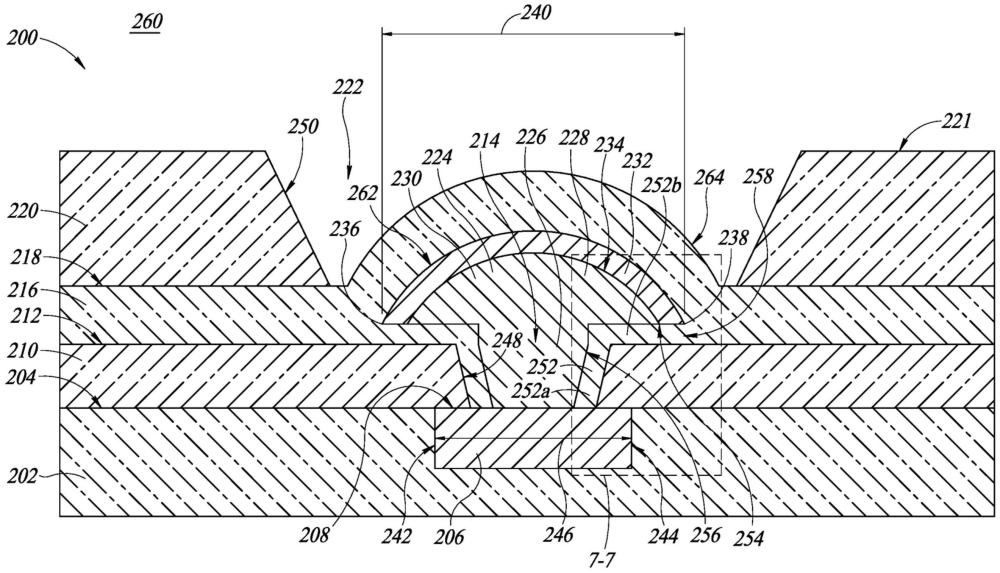

3、在一些实施例中,衬底包括第一表面,在第一表面处暴露衬底内的导电层。导电层可以是衬底内的导电大马士革层。导电层包括从衬底的第一表面暴露的第二表面。第一绝缘层在衬底的第一表面上,并且具有横向于衬底的第一表面和横向于导电层的第二表面的第一侧壁。第一开口在第一绝缘层中并且通过第一绝缘层延伸至导电层的第二表面,使得第一开口从第一绝缘层暴露导电层的第二表面。导电结构存在于第一开口内并且耦合到导电层的第二表面。第一绝缘层还包括与第一开口相邻的第一侧壁,并且导电结构包括第二侧壁,第二侧壁面向第一侧壁并且与第一绝缘层的第一侧壁间隔开。缝隙在第一绝缘层的第一侧壁与导电结构的第二侧壁之间。缝隙沿着第一绝缘层的第一侧壁和导电结构的第二侧壁延伸至导电层的第二表面。密封层在缝隙内并且在导电结构的第二表面上,以密封导电结构的第二表面以免受缝隙外部的环境影响。

4、密封层用作屏障以阻止湿气和污染物到达导电层的第二表面。例如,虽然湿气和污染物可以容易地进入缝隙并且穿过缝隙到达密封层,但是由于密封层阻止并且阻挡湿气和污染物,因此湿气和污染物不能到达导电层的第二表面。这至少降低导电层在与缝隙的流体连通中被来自外部环境的湿气和污染物腐蚀或损坏的可能性。降低这种腐蚀或损坏的可能性通常获得利用半导体制造厂(fab)在公差内制造的可用半导体封装的产量的增加。

技术特征:

1.一种器件,包括:

2.根据权利要求1所述的器件,其中所述密封层完全填充所述缝隙。

3.根据权利要求1所述的器件,其中所述密封层部分填充所述缝隙。

4.根据权利要求1所述的器件,其中所述导电结构还包括:

5.根据权利要求4所述的器件,其中所述密封层位于所述导电结构的所述第三表面上。

6.根据权利要求5所述的器件,其中所述密封层完全覆盖所述导电结构的所述第三表面。

7.根据权利要求5所述的器件,其中第二开口穿过所述密封层延伸至所述导电结构的所述第三表面,所述开口从所述密封层暴露所述第三表面。

8.根据权利要求4所述的器件,其中:

9.根据权利要求1所述的器件,还包括位于所述第一绝缘层上的第二绝缘层,并且其中所述密封层位于所述第二绝缘层上。

10.根据权利要求1所述的器件,其中:

11.根据权利要求10所述的器件,还包括位于所述绝缘层的所述第四表面上的第二绝缘层。

12.根据权利要求11所述的器件,其中所述密封层位于所述第一绝缘层与所述第二绝缘层之间。

13.根据权利要求11所述的器件,其中所述密封层将所述第一绝缘层与所述第二绝缘层完全分离。

14.一种器件,包括:

15.根据权利要求14所述的器件,还包括位于所述绝缘层与所述导电结构之间的缝隙,所述缝隙延伸至所述第一导电层的所述表面上的所述密封层,并且其中所述密封层将所述第一导电层的所述表面与所述缝隙完全分离。

16.根据权利要求14所述的器件,还包括引线键合部,所述引线键合部被耦合到所述导电结构,并且其中第二导电结构包括与所述第一端部相对的第二端部,所述导电结构的所述第二端部被耦合到所述引线键合部。

17.根据权利要求14所述的器件,还包括第二导电层,所述第二导电层被耦合到所述导电结构,并且其中所述第二导电结构包括与所述第一端部相对的第二端部,所述第二导电结构被耦合到所述第二导电层。

18.一种方法,包括:

19.根据权利要求18所述的方法,其中所述密封层通过原子层沉积技术而被形成。

20.根据权利要求18所述的方法,其中形成所述密封层还包括:在所述第一绝缘层的所述第一侧壁上、并且在所述导电结构的所述第二侧壁上形成所述密封层。

技术总结

本公开的实施例涉及具有密封层的半导体封装或器件。本公开涉及导电层上的导电结构的实施例,该导电层可以是半导体器件或封装的导电大马士革层。导电大马士革层可以在半导体器件或封装的衬底内。在导电结构的一个或多个侧壁与衬底上的一个或多个绝缘层的一个或多个侧壁之间存在缝隙,并且缝隙延伸到导电层的表面。在缝隙中形成密封层,该密封层密封导电层以免受半导体器件或封装外部的可能进入缝隙的湿气和污染物影响。换句话说,密封层阻止湿气和污染物到达导电层,使得导电层不会由于暴露于湿气和污染物而腐蚀。

技术研发人员:F·米拉内西,P·科尔帕尼

受保护的技术使用者:意法半导体股份有限公司

技术研发日:

技术公布日:2024/3/12

- 还没有人留言评论。精彩留言会获得点赞!