半导体装置及半导体装置的制造方法与流程

本发明说明书所公开的技术涉及半导体技术。

背景技术:

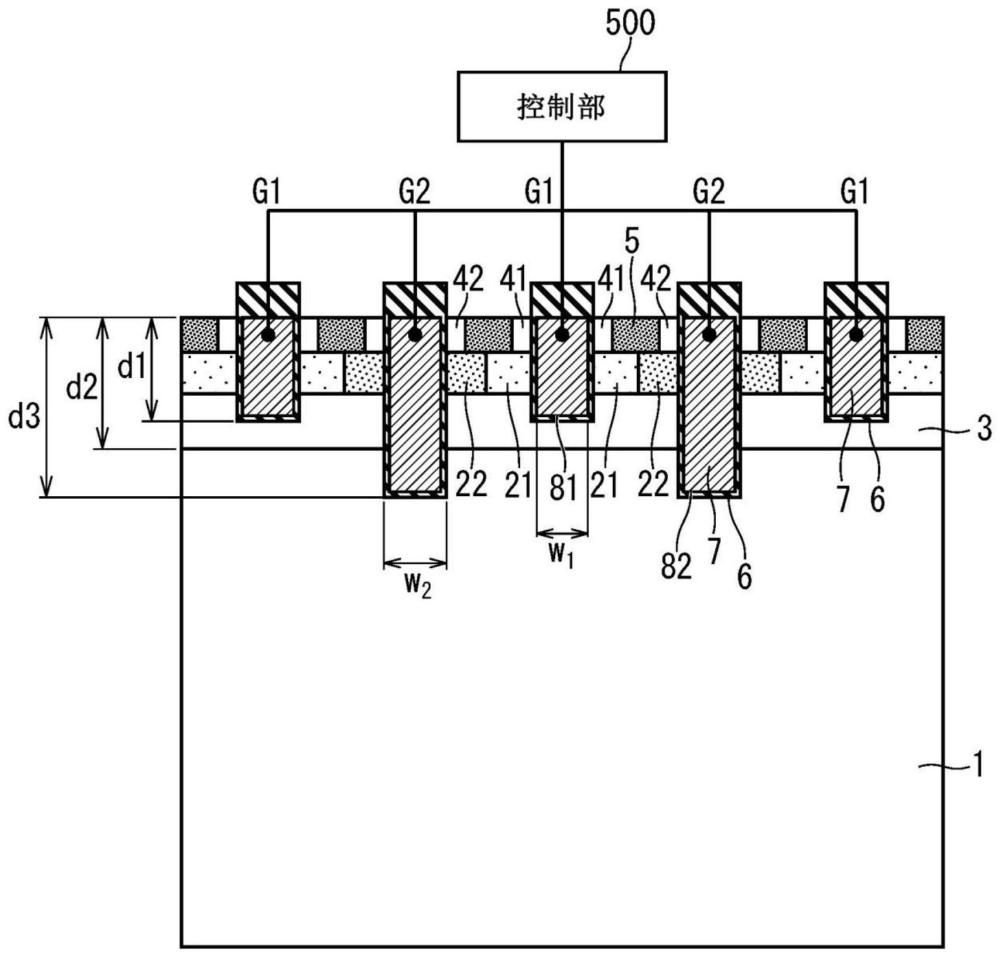

1、例如专利文献1所示那样的半导体装置,具体而言,绝缘栅型双极晶体管(insulated gate bipolar transistor,即,igbt)在n-型半导体的基板的上表面具有周期性地形成的沟槽构造(具体而言,浅的栅极沟槽)。在该栅极沟槽的侧面及底面形成氧化膜层,并且以被氧化膜层包围的方式设置埋入层,该埋入层例如为多晶硅。该栅极沟槽内的埋入层与栅极电极连接。

2、另外,上述igbt具有与上述栅极沟槽相邻,并且周期性地形成于基板的上表面的其它沟槽构造(具体而言,深的栅极沟槽)。在该栅极沟槽的侧面及底面形成氧化膜层,并且以被氧化膜层包围的方式设置埋入层。另外,该栅极沟槽内的埋入层与其它栅极电极连接。

3、另外,上述igbt具有在与栅极沟槽的相反侧与其它栅极沟槽相邻,并且形成于基板的上表面的大于或等于1个沟槽构造(具体而言,深的哑沟槽)。在哑沟槽的侧面及底面形成氧化膜层,并且以被氧化膜层包围的方式设置埋入层。哑沟槽内的埋入层与发射极电极连接。

4、另一方面,在栅极沟槽与其它栅极沟槽之间的基板的表层形成n型层。另外,在n型层的表层形成p型层。并且,在p型层的表层选择性地形成n+型发射极层和p+型发射极层。

5、n型层与基板、栅极沟槽的氧化膜层、其它栅极沟槽的氧化膜层接触。

6、p型层与p+型发射极层、n型层、栅极沟槽的氧化膜层、其它栅极沟槽的氧化膜层接触。

7、n+型发射极层与p型层、栅极沟槽的氧化膜层、其它栅极沟槽的氧化膜层接触。

8、专利文献1:日本特开2019-186318号公报

9、在上述那样的igbt进行接通动作时,栅极电极与其它栅极电极同时变为接通,电子从栅极沟槽和其它栅极沟槽注入至基板。因此,igbt的饱和电流变高,能够进行短路动作的最大短路脉宽变短。

10、为了保证短路耐量,通过将相邻的n+型发射极层的间隔扩大,从而能够降低每单位面积的电子注入效率,对饱和电流进行抑制。但是,如果该间隔变大,则形成p+型发射极层的区域的寄生电阻变大,vce(sat)-eoff折衷特性恶化。

11、另外,通过以比栅极电极低的电压对其它栅极电极进行驱动(例如,栅极电极为±15v,其它栅极电极为±9v),从而能够对来自栅极沟槽的电子注入进行抑制,降低饱和电流。但是,由于以不同的栅极电压进行驱动,因此栅极驱动器的动作变得复杂。

技术实现思路

1、本发明说明书所公开的技术就是鉴于以上所记载的问题而提出的,其用于防止vce(sat)-eoff折衷特性的恶化或栅极驱动器的动作复杂化,对饱和电流的增加进行抑制。

2、作为本发明说明书所公开的技术的第1方式的半导体装置具有:第1导电型的半导体基板;第1导电型的第1半导体层,其设置于所述半导体基板的表层;第2导电型的第1杂质层及第2导电型的第2杂质层,它们彼此选择性地设置于所述第1半导体层的表层;第1沟槽,其设置为从所述第1杂质层的上表面到达所述第1半导体层内;至少1个第2沟槽,其设置为从所述第2杂质层的上表面到达比所述第1半导体层的下表面更靠下方处;第1电极层,其以被氧化膜包围的方式埋入所述第1沟槽内;第2电极层,其以被氧化膜包围的方式埋入所述第2沟槽内;第1栅极电极,其与所述第1电极层连接;第2栅极电极,其与所述第2电极层连接;第2导电型的第3杂质层,其是跨所述第1杂质层的表层及所述第2杂质层的表层地设置的;第1导电型的第2半导体层,其设置于所述第1杂质层的表层,并且配置为在俯视观察时被所述第1沟槽和所述第3杂质层夹着;以及第1导电型的第3半导体层,其设置于所述第2杂质层的表层,并且配置为在俯视观察时被所述第2沟槽和所述第3杂质层夹着,所述第1半导体层的杂质浓度比所述半导体基板的杂质浓度高,所述第2杂质层的杂质浓度比所述第1杂质层的杂质浓度高,所述第3杂质层的杂质浓度比所述第2杂质层的杂质浓度高。

3、发明的效果

4、根据本发明说明书所公开的技术中的至少第1方式,能够防止vce(sat)-eoff折衷特性的恶化或栅极驱动器的动作复杂化,对饱和电流的增加进行抑制。

5、另外,通过以下所示的详细的说明和附图,本发明说明书所公开的技术涉及的目的、特征、方案、优点会更清楚。

技术特征:

1.一种半导体装置,其具有:

2.一种半导体装置,其具有:

3.根据权利要求1或2所述的半导体装置,其中,

4.根据权利要求1至3中任一项所述的半导体装置,其中,

5.根据权利要求1至3中任一项所述的半导体装置,其中,

6.根据权利要求1、3至5中任一项所述的半导体装置,还具有:

7.根据权利要求2至5中任一项所述的半导体装置,还具有:

8.根据权利要求6或7所述的半导体装置,其中,

9.根据权利要求6至8中任一项所述的半导体装置,其中,

10.根据权利要求6至9中任一项所述的半导体装置,其中,

11.一种半导体装置的制造方法,其中,

12.根据权利要求11所述的半导体装置的制造方法,其中,

13.一种半导体装置的制造方法,其中,

14.根据权利要求13所述的半导体装置的制造方法,其中,

15.根据权利要求11至14中任一项所述的半导体装置的制造方法,其中,

16.根据权利要求11至15中任一项所述的半导体装置的制造方法,其中,

技术总结

本发明涉及半导体装置及半导体装置的制造方法。对饱和电流的增加进行抑制。半导体装置具有:第1沟槽,其设置为从第1杂质层的上表面到达第1半导体层内;第2沟槽,其设置为从第2杂质层的上表面到达比第1半导体层的下表面更靠下方处;第1导电型的第2半导体层,其设置于第1杂质层的表层,配置为在俯视观察时被第1沟槽和第3杂质层夹着;以及第1导电型的第3半导体层,其设置于第2杂质层的表层,配置为在俯视观察时被第2沟槽和第3杂质层夹着。

技术研发人员:月东绫则

受保护的技术使用者:三菱电机株式会社

技术研发日:

技术公布日:2024/3/12

- 还没有人留言评论。精彩留言会获得点赞!