芯片键合应力的测量方法及芯片键合辅助结构与流程

本发明涉及一种半导体元件的制作方法及其辅助结构,特别是涉及一种半导体芯片键合应力的测量方法及芯片键合辅助结构。

背景技术:

1、芯片键合技术是指将两片半导体芯片(例如,晶片)经清洗后贴合在一起,再经过高温退火处理,在二者的界面形成化学键的连接。目前已广泛应用于半导体电路制作工艺中,成为制备集成电路的复合材料加工及实现微机电结构(包括基板工程、集成电路布线、微机电系统(mems)和封装等技术)的重要手段。

2、在半导体制作工艺的芯片键合技术中,键合应力(粘接强度)是一个非常重要的制作工艺参数,是关系到制作工艺品质的重要一环。键合应力的强度不足容易导致,加工过程中会出现芯片剥离、破裂而导致元件失效的风险。因此,在实施芯片键合步骤之后,需要在对已键合的芯片结构进行键合应力的测量与检验,以确保制作工艺的良率和品质。

3、目前,较常被应用来测量键合应力有刃片端子强度(the plug blade terminalstrength)法(也称刀片法),是采用刀片沿两个芯片之间的键合界面插入,通过观测断裂深度来估算芯片之间的键合强度。这种方法虽然使用的仪器设备较为简便,但是一种破坏性检测方法。再者,由于芯片性脆,插入刃片的步骤需要仰赖人为操作和经验。测量所得的数值可能因操作人员的不同而产生变异,导致测量误差相当大。

4、因此,有需要提供一种先进的芯片键合应力的测量方法及芯片键合辅助结构,来解决现有技术所面临的问题。

技术实现思路

1、本说明书的一实施例揭露一种芯片键合应力(bonding strength)的测量方法,包括下述步骤:先于第一芯片的第一表面形成一个辅助图案。再将第二芯片的第二表面与第一表面键合,用于形成至少一个围绕辅助图案的间隙空间。接着,分别测量此至少一个间隙空间和辅助图案的多个空间尺寸;并根据此多个空间尺寸来估计第一芯片和第二芯片之间的键合应力。

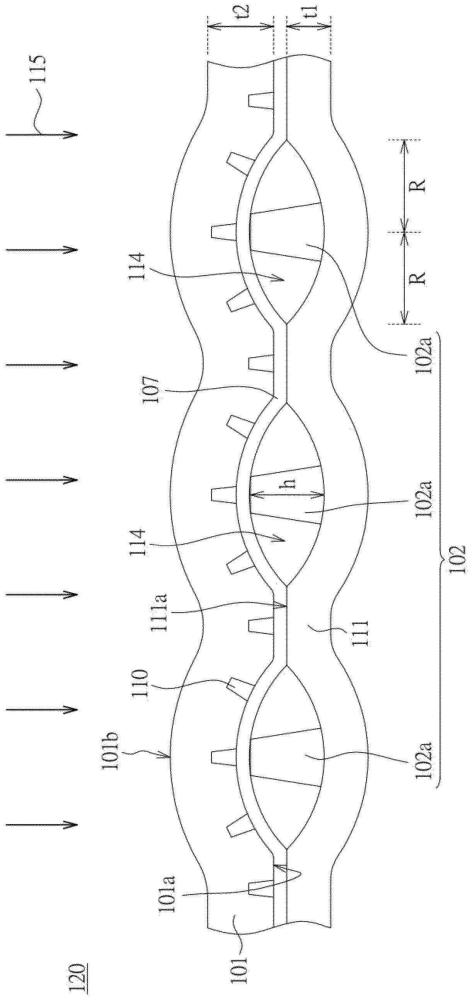

2、本说明书的另一实施例揭露一种芯片键合辅助结构,包括:第一芯片、至少一个辅助图案、第二芯片具。第一芯片具有一个第一表面。辅助图案,形成于第一表面上。第二芯片具有一个第二表面与第一表面键合,用于形成一个间隙空间围绕辅助图案。

3、根据上述实施例,本说明书是在提供一种芯片键合应力的测量方法和芯片键合辅助结构。先在要被键合的芯片之一者的键合表面上先形成凸出或凹陷的辅助图案,使被键合的二芯片在键合之后产生围绕辅助图案的间隙空间,通过非破坏性的测量方法(例如,超音波、光学或其他合适的技术),来测量辅助图案与间隙空间的尺寸,并根据测量所得的尺寸数据,配合芯片的弹性模数来估算二芯片的键合应力。由于测量过程中不会破坏芯片的键合结构,故而可以降低制作工艺成本。同时又可排除人为操作的变异因素,可提高测量的准确度。

技术特征:

1.一种芯片键合辅助结构,其特征在于,包括:

2.如权利要求1所述的芯片键合辅助结构,其中该辅助图案包括多个凸柱,该至少一间隙空间包括多个间隙空间,该多个凸柱的每一者,具有介于0.002平方毫米至0.03平方毫米的底面积以及介于50微米至100微米之间的高度;该多个间隙空间的每一者,具有介于500平方毫米至1000平方毫米的投影面积。

3.如权利要求2所述的芯片键合辅助结构,其中该多个凸柱的每一者是选自于圆柱体、圆锥体、多边柱状体、不规则形柱状体、或规则柱状体。

4.如权利要求2所述的芯片键合辅助结构,其中该多个间隙空间的每一者,仅围绕该多个凸柱中之一者。

5.如权利要求2所述的芯片键合辅助结构,其中该多个间隙空间的每一者,围绕该多个凸柱中的多个凸柱。

6.如权利要求12所述的芯片键合辅助结构,其中该多个凸柱平均分布于该第一表面上。

7.如权利要求2所述的芯片键合辅助结构,其中该多个凸柱邻接于该第一表面的边缘。

8.如权利要求1所述的芯片键合辅助结构,其中该第一芯片和该第二芯片之间,具有介于1焦耳/平方米至4焦耳/平方米的键合应力。

技术总结

本发明公开一种芯片键合应力的测量方法及芯片键合辅助结构,其中该芯片键合应力的测量方法包括下述步骤:先在第一芯片的第一表面形成一个辅助图案。再将第二芯片的第二表面与第一表面键合,用于形成至少一个围绕辅助图案的间隙空间。接着,分别测量此至少一个间隙空间和辅助图案的多个空间尺寸;并根据此多个空间尺寸来估计第一芯片和第二芯片之间的键合应力。

技术研发人员:张晟,冯健奇,赵昕

受保护的技术使用者:联华电子股份有限公司

技术研发日:

技术公布日:2024/1/5

- 还没有人留言评论。精彩留言会获得点赞!