一种解决数模干扰的封装结构及封装方法与流程

本发明涉及电子器件封装,具体而言,涉及一种解决数模干扰的封装结构及封装方法。

背景技术:

1、随着各类电子产品的高速化、复杂化和功能多样化,数模混合电路越来越多的应用到生活中各类电子产品上。数模混合电路,顾名思义,就是既有数字电路又有模拟电路,其中,数字电路可以用来修调性能,也能作为功能模块,往往一些对速度要求不高的电路,都已经由数字电路实现。常见的数模混合系统如serdes(serializer/deserializer,串行器/解串器)接口,adc(analog-to-digital converter,模数转换器),pll(phase-lockedloops,锁相环)等。

2、数模干扰,一直是困扰硬件电路设计师的瓶颈。众所周知,现实的世界都是模拟的,只有将模拟信号转变成数字信号,才方便做进一步的处理。模拟信号和数字信号的转变是否实时、精确,是电路设计的重要指标。

3、数模干扰的机理,即数字对模拟的影响可以分为以下两种情况:

4、1、串扰,串扰一般是通过数字与模拟信号线间的分布参数相互影响。

5、2、公共阻抗耦合,公共阻抗耦合是指由于骚扰源与敏感部位共用一个线路阻抗而产生的。当数字信号与模拟信号共地时,由于地线在高频时存在一定的阻抗,因此数字信号回流流过时将产生一个压降,这就是共模电压源。此时,如果共模电流流经模拟区域,在模拟区域地上产生压降,这个压降如果叠加在模拟信号上,便会影响模拟信号。

6、传统解决数模干扰的方法,基本都是在pcb(printed circuit board,印制电路板)上做器件、电路的隔离处理,这样的处理方式对pcb设计师的设计水平有一定的要求,收益大小也会随着pcb尺寸、材料等原因受到影响。

技术实现思路

1、本发明旨在提供一种解决数模干扰的封装结构及封装方法,以解决上述存在的问题,该封装结构及封装方法可以在电路更靠近芯片会更容易发生数模干扰的位置以及pcb隔离无法接触的位置进行电路的隔离。

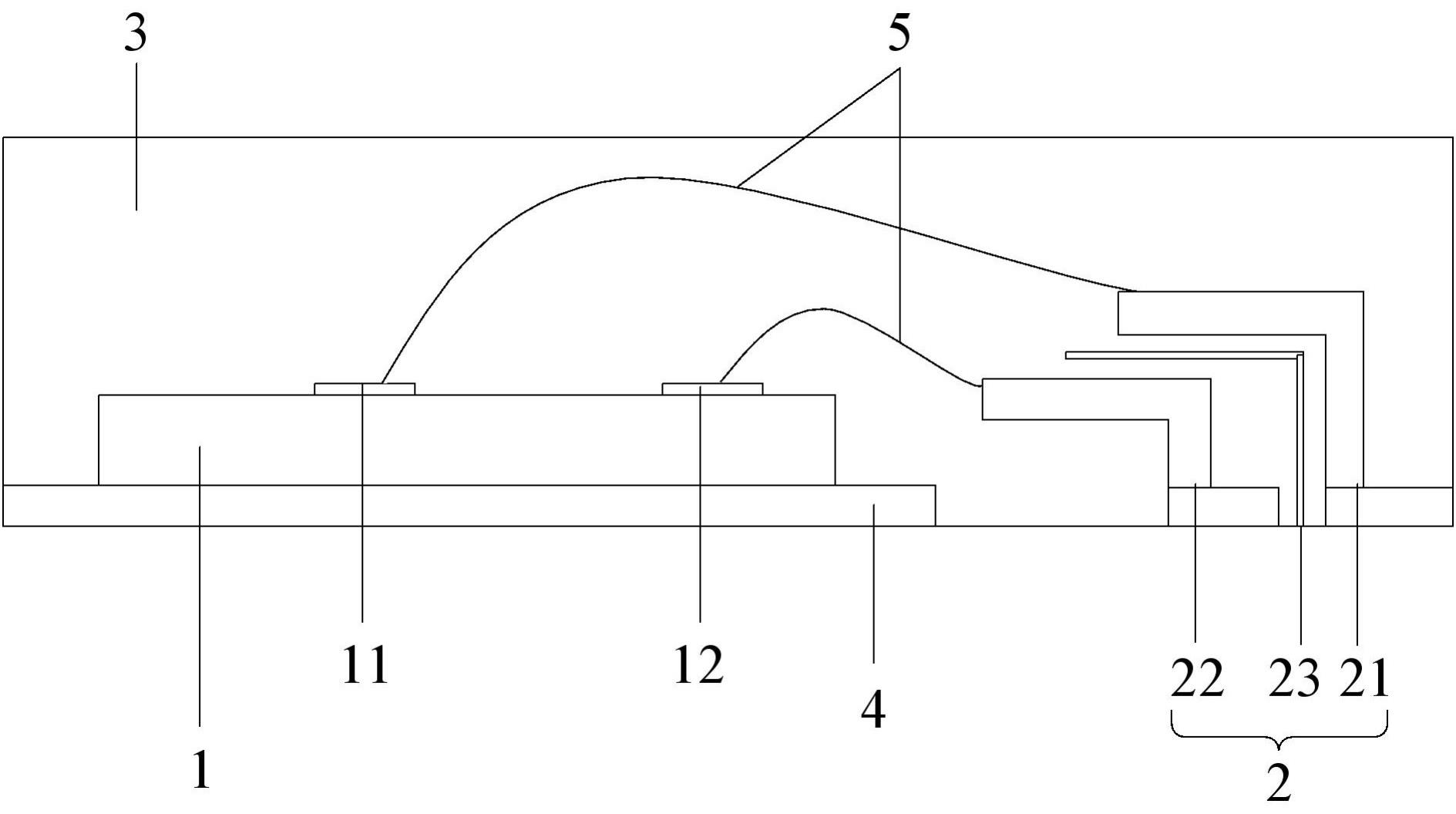

2、本发明提供一种解决数模干扰的封装结构,包括数模混合芯片、封装框架以及用于封装数模混合芯片和封装框架的塑封体;

3、所述数模混合芯片分为数字部分和模拟部分;所述数模混合芯片上表面设置有对应数字部分的数字信号焊盘,以及对应模拟部分的模拟信号焊盘;所述数模混合芯片下表面的接地焊盘包括对应数字部分的数字接地焊盘和对应模拟部分的模拟接地焊盘,且数字接地焊盘和模拟接地焊盘相互独立;

4、所述封装框架包括封装上层引脚和封装下层引脚以及设置在封装上层引脚和封装下层引脚之间的屏蔽环;所述封装上层引脚和封装下层引脚分别与数字信号焊盘和模拟信号焊盘键合;

5、所述数字接地焊盘、模拟接地焊盘、封装上层引脚和封装下层引脚露出塑封体。

6、可选的,所述封装上层引脚与数字信号焊盘键合;所述封装下层引脚与模拟信号焊盘键合。

7、可选的,所述封装下层引脚与数字信号焊盘键合;所述封装上层引脚与模拟信号焊盘键合。

8、可选的,所述封装上层引脚和封装下层引脚分别通过金属键合线与数字信号焊盘和模拟信号焊盘键合。

9、可选的,所述数字接地焊盘、模拟接地焊盘、封装上层引脚和封装下层引脚露出塑封体的部分具有阻氧层。

10、本发明还提供一种解决数模干扰的封装方法,包括如下步骤:

11、s1,根据待封装的数模混合芯片的数字部分和模拟部分,将接地焊盘进行裂片处理,形成对应数字部分的数字接地焊盘和对应模拟部分的模拟接地焊盘,且数字接地焊盘和模拟接地焊盘相互独立;

12、s2,根据待封装的数模混合芯片的数字部分和模拟部分,将封装上层引脚和封装下层引脚放置在对应位置,并在封装上层引脚和封装下层引脚之间设置屏蔽环;

13、s3,将待封装的数模混合芯片安装在接地焊盘上,使得其数字部分和模拟部分与相应的数字接地焊盘和模拟接地焊盘对应接触;

14、s4,将待封装的数模混合芯片上表面对应数字部分的数字信号焊盘以及对应模拟部分的模拟信号焊盘,分别与封装上层引脚和封装下层引脚键合;

15、s5,对待封装的数模混合芯片、数字接地焊盘、模拟接地焊盘、封装上层引脚和封装下层引脚注塑形成塑封体,并使得数字接地焊盘、模拟接地焊盘、封装上层引脚和封装下层引脚露出塑封体。

16、可选的,所述封装上层引脚与数字信号焊盘键合;所述封装下层引脚与模拟信号焊盘键合。

17、可选的,所述封装下层引脚与数字信号焊盘键合;所述封装上层引脚与模拟信号焊盘键合。

18、可选的,步骤s4中,所述封装上层引脚和封装下层引脚分别通过金属键合线与数字信号焊盘和模拟信号焊盘键合。

19、可选的,所述解决数模干扰的封装方法,还包括:

20、s6,对数字接地焊盘、模拟接地焊盘、封装上层引脚和封装下层引脚露出塑封体的部分进行电镀,形成阻氧层。

21、综上所述,由于采用了上述技术方案,本发明的有益效果是:

22、传统解决数模干扰的方法是在pcb上做器件、电路的隔离处理,会受到pcb尺寸、材料等原因的影响,而本发明改进了数模混合芯片采用的框架封装的封装结构,在电路更靠近芯片会更容易发生数模干扰的位置以及pcb隔离无法接触的位置进行电路的隔离,封装与芯片会作为一个完整的产品个体,因此不会受到pcb尺寸、材料影响,同时提升了封装抗数模干扰和芯片散热的能力。

技术特征:

1.一种解决数模干扰的封装结构,其特征在于,包括数模混合芯片(1)、封装框架(2)以及用于封装数模混合芯片(1)和封装框架(2)的塑封体(3);

2.根据权利要求1所述的一种解决数模干扰的封装结构,其特征在于,所述封装上层引脚(21)与数字信号焊盘(11)键合;所述封装下层引脚(22)与模拟信号焊盘(12)键合。

3.根据权利要求1所述的一种解决数模干扰的封装结构,其特征在于,所述封装下层引脚(22)与数字信号焊盘(11)键合;所述封装上层引脚(21)与模拟信号焊盘(12)键合。

4.根据权利要求1-3任一项所述的一种解决数模干扰的封装结构,其特征在于,所述封装上层引脚(21)和封装下层引脚(22)分别通过金属键合线(5)与数字信号焊盘(11)和模拟信号焊盘(12)键合。

5.根据权利要求1所述的一种解决数模干扰的封装结构,其特征在于,所述数字接地焊盘(41)、模拟接地焊盘(42)、封装上层引脚(21)和封装下层引脚(22)露出塑封体(3)的部分具有阻氧层。

6.一种解决数模干扰的封装方法,其特征在于,包括如下步骤:

7.根据权利要求6所述的一种解决数模干扰的封装方法,其特征在于,步骤s4中,所述封装上层引脚(21)与数字信号焊盘(11)键合;所述封装下层引脚(22)与模拟信号焊盘(12)键合。

8.根据权利要求6所述的一种解决数模干扰的封装方法,其特征在于,步骤s4中,所述封装下层引脚(22)与数字信号焊盘(11)键合;所述封装上层引脚(21)与模拟信号焊盘(12)键合。

9.根据权利要求6-8任一项所述的一种解决数模干扰的封装方法,其特征在于,步骤s4中,所述封装上层引脚(21)和封装下层引脚(22)分别通过金属键合线(5)与数字信号焊盘(11)和模拟信号焊盘(12)键合。

10.根据权利要求6所述的一种解决数模干扰的封装方法,其特征在于,还包括:

技术总结

本发明提供一种解决数模干扰的封装结构及封装方法,所述封装结构包括数模混合芯片、封装框架以及用于封装数模混合芯片和封装框架的塑封体;数模混合芯片分为数字部分和模拟部分;数模混合芯片上表面设置有对应数字部分和模拟部分的数字信号焊盘和模拟信号焊盘;数模混合芯片下表面的接地焊盘包括对应数字部分和模拟部分的数字接地焊盘和模拟接地焊盘;封装框架包括封装上层引脚和封装下层引脚以及设置在封装上层引脚和封装下层引脚之间的屏蔽环;所述封装上层引脚和封装下层引脚分别与数字信号焊盘和模拟信号焊盘键合;所述数字接地焊盘、模拟接地焊盘、封装上层引脚和封装下层引脚露出塑封体。本发明提升了封装抗数模干扰和芯片散热的能力。

技术研发人员:闵云川,杜军,彭一弘

受保护的技术使用者:成都电科星拓科技有限公司

技术研发日:

技术公布日:2024/1/15

- 还没有人留言评论。精彩留言会获得点赞!