半导体测试结构及测试方法与流程

本发明涉及半导体领域,尤其涉及一种半导体测试结构及测试方法。

背景技术:

1、在半导体刻蚀工艺中,刻蚀负载效应可能会导致刻蚀出现偏差,由于刻蚀图案的密度不同,刻蚀图案密度越大的区域出现偏差的可能性越大,这极大地影响了晶圆刻蚀质量。现有技术仅仅根据工艺整合需求对刻蚀区域进行光学修正(opc),繁琐且耗费时间精力。

2、随着更向上技术节点先进制程的推进开发,为保护客户芯片版图设计的范围包容性,如何减小不同密度芯片版图的刻蚀误差,提高刻蚀质量,是目前需要解决的问题。

技术实现思路

1、本发明所要解决的技术问题是减小不同密度芯片版图的刻蚀误差,提高刻蚀质量,提供一种半导体测试结构及测试方法。

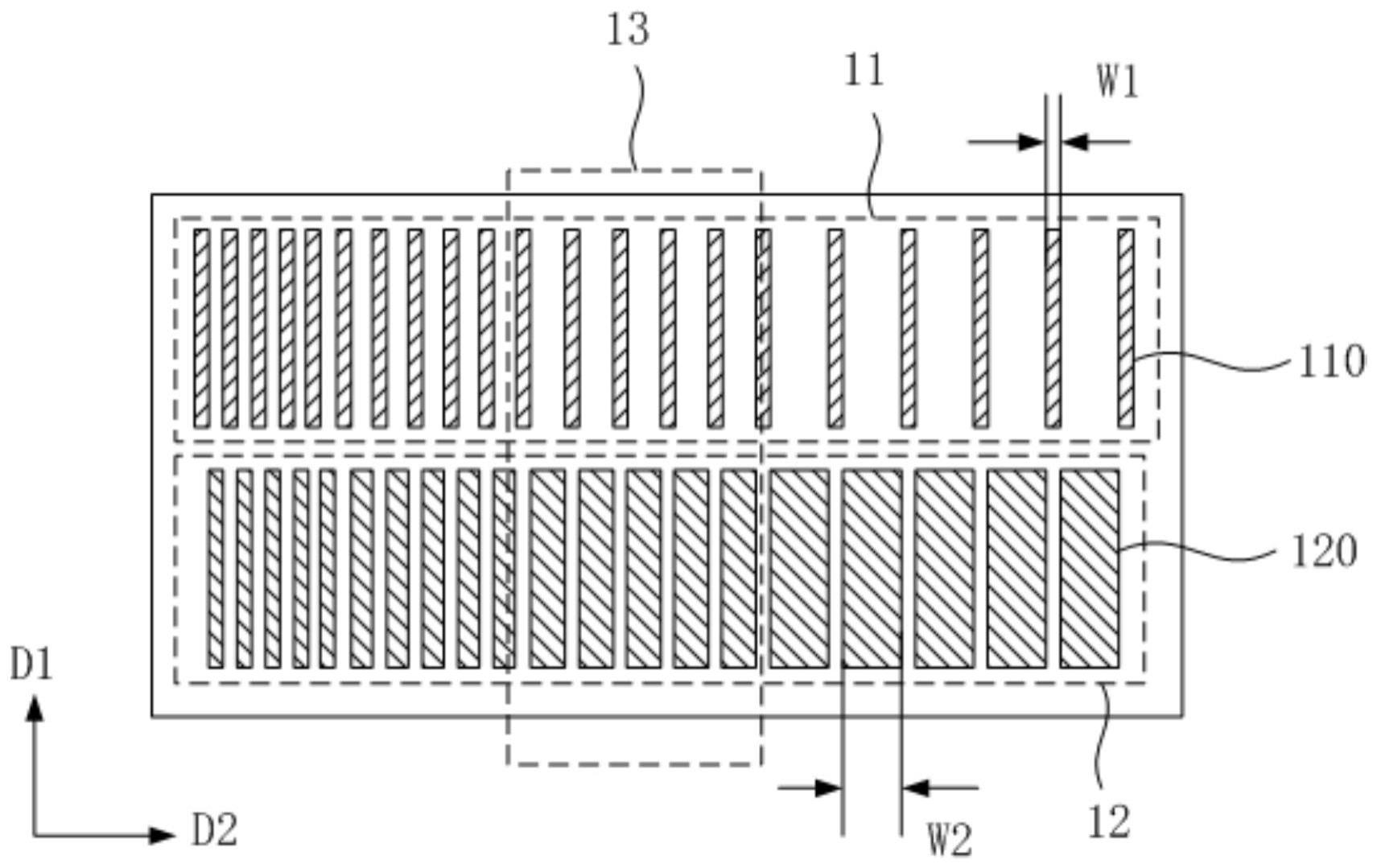

2、为了解决上述问题,本发明提供了一种半导体测试结构,包括:第一图形序列,所述第一图形序列包括多个沿第一方向延伸、沿第二方向排布的第一图形,且相邻两所述第一图形的空隙沿所述第一方向逐渐增大;第二图形序列,与所述第一图形序列沿所述第一方向相邻设置,所述第二图形序列包括多个沿所述第一方向延伸、沿所述第二方向排布的第二图形,且所述第二图形的宽度沿所述第一方向逐渐增大;其中,所述第二方向垂直于所述第一方向。

3、在一些实施例中,所述第二图形序列与所述第一图形序列沿所述第一方向相邻且互补设置,相邻两所述第一图形的空隙的宽度与互补位置处的所述第二图形的宽度基本相同。

4、在一些实施例中,每五个所述第一图形及互补设置的五个所述第二图形组成一个测试单元。

5、在一些实施例中,每一所述测试单元内,相邻两所述第一图形的空隙的宽度相同,所有所述第二图形的宽度相同。

6、在一些实施例中,所述第一图形序列的所有所述第一图形的宽度相同,所述第二图形序列的所述第二图形的宽度范围为220nm~1200nm,且相邻两所述测试单元的第二图形的宽度差值为100nm。

7、为了解决上述问题,本发明还提供了一种半导体测试方法,采用本发明所述的半导体测试结构,所述方法包括如下步骤:提供一初始半导体结构;以所述半导体测试结构为模板在所述初始半导体结构表面形成掩膜层,并记录第一偏移值;刻蚀所述初始半导体结构以形成刻蚀图案;将所述刻蚀图案与所述半导体测试结构对比以获得第二偏移值;若第一偏移值与第二偏移值的差值大于或等于一预设阈值,对所述刻蚀图案进行补偿。

8、在一些实施例中,所述刻蚀图案包括正向刻蚀图案与反向刻蚀图案,所述正向刻蚀图案与所述反向刻蚀图案均包括多个沿所述第一方向延伸、沿所述第二方向排布的沟槽图案,且所述正向刻蚀图案与所述反向刻蚀图案沿所述第一方向相邻设置,所述正向刻蚀图案包括多个沿所述第一方向延伸、沿所述第二方向排布的第一沟槽图案;所述反向刻蚀图案包括多个沿所述第一方向延伸、沿所述第二方向排布的第二沟槽图案;所述第二偏移值包括第二正向偏移值及第二反向偏移值。

9、在一些实施例中,所述刻蚀图案为亮场图案,所述的将所述刻蚀图案与所述半导体测试结构对比以获得第二偏移值的步骤进一步包括如下步骤:将所述正向刻蚀图案与所述半导体测试结构的第一图形序列进行对比,获取每一第一沟槽图案与相应的所述第一图案的边缘差值,记为第二正向偏移值;将所述反向刻蚀图案与所述半导体测试结构的第二图形序列进行对比,获取每一第二沟槽图案与相应的所述第二图案的边缘差值,记为第二反向偏移值;对所述第二正向偏移值及所述第二反向偏移值求和得到所述第二偏移值。

10、在一些实施例中,所述刻蚀图案为暗场图案,所述的将所述刻蚀图案与所述半导体测试结构对比以获得第二偏移值的步骤进一步包括如下步骤:将所述正向刻蚀图案与所述半导体测试结构的第二图形序列进行对比,获取每一第一沟槽图案与所述第二图案的边缘差值,记为第二正向偏移值;将所述反向刻蚀图案与所述半导体测试结构的第一图形序列进行对比,获取每一第二沟槽图案与所述第一图案的边缘差值,记为第二反向偏移值;对所述第二正向偏移值及所述第二反向偏移值求和得到所述第二偏移值。

11、在一些实施例中,所述预设阈值小于或等于10nm。

12、在一些实施例中,所述的对刻蚀图案进行补偿的步骤进一步包括:采用选择性偏差算法表对所述刻蚀图案进行光学临近效应修正。

13、上述技术方案通过设置不同密度的图形序列,以监控不同图形密度的刻蚀工艺中刻蚀负载影响导致的刻蚀偏移,减小不同密度芯片版图的刻蚀误差,提高刻蚀质量。所述半导体测试结构也可以用来替代关键尺寸棒(cd bar)测量关键尺寸(cd),以及替代金属光学关键尺寸(metal ocd)测量厚度。该结构大大提高了功能性以及节省了时间,更精准范围宽广的监控刻蚀偏移。

14、应当理解的是,以上的一般描述和后文的细节描述仅是示例性和解释性的,并不能限制本发明。对于相关领域普通技术人员已知的技术、方法和设备可能不作详细讨论,但在适当情况下,所述技术、方法和设备应当被视为授权说明书的一部分。

技术特征:

1.一种半导体测试结构,其特征在于,包括:

2.根据权利要求1所述的半导体测试结构,其特征在于,所述第二图形序列与所述第一图形序列沿所述第一方向相邻且互补设置,相邻两所述第一图形的空隙的宽度与互补位置处的所述第二图形的宽度基本相同。

3.根据权利要求2所述的半导体测试结构,其特征在于,每五个所述第一图形及互补设置的五个所述第二图形组成一个测试单元。

4.根据权利要求3所述的半导体测试结构,其特征在于,在每一所述测试单元内,相邻两所述第一图形的空隙的宽度相同,所有所述第二图形的宽度相同。

5.根据权利要求1所述的半导体测试结构,其特征在于,

6.一种半导体测试方法,其特征在于,采用权利要求1~5任一项所述的半导体测试结构,所述方法包括如下步骤:

7.根据权利要求6所述的半导体测试方法,其特征在于,所述刻蚀图案包括正向刻蚀图案与反向刻蚀图案,且所述正向刻蚀图案与所述反向刻蚀图案沿所述第一方向相邻设置,所述正向刻蚀图案包括多个沿所述第一方向延伸、沿所述第二方向排布的第一沟槽图案;所述反向刻蚀图案包括多个沿所述第一方向延伸、沿所述第二方向排布的第二沟槽图案;

8.根据权利要求7所述的半导体测试方法,其特征在于,所述刻蚀图案为亮场图案,所述的将所述刻蚀图案与所述半导体测试结构对比以获得第二偏移值的步骤进一步包括如下步骤:

9.根据权利要求7所述的半导体测试方法,其特征在于,所述刻蚀图案为暗场图案,所述的将所述刻蚀图案与所述半导体测试结构对比以获得第二偏移值的步骤进一步包括如下步骤:

10.根据权利要求6所述的半导体测试方法,其特征在于,所述预设阈值小于或等于10nm。

11.根据权利要求6所述的半导体测试方法,其特征在于,所述的对刻蚀图案进行补偿的步骤进一步包括:采用选择性偏差算法表对所述刻蚀图案进行光学临近效应修正。

技术总结

本发明提供一种半导体测试结构及测试方法。所述半导体测试结构包括:第一图形序列,所述第一图形序列包括多个沿第一方向延伸、沿第二方向排布的第一图形,且相邻两所述第一图形的空隙沿所述第一方向逐渐增大;第二图形序列,与所述第一图形序列沿所述第一方向相邻设置,所述第二图形序列包括多个沿所述第一方向延伸、沿所述第二方向排布的第二图形,且所述第二图形的宽度沿所述第一方向逐渐增大;其中,所述第二方向垂直于所述第一方向。上述技术方案通过设置不同密度的图形序列,以监控不同图形密度的刻蚀工艺中刻蚀负载影响导致的刻蚀偏移,减小不同密度芯片版图的刻蚀误差,提高刻蚀质量。

技术研发人员:王嘉南,叶黄

受保护的技术使用者:上海积塔半导体有限公司

技术研发日:

技术公布日:2024/1/16

- 还没有人留言评论。精彩留言会获得点赞!