半导体器件的制作方法

本申请涉及半导体,特别是一种半导体器件。

背景技术:

1、随着集成电路(integrated circuit,ic)的快速发展,晶体管的尺寸缩小,电路的复杂度增加。由于电路的复杂度增加,电路的规划若稍有不慎,则容易产生漏电流的状况。因此,在集成电路中,相邻电晶体之间的电性隔离是个相当重要的议题。

2、现有技术中,两个相邻的晶体管之间透过设置隔离区来达到电性隔离。具体而言,两个相邻的晶体管为第一晶体管和第二晶体管,第一晶体管和第二晶体管共用衬底以及衬底接触孔,第一晶体管和衬底接触孔之间设置隔离区,第二晶体管和衬底接触孔之间设置隔离区。但是由于隔离区的设置,导致半导体器件的版图面积增加。

技术实现思路

1、根据前述,本申请提供一种半导体器件,解决因隔离区造成的半导体器件的版图面积增加以及闩锁效应的问题。

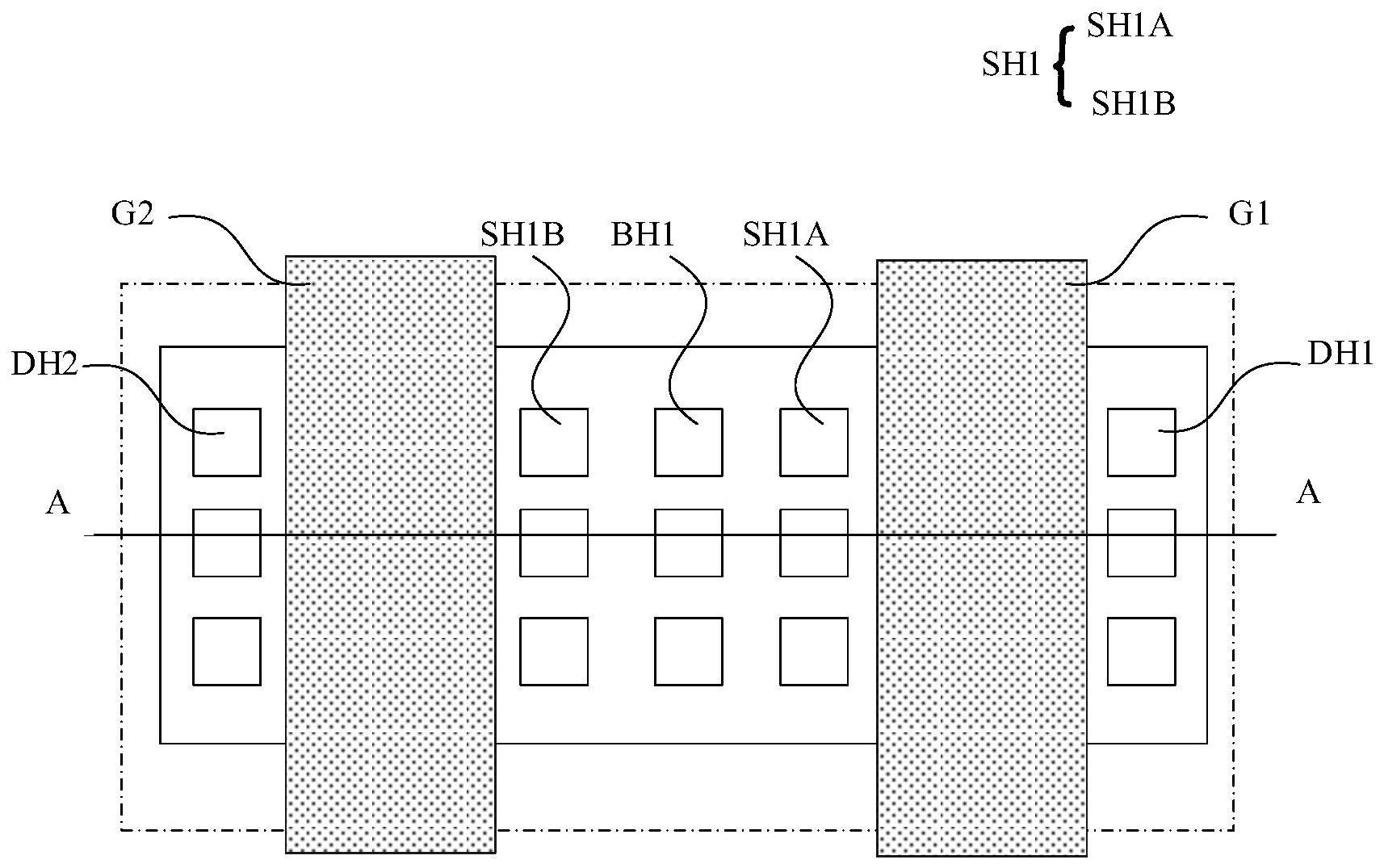

2、基于上述目的,本申请提供一种半导体器件,包括第一晶体管、第二晶体管以及至少一个体区接触孔。第一晶体管包括第一漏极以及第一栅极,第一漏极位于第一栅极的一侧。第二晶体管包括第二漏极以及第二栅极,第二漏极位于第二栅极的一侧,第一晶体管与第二晶体管具有共同的有源区,第一晶体管与第二晶体管具有共用的源极,源极设置于第一栅极和第二栅极之间并对应至少一个源极接触孔。至少一个体区接触孔设置于第一栅极和第二栅极之间且与至少一个源极接触孔相邻,其中,至少一个源极接触孔的电位与至少一个体区接触孔的电位相同。

3、在本申请的实施例中,至少一个体区接触孔与其所在的衬底或其所在的阱区连接,使得衬底或阱区通过体区接触孔与外部参考电压连接。

4、在本申请的实施例中,半导体器件还包括金属层,金属层设置于第一栅极和第二栅极之间,源极及至少一个体区接触孔透过金属层连接,使得至少一个源极接触孔的电位与至少一个体区接触孔的电位相同。

5、在本申请的实施例中,第一晶体管和第二晶体管具有共同的衬底。

6、在本申请的实施例中,在至少一个源极接触孔的数目为一个,且至少一个体区接触孔包括第一体区接触孔以及第二体区接触孔时,第一体区接触孔以及第二体区接触孔设置于源极接触孔的相对两侧。

7、在本申请的实施例中,在至少一个源极接触孔包括第一源极接触孔以及第二源极接触孔,且至少一个体区接触孔的数目为一个时,第一源极接触孔及第二源极接触孔设置于体区接触孔的相对两侧。

8、在本申请的实施例中,在至少一个源极接触孔包括多个第一源极接触孔以及多个第二源极接触孔,且至少一个体区接触孔的数目为多个时,体区接触孔设置于第一源极接触孔和第二源极接触孔之间。

9、在本申请的实施例中,在至少一个源极接触孔包括第一源极接触孔以及第二源极接触孔,且至少一个体区接触孔包括第一体区接触孔以及第二体区接触孔时,第一源极接触孔和第二源极接触孔位于第一体区接触孔及第二体区接触孔之间,且第一源极接触孔与第二源极接触孔并排设置。

10、在本申请的实施例中,在至少一个源极接触孔包括第一源极接触孔以及第二源极接触孔,且至少一个体区接触孔包括第一体区接触孔以及第二体区接触孔时,第一体区接触孔及第二体区接触孔位于第一源极接触孔和第二源极接触孔之间,且第一体区接触孔与第二体区接触孔并排设置。

11、在本申请的实施例中,在至少一个源极接触孔的数目为一个,且至少一体区接触孔包括多个第一体区接触孔和多个第二体区接触孔时,多个第一体区接触孔和多个第二体区接触孔围绕源极接触孔。

12、在本申请的实施例中,在至少一个源极接触孔的数目为多个,且至少一体区接触孔包括第一体区接触孔以及第二体区接触孔时,多个源极接触孔设置于第一体区接触孔和第二体区接触孔之间。

13、综上所述,本申请的半导体器件,透过共同的有源区以及共用的源极,且配置源极接触孔的电位与体区接触孔的电位相同,而无需隔离区的配置,从而减小半导体器件的版图面积。另外,由于共用的源极的配置以及源极接触孔的电位与体区接触孔的电位相同,减少衬底的寄生电阻或n型阱区的寄生电阻,可降低闩锁效应的发生机会,当本申请的半导体器件应用于芯片时,增加芯片的抗闩锁的能力。

14、上述说明仅是本申请技术方案的概述,为了能够更清楚了解本申请的技术手段,并可依照说明书的内容予以实施,以下以本申请较佳的实施例并配合附图对本申请进行详细说明。

技术特征:

1.一种半导体器件,包括:

2.如权利要求1所述的半导体器件,其特征在于,所述至少一个体区接触孔与其所在的衬底或其所在的阱区连接,使得所述衬底或所述阱区通过体区接触孔与外部参考电压连接。

3.如权利要求1所述的半导体器件,其特征在于,还包括金属层,所述金属层设置于所述第一栅极和所述第二栅极之间,所述源极及所述至少一个体区接触孔透过所述金属层连接,使得所述至少一个源极接触孔的电位与所述至少一个体区接触孔的电位相同。

4.如权利要求1所述的半导体器件,其特征在于,所述第一晶体管和所述第二晶体管具有共同的衬底。

5.如权利要求1所述的半导体器件,其特征在于,在所述至少一个源极接触孔的数目为一个,且所述至少一个体区接触孔包括第一体区接触孔以及第二体区接触孔时,所述第一体区接触孔以及所述第二体区接触孔设置于所述源极接触孔的相对两侧。

6.如权利要求1所述的半导体器件,其特征在于,在所述至少一个源极接触孔包括第一源极接触孔以及第二源极接触孔,且所述至少一个体区接触孔的数目为一个时,所述第一源极接触孔及所述第二源极接触孔设置于所述体区接触孔的相对两侧。

7.如权利要求1所述的半导体器件,其特征在于,在所述至少一个源极接触孔包括多个第一源极接触孔以及多个第二源极接触孔,且所述至少一个体区接触孔的数目为多个时,所述体区接触孔设置于所述第一源极接触孔和所述第二源极接触孔之间。

8.如权利要求1所述的半导体器件,其特征在于,在所述至少一个源极接触孔包括第一源极接触孔以及第二源极接触孔,且所述至少一个体区接触孔包括第一体区接触孔以及第二体区接触孔时,所述第一源极接触孔和所述第二源极接触孔位于所述第一体区接触孔及所述第二体区接触孔之间,且所述第一源极接触孔与所述第二源极接触孔并排设置。

9.如权利要求1所述的半导体器件,其特征在于,在所述至少一个源极接触孔包括第一源极接触孔以及第二源极接触孔,且所述至少一个体区接触孔包括第一体区接触孔以及第二体区接触孔时,所述第一体区接触孔及所述第二体区接触孔位于所述第一源极接触孔和所述第二源极接触孔之间,且所述第一体区接触孔与所述第二体区接触孔并排设置。

10.如权利要求1所述的半导体器件,其特征在于,在所述至少一个源极接触孔的数目为一个,且所述至少一体区接触孔包括多个第一体区接触孔和多个第二体区接触孔时,所述多个第一体区接触孔和所述多个第二体区接触孔围绕所述源极接触孔。

11.如权利要求1所述的半导体器件,其特征在于,在所述至少一个源极接触孔的数目为多个,且所述至少一体区接触孔包括第一体区接触孔以及第二体区接触孔时,所述多个源极接触孔设置于所述第一体区接触孔和所述第二体区接触孔之间。

技术总结

本申请提供一种半导体器件,包括第一晶体管、第二晶体管以及至少一个体区接触孔。第一晶体管包括第一漏极以及第一栅极。第二晶体管包括第二漏极以及第二栅极。第一晶体管与第二晶体管具有共同的有源区,第一晶体管与第二晶体管具有共用的源极,源极设置于第一栅极和第二栅极之间并对应至少一个源极接触孔。至少一个体区接触孔设置于第一栅极和第二栅极之间且与至少一个源极接触孔相邻,至少一个源极接触孔的电位与至少一个体区接触孔的电位相同。透过共用的源极且配置源极接触孔的电位与体区接触孔的电位相同,达成电性隔离,而无需隔离区的配置,从而减小半导体器件的版图面积。

技术研发人员:孙再伟,袁华锋,姚刚,陈一丹,楼晓燕

受保护的技术使用者:矽力杰半导体技术(杭州)有限公司

技术研发日:

技术公布日:2024/1/16

- 还没有人留言评论。精彩留言会获得点赞!