InP基平衡探测器集成芯片及其制备方法

本发明涉及光电子领域,尤其涉及一种inp基平衡探测器集成芯片及其制备方法。

背景技术:

1、信息时代下,各行业的飞速发展离不开通信技术水平的提升,而随着通信内容种类日益丰富和信息传输速率不断提升,对光通信接收技术也有更高的需求。光电探测器作为光通信接收端的核心器件,在长距离光通信数据传递中具有重要应用价值,在性能上应具有高带宽,高速,高响应度等特性。目前实现长距离光通信运输主要采用以波分复用主导的多路传输和以光强度、相位等作为通信信号为主的相干光通信传输,后者随着dsp数字信号处理技术的发展逐渐成为当下重要的光通信传输方式。

2、相干光通信采用的接收方式包括多探测器并接结构和平衡探测器结构,相比于传统采用多个探测器并接方式,平衡探测器结构的出现提高了芯片结构的利用率,减少器件互连带来的光功率损耗和相位偏差等问题,同时其还能与多种器件和波导结构集成实现诸多功能。

技术实现思路

1、鉴于上述问题,本发明提供了一种inp基平衡探测器集成芯片及其制备方法。

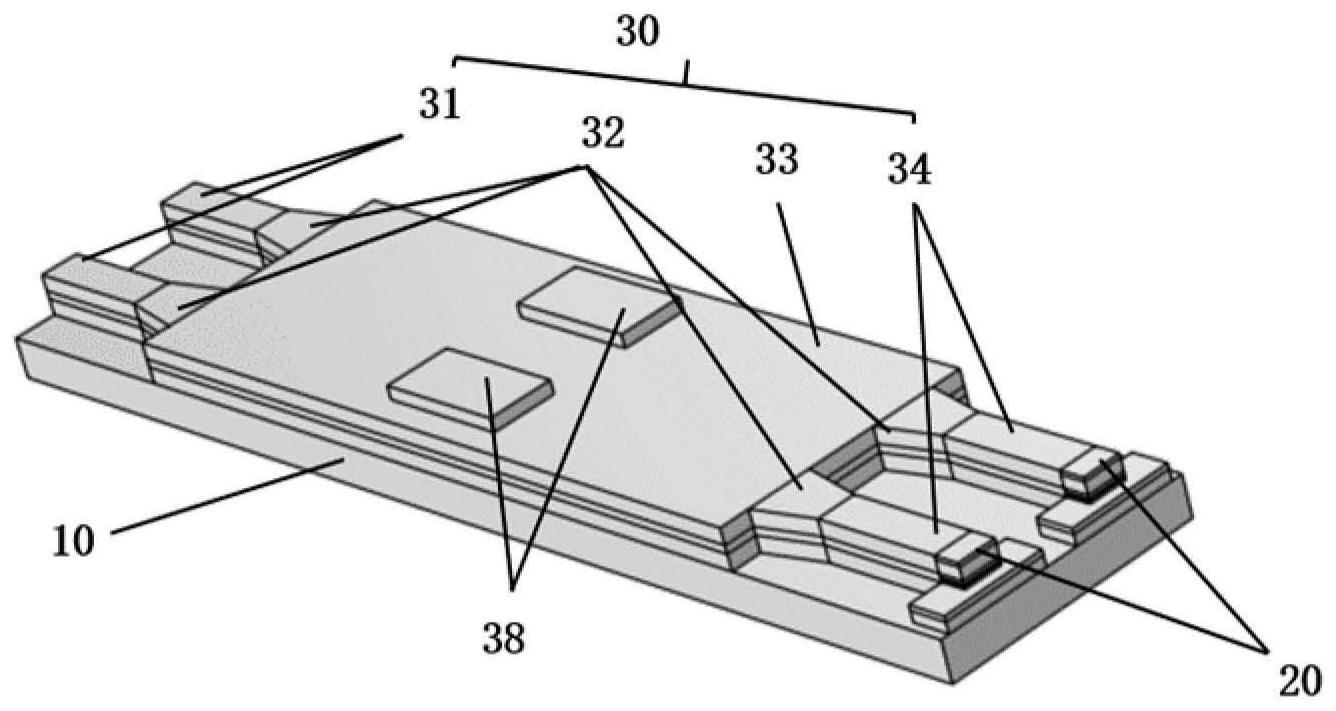

2、根据本发明的第一个方面,提供了一种inp基平衡探测器集成芯片,包括:

3、衬底;

4、多模干涉耦合波导区,位于所述衬底之上,用于耦合信号光和本征光并实现功率均分,得到均分相干光信号;

5、平衡探测器区,位置于所述衬底之上,用于将所述均分相干光信号转化为电信号;

6、其中,所述多模干涉耦合波导区与所述平衡探测器区对接。

7、根据本发明实施例,所述多模干涉耦合波导区为2×2波导结构。

8、根据本发明实施例,所述多模干涉耦合波导区自下而上依次包括:与衬底直接接触的下波导层,波导芯层,上波导层,以及位于多模干涉区中心处金属接触结构。

9、根据本发明实施例,所述多模干涉耦合波导区包括:输入波导区,渐变耦合波导区,多模干涉区以及输出波导区;

10、所述多模干涉区的两侧对接所述分布渐变耦合波导区,一侧对接分布渐变耦合波导区与输入波导区对接,另一侧对接分布渐变耦合波导区与输出波导区对接;

11、其中,所述所述多模干涉耦合波导区的输出波导区与所述平衡探测器区对接。

12、根据本发明实施例,在需要降低输出功率不平均度的情况下,在所述上波导层上方增加金属接触结构,通过微量电注入方式对输出功率差进行微调从而降低输出功率不平均度。

13、根据本发明实施例,所述平衡探测器区自下而上依次包括:n接触层,光学匹配层,第一吸收层,第二吸收层,能带过渡层,上包层,p接触层,n电极,设置于第一吸收层上的n电极,设置于p接触层之上的p电极;

14、所述n接触层和所述光学匹配层与所述下波导层对接;

15、所述第一吸收层和所述第二吸收层与所述波导芯层对接;

16、所述上包层和所述p接触层与所述上波导层对接。

17、根据本发明实施例,所述第一吸收层、第二吸收层和能带过渡层设置厚度与波导芯层厚度相匹配。

18、根据本发明实施例,所述下波导层为n掺杂的inp层,掺杂浓度为5×1017cm-3,厚度在0.6-1um;

19、所述波导芯层为未掺杂的与inp晶格匹配的ingaasp层,厚度在500-800nm;

20、所述上波导层为未掺杂的inp层,厚度在0.8-1.2um。

21、根据本发明的第二个方面,提供了一种inp基平衡探测器集成芯片的制备方法,包括:

22、制备衬底;

23、制备位于所述衬底之上的多模干涉耦合波导区,所述多模干涉耦合波导区用于耦合信号光和本征光并实现功率均分,得到均分相干光信号;

24、制备位于所述衬底之上的平衡探测器区,所述平衡探测器区用于将所述均分相干光信号转化为电信号;

25、其中,所述多模干涉耦合波导区与所述平衡探测器区对接。

26、根据本发明实施例,所述制备位于所述衬底之上的多模干涉耦合波导区包括:

27、依次制备与衬底直接接触的下波导层,波导芯层,上波导层,以及位于多模干涉区中心处金属接触结构;

28、所述制备位于所述衬底之上的平衡探测器区包括:

29、依次制备n接触层,光学匹配层,第一吸收层,第二吸收层,能带过渡层,上包层,p接触层,n电极,设置于第一吸收层上的n电极,设置于p接触层之上的p电极;

30、所述n接触层和所述光学匹配层与所述下波导层对接;

31、所述第一吸收层和所述第二吸收层与所述波导芯层对接;

32、所述上包层和所述p接触层与所述上波导层对接。

33、本发明所提出的一种inp基平衡探测器集成芯片及其制备方法至少具有以下有益效果:

34、1、该平衡探测器集成芯片采用单片集成技术,将多模干涉耦合波导和平衡光探测器组合,从而有效减小了器件互连尺寸,集成后的芯片能够在相干光领域、空间自由光通信领域具有一定的应用价值。

35、2、本发明采用多模干涉耦合波导结构,通过添加可调谐电极以输入电流达到微量调节波导折射率的目的,因此在此结构下能够降低输出光的不平衡度,进而实现对rin噪声的抑制。

36、3、本发明所提到的具有双吸收区的平衡探测器,能将通过多模干涉耦合器均分的光信号充分吸收并转化为电信号,通过对该探测器其他层结构的材料和厚度的设计,使其能够实现高带宽,高响应度的特点,应用于高速光通信领域。

技术特征:

1.一种inp基平衡探测器集成芯片,其特征在于,包括:

2.根据权利要求1所述的inp基平衡探测器集成芯片,其特征在于,所述多模干涉耦合波导区为2×2波导结构。

3.根据权利要求1所述的inp基平衡探测器集成芯片,其特征在于,所述多模干涉耦合波导区自下而上依次包括:与衬底直接接触的下波导层,波导芯层,上波导层,以及位于多模干涉耦合波导区中心处的金属接触结构。

4.根据权利要求1所述的inp基平衡探测器集成芯片,其特征在于,所述多模干涉耦合波导区包括:输入波导区,渐变耦合波导区,多模干涉区以及输出波导区;

5.根据权利要求1所述的inp基平衡探测器集成芯片,其特征在于,在需要降低输出功率不平均度的情况下,在所述上波导层上方增加金属接触结构,通过微量电注入方式对输出功率差进行微调从而降低输出功率不平均度。

6.根据权利要求3所述的inp基平衡探测器集成芯片,其特征在于,所述平衡探测器区自下而上依次包括:n接触层,光学匹配层,第一吸收层,第二吸收层,能带过渡层,上包层,p接触层,设置于第一吸收层上的n电极,设置于p接触层之上的p电极;

7.根据权利要求1所述的inp基平衡探测器集成芯片,其特征在于,所述第一吸收层、第二吸收层和能带过渡层设置厚度与波导芯层厚度相匹配。

8.根据权利要求1所述的inp基平衡探测器集成芯片,其特征在于,所述下波导层为n掺杂的inp层,掺杂浓度为5×1017cm-3,厚度在0.6-1um;

9.一种inp基平衡探测器集成芯片的制备方法,其特征在于,包括:

10.根据权利要求9所述的inp基平衡探测器集成芯片的制备方法,其特征在于,所述制备位于所述衬底之上的多模干涉耦合波导区包括:

技术总结

本发明提供了一种InP基平衡探测器集成芯片及其制备方法,可以应用于光电子技术领域。包括:衬底;多模干涉耦合波导区,位于所述衬底之上,用于耦合信号光和本征光并实现功率均分,得到均分相干光信号;平衡探测器区,位置于所述衬底之上,用于将所述均分相干光信号转化为电信号;其中,所述多模干涉耦合波导区与所述平衡探测器区对接。采用单片集成技术,将多模干涉耦合波导和平衡探测器对接,能够提高光吸收耦合效率。

技术研发人员:郑煜,韩勤,叶焓,王帅,耿立妍,褚艺渺,肖帆

受保护的技术使用者:中国科学院半导体研究所

技术研发日:

技术公布日:2024/1/15

- 还没有人留言评论。精彩留言会获得点赞!