一种提高MCU存储性能的MCU芯片及方法与流程

本发明涉及mcu芯片相关领域,具体为一种提高mcu存储性能的mcu芯片及方法。

背景技术:

1、mcu,中文为微控制单元,又称单片微型计算机或者单片机,是指将计算机的cpu、ram、rom、定时计数器和多种i/o接口集成在一片芯片上,形成芯片级的计算机。mcu的好处是可以为不同的应用场合做不同组合控制,其设备常见的有h3c的mg 9000系列和me8000系列;

2、例如公开号为cn206149596u的授权专利(芯片板及适用于该芯片板的插座):包括一体成型的顶层打线板、中层打线板和底层打线板,顶层打线板位于中层打线板上表面的中部,底层打线板位于中层打线板下表面的一侧边缘;主控芯片区位于顶层打线板上表面的中部;金手指区对称位于底层打线板的两侧;根据金手指的结构相应更改插座的设计,将原来的纵向插入的针脚改为横向弹性设计。本发明通过将pcb板设置成不同层级避免了相互交叉打线时易造成短路的问题;将芯片板上的pin针设计成金手指结构,避免焊接pin针的繁琐工作,将垂直的上下插拔方式改为从侧面滑动插入的方式,解决插拔困难问题以及减小插拔方式对芯片板的损伤;

3、上述现有技术的芯片板无法叠加组装副芯片,使其对于数据的存储能力不变,无法根据存储需求进行提高存储能力,且芯片板采用全封闭的封装方式,此种方式如果芯片内部元件损坏,维修较为麻烦,需要对其外部结构进行破坏,影响其再次使用。

技术实现思路

1、本发明的目的在于提供一种提高mcu存储性能的mcu芯片及方法,以解决上述背景技术中提出的芯片板无法叠加组装副芯片,使其对于数据的存储能力不变,无法根据存储需求进行提高存储能力,且芯片板采用全封闭的封装方式,此种方式如果芯片内部元件损坏,维修较为麻烦,需要对其外部结构进行破坏,影响其再次使用的问题。

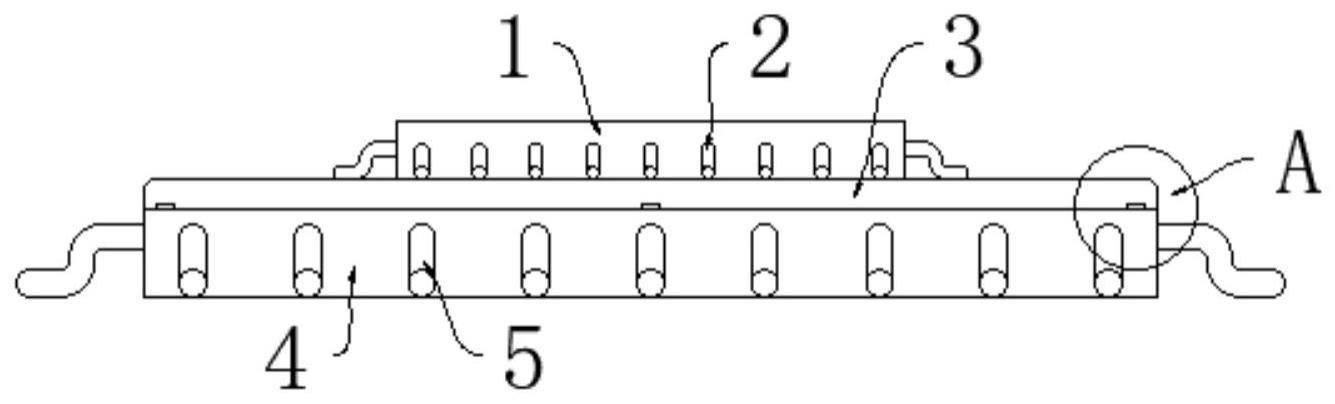

2、为实现上述目的,本发明提供如下技术方案:一种提高mcu存储性能的mcu芯片,包括副芯片和mcu芯片主体,所述mcu芯片主体的外侧设有第二引脚,所述mcu芯片主体的顶部设有芯片盖,所述芯片盖的顶部设有副芯片,所述副芯片的外侧设有第一引脚。

3、在进一步的实施例中,所述芯片盖的底部边侧设有卡槽,所述mcu芯片主体的顶端边侧设有凸槽,且凸槽与卡槽镶嵌组装。

4、在进一步的实施例中,所述mcu芯片主体设为方形结构,所述副芯片设为圆形结构。

5、在进一步的实施例中,所述芯片盖的顶端中部设有安装槽,所述安装槽上设有销孔。

6、在进一步的实施例中,所述副芯片的底部设有插销,且插销与销孔镶嵌组装。

7、在进一步的实施例中,所述副芯片与mcu芯片主体组装后设为一体结构,其内部存储模块互通。

8、还包括处理器、数据缓冲模块、片内非易失性存储器以及预取控制器,所述处理器与数据缓冲模块连接,数据缓冲模块与片内非易失性存储器连接,所述数据缓冲模块还与预取控制器连接;所述处理器用于执行片内非易失性存储器中读取的指令;所述数据缓冲模块用于缓存非易失性存储器读出的指令,供处理器读取;片内非易失性存储器,用于存储指令;预取控制器用于实现片内非易失性存储器数据预取和处理器指令读取。

9、一种提高mcu存储性能的mcu芯片的方法,包括以下步骤:

10、s1:将芯片盖的底端卡槽与mcu芯片主体的顶部边侧的,将副芯片通过其底端的插销与芯片盖顶端中部的安装槽上的销孔镶嵌组装,使副芯片与mcu芯片主体接通,使两者对于数据的存储可以连通;

11、s2:通过第二引脚用以引流,通过副芯片外侧的第一引脚用以引流,通过芯片盖对mcu芯片主体的顶部进行安全组装,通过副芯片辅助mcu芯片主体使用;

12、s3:在预取控制器中,通过片内非易失性存储器和cpu数据位宽的比例关系,以及程序指令存储地址多为连续的特点;从片内非易失性存储器中一次读取n个m比特指令放入其中一个数据缓存中,cpu在至少n个周期内有数据读取,在此期间从片内非易失性存储器读取另一组指令放入另一个数据缓存,如此往复,形成流水结构,提高cpu从片内非易失性存储器中读取指令的速率。

13、与现有技术相比,本发明的有益效果是:

14、1、该发明设有副芯片,且副芯片的底部设有插销,在mcu芯片主体的顶部设有芯片盖,通过芯片盖可以将mcu芯片主体进行拆分,使其可以在后期维修过程直接拆分,方便芯片元件的更换和检查。

15、2、该发明的芯片盖顶端中部设有安装槽,在安装槽的中部设有多个销孔,通过销孔可以与副芯片底部的插销镶嵌,使其方便副芯片的组装,通过副芯片可以提高mcu芯片主体的存储能力。

技术特征:

1.一种提高mcu存储性能的mcu芯片,包括副芯片(1)和mcu芯片主体(4),其特征在于:所述mcu芯片主体(4)的外侧设有第二引脚(5),所述mcu芯片主体(4)的顶部设有芯片盖(3),所述芯片盖(3)的顶部设有副芯片(1),所述副芯片(1)的外侧设有第一引脚(2)。

2.根据权利要求1所述的一种提高mcu存储性能的mcu芯片及方法,其特征在于:所述芯片盖(3)的底部边侧设有卡槽(8),所述mcu芯片主体(4)的顶端边侧设有凸槽(9),且凸槽(9)与卡槽(8)镶嵌组装。

3.根据权利要求1所述的一种提高mcu存储性能的mcu芯片,其特征在于:所述mcu芯片主体(4)设为方形结构,所述副芯片(1)设为圆形结构。

4.根据权利要求1所述的一种提高mcu存储性能的mcu芯片,其特征在于:所述芯片盖(3)的顶端中部设有安装槽(6),所述安装槽(6)上设有销孔(7)。

5.根据权利要求1所述的一种提高mcu存储性能的mcu芯片,其特征在于:所述副芯片(1)的底部设有插销(10),且插销(10)与销孔(7)镶嵌组装。

6.根据权利要求1所述的一种提高mcu存储性能的mcu芯片,其特征在于:所述副芯片(1)与mcu芯片主体(4)组装后设为一体结构,其内部存储模块互通。

7.根据权利要求1所述的一种提高mcu存储性能的mcu芯片,其特征在于:还包括处理器、数据缓冲模块、片内非易失性存储器以及预取控制器,所述处理器与数据缓冲模块连接,数据缓冲模块与片内非易失性存储器连接,所述数据缓冲模块还与预取控制器连接;所述处理器用于执行片内非易失性存储器中读取的指令;所述数据缓冲模块用于缓存非易失性存储器读出的指令,供处理器读取;片内非易失性存储器,用于存储指令;预取控制器用于实现片内非易失性存储器数据预取和处理器指令读取。

8.根据权利要求7所述的一种提高mcu存储性能的mcu芯片的方法,其特征在于:包括以下步骤:

技术总结

本发明公开了一种提高MCU存储性能的MCU芯片及方法,包括副芯片和MCU芯片主体,所述MCU芯片主体的外侧设有第二引脚,所述MCU芯片主体的顶部设有芯片盖,所述芯片盖的顶部设有副芯片,所述副芯片的外侧设有第一引脚,所述芯片盖的底部边侧设有卡槽,所述MCU芯片主体的顶端边侧设有凸槽。该发明设有副芯片,且副芯片的底部设有插销,在MCU芯片主体的顶部设有芯片盖,通过芯片盖可以将MCU芯片主体进行拆分,使其可以在后期维修过程直接拆分,方便芯片元件的更换和检查;芯片盖顶端中部设有安装槽,在安装槽的中部设有多个销孔,通过销孔可以与副芯片底部的插销镶嵌,使其方便副芯片的组装,通过副芯片可以提高MCU芯片主体的存储能力。

技术研发人员:祝苏明

受保护的技术使用者:江苏新安电器股份有限公司

技术研发日:

技术公布日:2024/1/16

- 还没有人留言评论。精彩留言会获得点赞!