封装结构及其形成方法与流程

本技术涉及封装领域,尤其涉及一种封装结构及其形成方法。

背景技术:

1、现在电子设备正在迅速地向高集成度、高组装密度、高运行速度方向发展,半导体芯片作为电子设备的核心,由于其集成度、封装密度以及工作时钟频率不断提高,而体积却不断缩小,因此,半导体芯片单位面积的发热量不断增加,尤其对于大功率电子设备而言情况更为严重。

2、目前针对半导体芯片具有多种散热方案,其中一种比较常见的方案为通过半导体制控温装置(或半导体制冷器,tec)对半导体芯片进行散热。采用半导体制控温装置对半导体芯片进行散热时,通常是将半导体制控温装置贴装在半导体芯片上方的散热盖表面上,且所述散热盖与所述半导体芯片之间以及所述散热盖与所述半导体制控温装置之间需要形成热界面材料以传导热量,这种散热方案使得封装结构的厚度增大,热量通过两层热界面材料和散热盖传导到半导体制控温装置释放时,热传导的路径较长散热效率较差,并且由于半导体制控温装置为单独的结构,因而需要为半导体制控温装置设置额外的接口以连接外部的电源,极不方便和灵活。

技术实现思路

1、本技术一些实施例提供了一种封装结构,包括:

2、提供基板;

3、提供半导体制控温装置,所述半导体制控温装置包括相对的第一表面和第二表面,所述第一表面上具有凸起的第一柱状电极和第二柱状电极;

4、将所述半导体制控温装置的第二表面贴装在所述基板的上表面上;

5、提供半导体芯片,所述半导体芯片包括相对的背面和功能面,所述功能面上具有外接端子;

6、将所述半导体芯片的背面贴装在半导体制控温装置的第一表面上;

7、在所述基板的上表面上形成包覆所述半导体芯片和半导体制控温装置的塑封层,所述塑封层暴露出所述第一柱状电极、第二柱状电极和外接端子的顶部表面;

8、在所述塑封层上形成与所述第一柱状电极电连接的第一外接凸起,与所述第二柱状电极电连接的第二外接凸起,以及与所述外接端子电连接的第三外接凸起。

9、在一些实施例中,第一外接凸起和第二外接凸起用于与直流电源的正极和负极电连接,以使得所述半导体制控温装置工作以吸收所述半导体芯片产生的热量,所述半导体制控温装置在工作时会形成冷端和热端,所述冷端为靠近所述第一表面的一端,所述热端为靠近所述第二表面的一端。

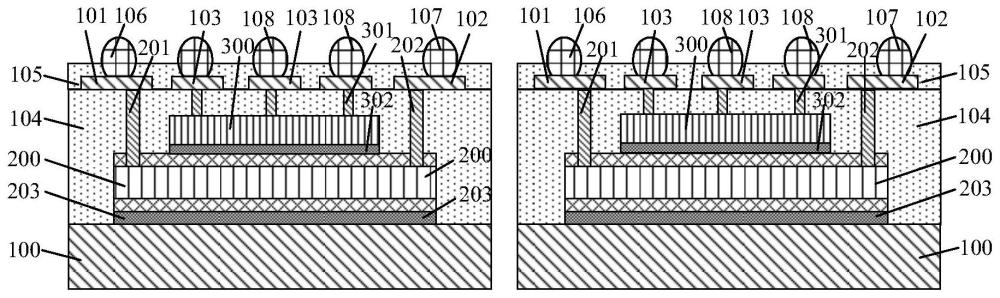

10、在一些实施例中,所述半导体制控温装置包括交错排布并串联的多个n型半导体和p型半导体,位于所述多个n型半导体和p型半导体顶部表面上的顶层陶瓷基板,位于所述多个n型半导体和p型半导体底部表面的底层陶瓷基板,所述第一柱状电极和第二柱状电极凸起于所述顶层陶瓷基板表面上,并与所述串联的多个n型半导体和p型半导体的两端的一个n型半导体和p型半导体电连接。

11、在一些实施例中,所述半导体芯片的背面通过导热胶贴装在半导体制控温装置的顶层陶瓷基板表面上。

12、在一些实施例中,所述半导体芯片贴装在第一柱状电极和第二柱状电极之间的半导体制控温装置的上表面上,或者贴装在第一柱状电极和第二柱状电极一侧的半导体制控温装置的上表面上。

13、在一些实施例中,所述半导体芯片的背面贴装在半导体制控温装置的上表面上后,所述半导体芯片的功能面上的外接端子的顶部表面与所述半导体制控温装置的第一表面上凸起的第一柱状电极和第二柱状电极的顶部表面齐平。

14、在一些实施例中,还包括:在所述塑封层上形成与所述第一柱状电极电连接的第一再布线层,与所述第二柱状电极电连接的第二再布线层,与所述外接端子电连接的第三再布线层;所述第一外接凸起位于所述第一再布线层上并与所述第一再布线层电连接,所述第二外接凸起位于所述第二再布线层上并与所述第二再布线层电连接,所述第三外接凸起位于所述第三再布线层上并与所述第三再布线层电连接。

15、在一些实施例中,所述基板包括多个阵列排布的封装区域和位于相邻封装区域之间的切割道区域;在每一个所述封装区域的上表面上相应的贴装所述半导体制控温装置和半导体芯片;所述塑封层还覆盖所述基板的切割道区域的上表面;形成所述第一外接凸起、第二外接凸起和第三外接凸起后,沿切割道区域切割所述塑封层和基板,形成若干分立的封装体。

16、本技术另一些实施例还提供了一种封装结构,包括:

17、基板;

18、半导体制控温装置,所述半导体制控温装置包括相对的第一表面和第二表面,所述第一表面上具有凸起的第一柱状电极和第二柱状电极;

19、所述半导体制控温装置的第二表面贴装在所述基板的上表面上;

20、半导体芯片,所述半导体芯片包括相对的背面和功能面,所述功能面上具有外接端子;

21、所述半导体芯片的背面贴装在半导体制控温装置的第一表面上;

22、位于所述基板的上表面上包覆所述半导体芯片和半导体制控温装置的塑封层,所述塑封层暴露出所述第一柱状电极、第二柱状电极和外接端子的顶部表面;

23、位于所述塑封层上与所述第一柱状电极电连接的第一外接凸起,与所述第二柱状电极电连接的第二外接凸起,以及与所述外接端子电连接的第三外接凸起。

24、在一些实施例中,第一外接凸起和第二外接凸起用于与直流电源的正极和负极电连接,以使得所述半导体制控温装置工作以吸收所述半导体芯片产生的热量,所述半导体制控温装置在工作时会形成冷端和热端,所述冷端为靠近所述第一表面的一端,所述热端为靠近所述第二表面的一端。

25、在一些实施例中,所述半导体制控温装置包括交错排布并串联的多个n型半导体和p型半导体,位于所述多个n型半导体和p型半导体顶部表面上的顶层陶瓷基板,位于所述多个n型半导体和p型半导体底部表面的底层陶瓷基板,所述第一柱状电极和第二柱状电极凸起于所述顶层陶瓷基板表面上,并与所述串联的多个n型半导体和p型半导体的两端的一个n型半导体和p型半导体电连接。

26、在一些实施例中,所述半导体芯片的背面通过导热胶贴装在半导体制控温装置的顶层陶瓷基板表面上。

27、在一些实施例中,所述半导体芯片贴装在第一柱状电极和第二柱状电极之间的半导体制控温装置的上表面上,或者贴装在第一柱状电极和第二柱状电极一侧的半导体制控温装置的上表面上。

28、在一些实施例中,所述半导体芯片的功能面上的外接端子的顶部表面与所述半导体制控温装置的第一表面上凸起的第一柱状电极和第二柱状电极的顶部表面齐平。

29、在一些实施例中,还包括:位于所述塑封层上与所述第一柱状电极电连接的第一再布线层,与所述第二柱状电极电连接的第二再布线层,与所述外接端子电连接的第三再布线层;所述第一外接凸起位于所述第一再布线层上并与所述第一再布线层电连接,所述第二外接凸起位于所述第二再布线层上并与所述第二再布线层电连接,所述第三外接凸起位于所述第三再布线层上并与所述第三再布线层电连接。

30、在一些实施例中,所述外接端子为凸起于半导体芯片的功能面上的金属柱或者为位于所述半导体芯片的功能面的外接焊盘。

31、本技术前述一些实施例中的封装结构及其形成方法,所述形成方法,包括:提供基板;提供半导体制控温装置,所述半导体制控温装置包括相对的第一表面和第二表面,所述第一表面上具有凸起的第一柱状电极和第二柱状电极;将所述半导体制控温装置的第二表面贴装在所述基板的上表面上;提供半导体芯片,所述半导体芯片包括相对的背面和功能面,所述功能面上具有外接端子;将所述半导体芯片的背面贴装在半导体制控温装置的第一表面上;在所述基板的上表面上形成包覆所述半导体芯片和半导体制控温装置的塑封层,所述塑封层暴露出所述第一柱状电极、第二柱状电极和外接端子的顶部表面;在所述塑封层上形成与所述第一柱状电极电连接的第一外接凸起,与所述第二柱状电极电连接的第二外接凸起,以及与所述外接端子电连接的第三外接凸起。由于所述半导体制控温装置的第一柱状电极和第二柱状电极凸起于所述第一表面上,因而可以将半导体芯片贴装在第一柱状电极和第二柱状电极之间或一侧的半导体制控温装置的第一表面上,并且,由于基板的厚度可以较薄,所述半导体制控温装置与半导体芯片之间不会设置散热盖且只需要一层热界面材料(导热胶),从而减小形成的封装结构的厚度,并且使得半导体芯片到半导体制控温装置之间的热传输距离变短,因而半导体芯片产生的热量可以快速的传递到半导体制控温装置进行释放,提高对半导体芯片的散热性能,同时在所述基板的上表面上形成包覆所述半导体芯片和半导体制控温装置的塑封层,所述塑封层暴露出所述第一柱状电极、第二柱状电极和外接端子的顶部表面后,方便第一外接凸起、第二外接凸起和第三外接凸起的集成制作,且通过第一外接凸起、第二外接凸起、第一柱状电极和第二柱状电极作为端口可以使得半导体制控温装置与直流电源的正极和负极电连接,从而使得半导体制控温装置无需在额外设置与直流电源连接的端口,提高了方便性和灵活性。

- 还没有人留言评论。精彩留言会获得点赞!