功率芯片及其封装方法与流程

本公开涉及半导体,特别是涉及一种功率芯片及其封装方法。

背景技术:

1、氮化镓(gan)作为第三代半导体材料的典型代表,具有禁带宽度大、击穿电场强、电子迁移率高、导热率高,导通电阻低等优点,是制备高温、高压、射频、功率领域器件的理想材料。氮化铝镓(algan)和氮化镓(gan)异质结构由于具有显著的自发极化效应,能够在界面处形成高浓度的二维电子气。

2、目前,基于氮化铝镓/氮化镓异质结形成的二维电子气制备的高电子迁移率晶体管(high electron mobility transistor,简称hemt)在射频和功率领域应用前景广阔,是电力电子、无线通信和雷达等领域的核心器件。

3、然而,随着半导体器件集成度的提高,氮化镓基功率芯片的功率密度显著提升。由于氮化镓hemt器件具有明显的自热效应,导致器件栅极沟道处的温度显著升高,从而降低器件的可靠性,严重时可能会造成器件失效,影响其使用寿命,阻碍了氮化镓器件在功率和射频领域的应用。

技术实现思路

1、基于此,本公开实施例提供了一种功率芯片及其封装方法,以有效提升功率芯片的散热效率。

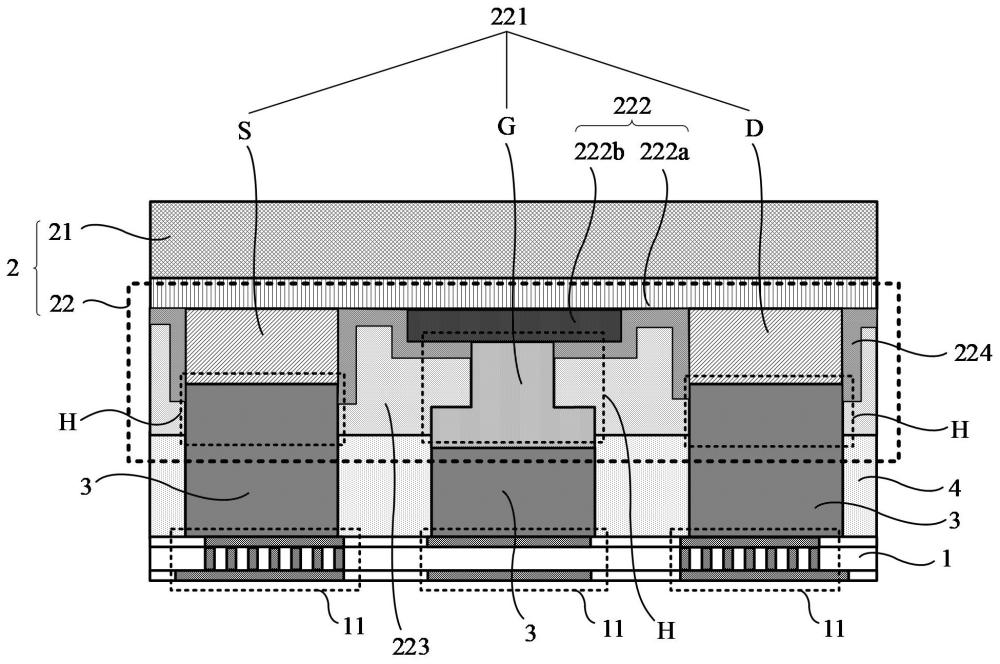

2、为了实现上述目的,一方面,本公开一些实施例提供了一种功率芯片。功率芯片包括:基板,设有导电结构。一个或多个子芯片,子芯片靠近基板的一侧设有多个电极。多个导电柱,分别设置于对应电极的表面,并与导电结构电性连接;其中,导电柱复用为散热柱。

3、在一些实施例中,子芯片包括:外延层,各电极设置于外延层靠近基板的表面。钝化层,覆盖于外延层靠近基板的表面并具有多个开口,开口暴露出对应的电极;其中,至少部分导电柱的一端位于开口内并与电极电性连接;钝化层的导热率大于或等于200w/m·k。

4、在一些实施例中,钝化层包括金刚石层。

5、在一些实施例中,子芯片还包括:钝化保护层,设置于钝化层靠近外延层的表面;其中,钝化层中的开口还延伸贯穿钝化保护层。

6、在一些实施例中,导电柱在基板上的正投影与对应相连的电极在基板上的正投影大致重叠。

7、在一些实施例中,多个电极包括栅极、源极和漏极;其中,导电柱、栅极、源极和漏极的材料均为金属。

8、在一些实施例中,相邻导电柱之间具有间隔。功率芯片还包括:绝缘填充层,填充于任相邻导电柱之间的间隔内。

9、在一些实施例中,子芯片包括衬底及设置于衬底靠近基板一侧的晶体管;多个电极包括晶体管的栅极、源极和漏极;其中,衬底的厚度的取值范围包括50μm~1500μm。

10、另一方面,本公开还根据一些实施例,提供一种功率芯片的封装方法,包括如下步骤。

11、制备一个或多个子芯片,子芯片的一侧形成有多个电极。

12、于各电极的表面分别形成导电柱,导电柱复用为散热柱。

13、提供基板,基板上形成有导电结构。

14、将各导电柱与导电结构电性连接。

15、在一些实施例中,子芯片包括衬底及设置于衬底靠近基板一侧的外延层;各电极设置于外延层靠近基板的表面,包括栅极、源极和漏极。其中,制备一个或多个子芯片,包括如下步骤。

16、提供衬底,于衬底上依次形成外延层及位于外延层背离衬底一侧的源极和漏极。

17、形成覆盖外延层及源极、漏极的钝化层,钝化层的导热率大于或等于200w/m·k。

18、于钝化层中形成多个开口,多个开口分别暴露出源极、漏极以及位于源极和漏极之间的部分外延层。

19、于暴露出外延层的开口内形成栅极。

20、其中,于各电极的表面分别形成导电柱,包括如下步骤:于暴露出源极和漏极的开口内以及栅极背离外延层的表面,分别形成导电柱。

21、本公开实施例可以/至少具有以下优点:

22、本公开实施例中,将子芯片靠近基板一侧设有的多个电极通过多个导电柱与基板的导电结构电性连接,以形成倒装封装结构;并且,导电柱复用为散热柱,这样不仅缩短了各子芯片与基板上导电结构的互连路径和散热传导路径,还能同时兼顾了各子芯片与基板上导电结构之间的电气互连和散热功能,使各子芯片内部产生的热量可以通过散热柱(即导电柱)直接传导至基板处进行散热。由此,本公开实施例提供的功率芯片,其整体封装热阻较小,散热效率高,在满足自身散热需求的同时,对衬底的厚度及热导率的要求低,从而有利于延长功率芯片的使用寿命,提高功率芯片的性能及可靠性,进而促进半导体功率芯片的进一步发展。

23、本公开的一个或多个实施例的细节在下面的附图和描述中提出。本公开的其他特征、目的和优点将从说明书、附图以及权利要求书变得明显。

技术特征:

1.一种功率芯片,其特征在于,包括:

2.根据权利要求1所述的功率芯片,其特征在于,所述子芯片包括:

3.根据权利要求2所述的功率芯片,其特征在于,所述钝化层包括金刚石层。

4.根据权利要求2所述的功率芯片,其特征在于,所述子芯片还包括:

5.根据权利要求1~4中任一项所述的功率芯片,其特征在于,所述导电柱在所述基板上的正投影与对应相连的所述电极在所述基板上的正投影大致重叠。

6.根据权利要求1~4中任一项所述的功率芯片,其特征在于,多个所述电极包括栅极、源极和漏极;

7.根据权利要求1~4中任一项所述的功率芯片,其特征在于,相邻所述导电柱之间具有间隔;所述功率芯片还包括:

8.根据权利要求1~4中任一项所述的功率芯片,其特征在于,所述子芯片包括衬底及设置于所述衬底靠近所述基板一侧的晶体管;多个所述电极包括所述晶体管的栅极、源极和漏极;

9.一种功率芯片的封装方法,其特征在于,包括:

10.根据权利要求9所述的功率芯片的封装方法,其特征在于,所述子芯片包括衬底及设置于所述衬底靠近所述基板一侧的外延层;各所述电极设置于所述外延层靠近所述基板的表面,包括栅极、源极和漏极;

技术总结

本公开涉及一种功率芯片及其封装方法。该功率芯片,包括:基板、一个或多个子芯片以及多个导电柱。基板设有导电结构。子芯片靠近基板的一侧设有多个电极。多个导电柱分别设置于对应电极的表面,并与导电结构电性连接;其中,导电柱复用为散热柱。本公开利于缩短功率芯片中的散热传导路径、降低热阻并提高散热效率。

技术研发人员:童富,陈少俭,杨琳

受保护的技术使用者:苏州华太电子技术股份有限公司

技术研发日:

技术公布日:2024/1/15

- 还没有人留言评论。精彩留言会获得点赞!